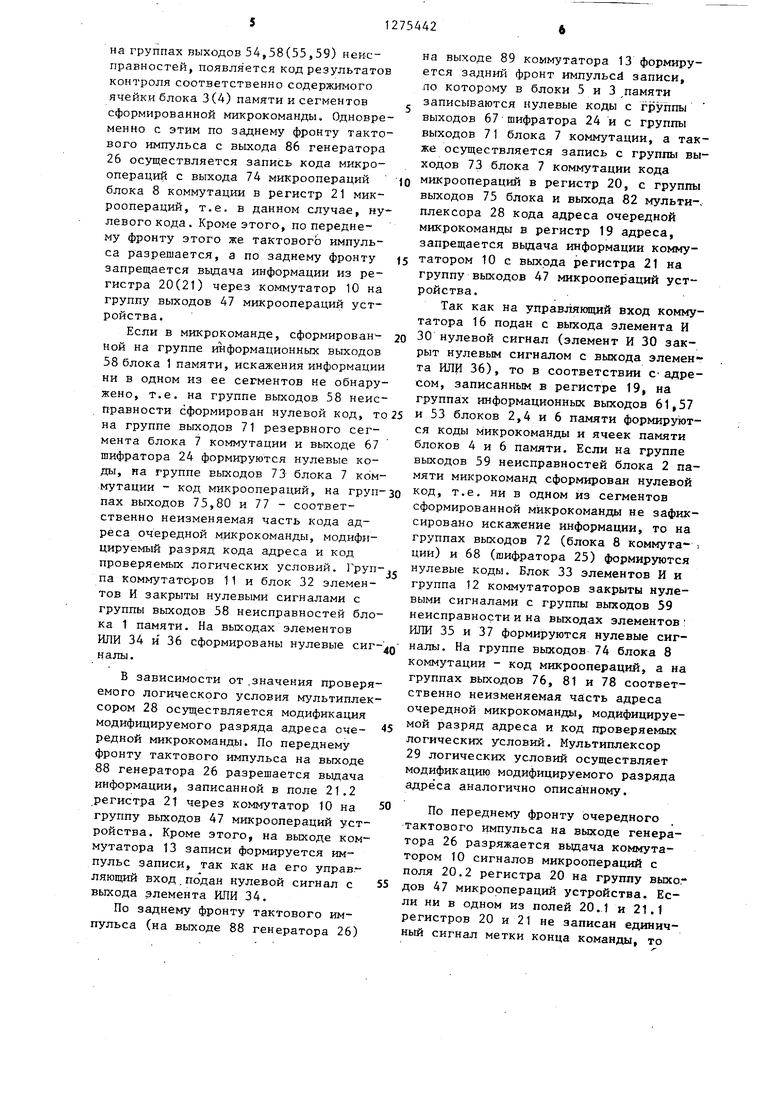

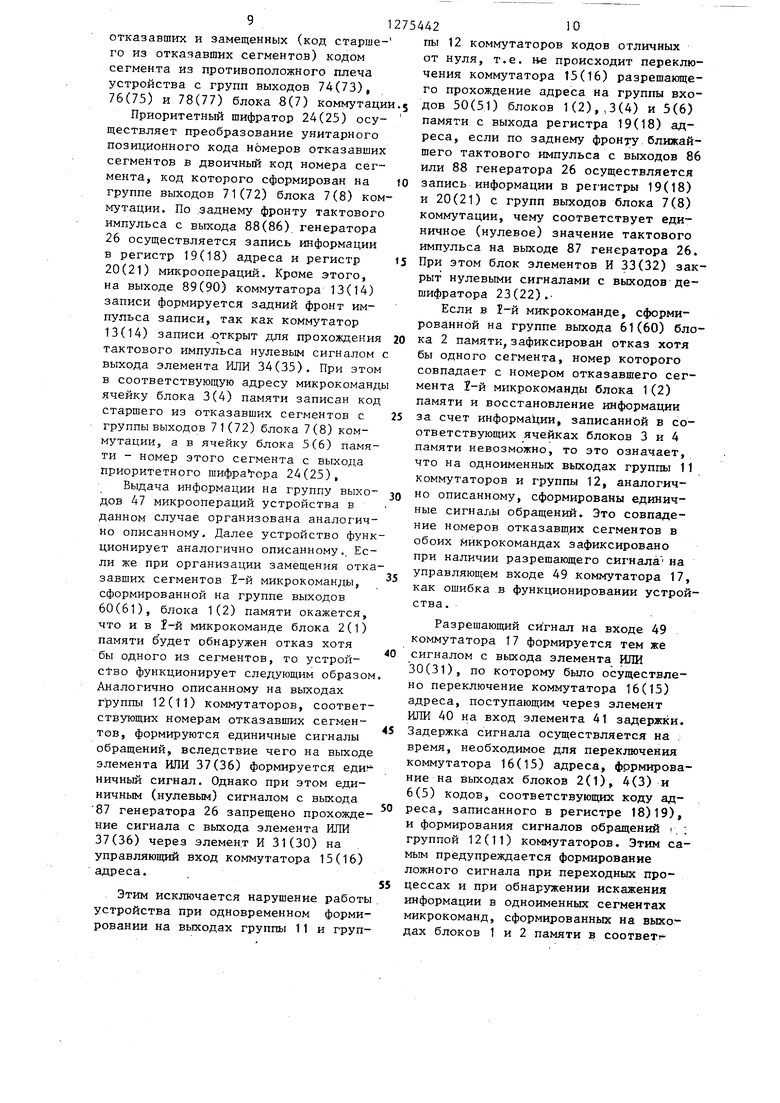

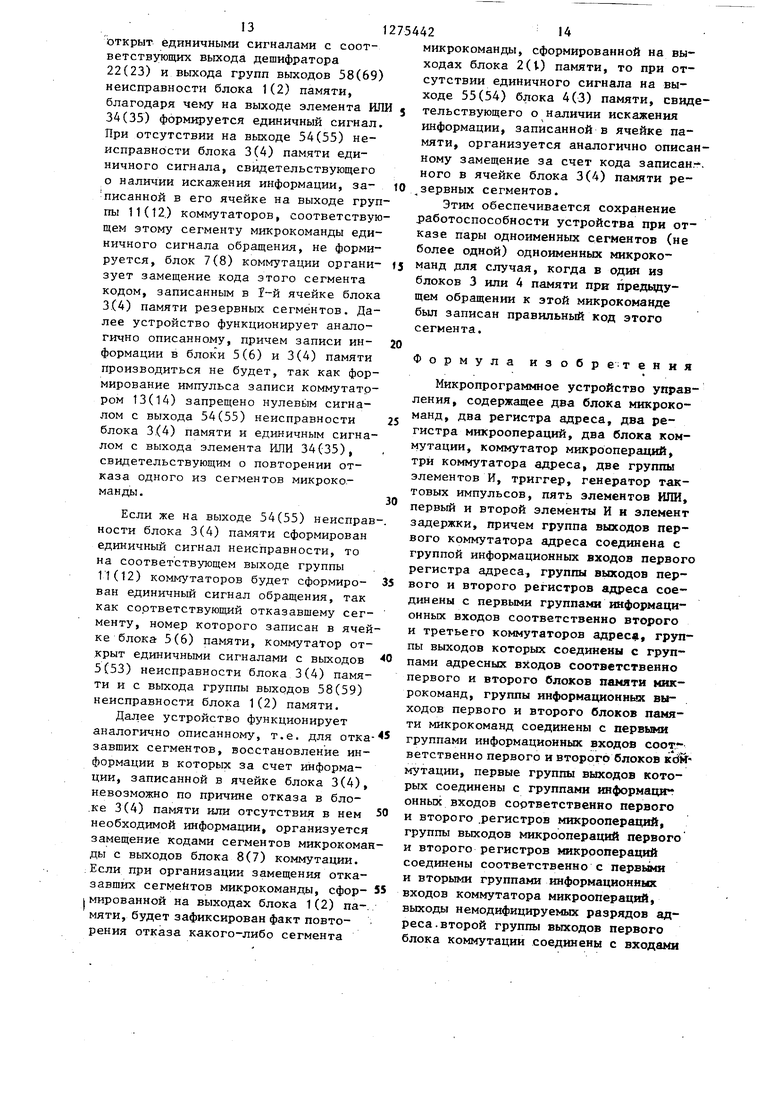

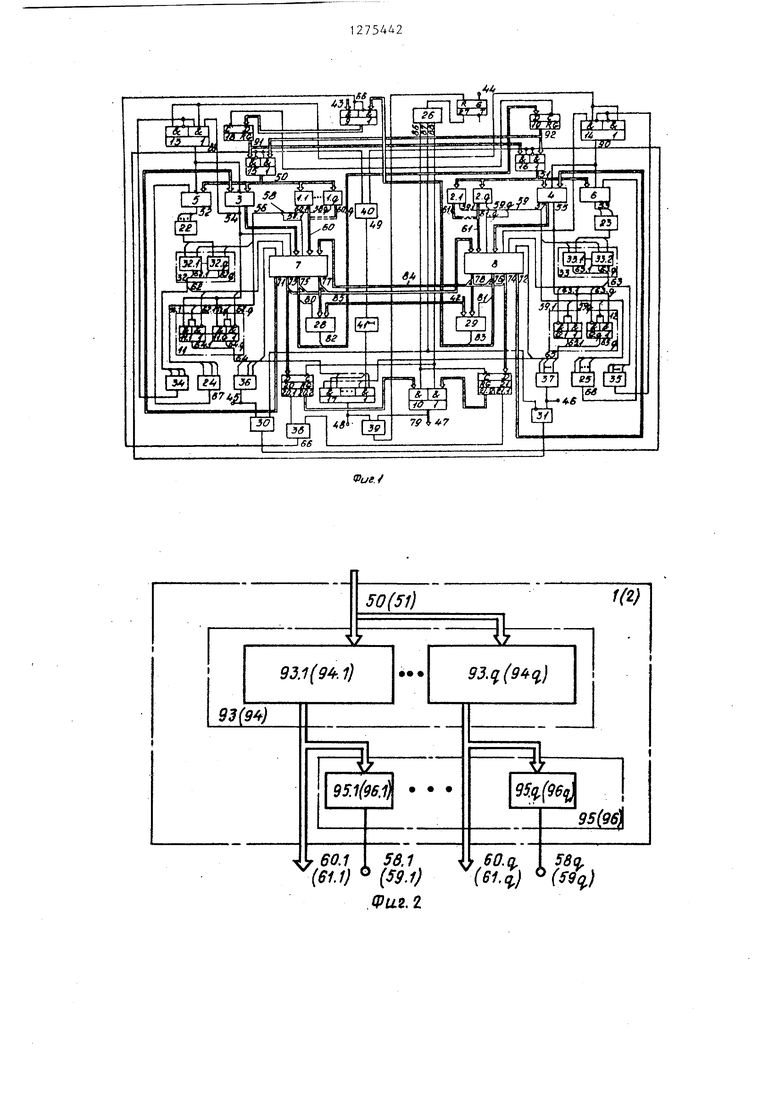

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управле ния цифровых вычислительных машин с повышенной надежностью. Цель изобретения - повышение отказоустойчивости устройства за счет повышения устойчивости устройства к сбоям и отказам в ячейках блоков памяти микрокоманд. Цель достигается за счет использо вания идентичных блоков памяти, в ко торых по одним и тем же адресам записаны одинаковые микрокоманды, причем каждый из блоков памяти разбит на q независимых секций, благодаря чему каждая микрокоманда разделяется на q сегментов, каждый из которых подвергается контролю; организации записи в соответствующую ячейку соот ветствующего блока памяти резервных сегментов кода, которым было осущест влено замещение одного из сегментов микрокоманды, в котором бьшо обнаружено искажение информации (отказ) сегмента; использования информации, записанной в сегменте, микрокоманды, которой был забракован при последнем (после установки устройства в исходное состояние) обращении к этой микрокоманде, при условии, что при данном обращении к ней искажения в этом сегменте не обнаружено; организации смены информации, записанной в 1-й ячейке блока памяти резервных сегмен тов при несоответствии номера сегмента, код которого записан в ней, ни одному из номеров сегментов 1-й микрокоманды, в которых при данном обращении к ней зафиксировано искажение информации; организации перезаписи информации в 1-й ячейке блока памяти резервных сегментов при обнаружении в ней искажений-информации; обеспечения на этой основе восстановления работоспособности устройства при наличии искажения в j-м сегменте 1-й микрокоманды первого (второго) блока памяти микрокоманд путем его замещения: кодом сегмента, записанным в Е-й ячейке соответствующего первого (второго) блока памяти резервных сегментов прИ|01;сутствии факта обнаружения искажений информации в ней и соответствии его номера i-номеру j-сегмента, в котором обнаружено искажение информации для всех j i, где ,qиj 1,q, а также ко422дом соответствующего j-ro сегмента 1-й микрокоманды второго (первого) блока памяти микрокоманд, а при обнаружении искажения информации в нем кодом i-ro сегмента, записанным в 2-й ячейке соответствующего этому блоку памяти микрокоманд второго (первого) блока памяти резервных сегментов при условии, что i j и отсутствии в ней искажения информации. Это позволяет существенно расширить множество неисправностей, при которых устройство сохраняет свою работоспособность. На фиг.1 представлена фзшкциональная схема устройства; на фиг. 2 функциональная схема блока памяти микрокоманд; на фиг.3 - функциональная схема блока памяти резервного сегмента; на фиг.4 - функциональная схема блока коммутации; на фиг.5 временная диаграмма работы устройства. Устройство (фиг.1) содержит первый 1 и второй 2 блоки памяти микрокоманд, первый 3 и второй 4 блоки памяти резервных сегментов, первый 5 и второй 6 блоки памяти номеров отказавших сегментов, первый 7 и второй 8 блоки коммутации, первый коммутатор 9 адреса, коммутатор 10 микроопераций, первая 11 и вторая 12 группы коммутаторов обращений, второй 13 и первый 14 коммутаторы записи, второй 15 и третий 16 коммутаторы адреса. коммутатор 17 ошибки, первый 18 и второй 19 регистры адреса, первый 20 и второй 21 регистры микроопераций с полями 20.1 и 21,1 меток конца команды и с полями 20,2 и 21.2 микроопераций, первый 22 и второй 23 дешифраторы, первый 24 и второй 25 шифраторы, генератор 26 тактовых импульсов, триггер 27, первьц 28 и второй 29 мультиплексоры логических условий. первый 30 и второй 31 элементы И, первый 32 и второй 33 блоки элемен тов И, первьй 34, второй 35, четвертый 36, пятый 37, тестой 38, седьмой 39 и третий 40 элементы ИЛИ, элемент 41 задержки, группу входов 42 логических условий, группу входов микро- операций 43 и вход 44 пуска устройства, первьгй 45 и второй 46 выходы неисправности уса-ройства, группу выходов 47 микроопераций и выход 48 ошибки устройства, выход 49 элемента 41 задержки, группы выходов 50 и 51 соответственно второго 15 и третьего 16 коммутаторов адреса, группы инфор мационных выходов 52 и 53 соответ-. ственно первого 5 и второго 6. блоков памяти номеров отказавших сегментов, выходы 54 и 5 неисправности соответ ствекно первого 3 и второго 4 блоков памяти резервных сегментов, группы информационных выходов 56 и 57 этих блоков5 группы выходов 58 и 59 неисправностей соответственно первого 1 и второго 2 блоков памяти микрокоманд, группы информационных выходов 60 и 61 блоков 1 и 2 соответственно, группы выходов 62 и 63 первого 32 и второго 33 блоков элементов И соотве ственно, группы выходов 64 и 65 соот ветственно первой 11 и второй 12 группы коммутаторов обращений, выход 66элемента ИЛИ 38, группы выходов 67и 68 соответственно первого 24 и второго 25 приоритетных шифраторов выходы 69 и 70 соответственно первого 34 и второго 35 элементов ИЛИ, третьи 71 и 72, первые 73 и 74, вторые 75 и 76, четвертые 77 и 78 груп-пы выходов соответственно первого 7 и второго 8 блоков коммутации, выход 79метки конца работы группы выходов коммутатора 10 микроопераций, выходы 80и 81 модифицируемого разряда второй группы выходов соответственно первого 7 и второго 8 блоков коммутации, выходы 82 и 83 первого 28 и второго 29 мультиплексоров логических условий соответственно, седьмые группы входов 84 и 85 соответственно первого 7 и второго 8 блоков коммутации первый 86, третий 87 и второй 88 выходы генератора 26 тактовых импуль ов, выходы 89 и 90 соответственно второго 13 и первого 14 коммутаторов записи, выходы 91 и 92 первого 18 и второго 19 регистров адреса соответственно. Блок 1 (2) памяти микрокоманд (фиг.2) содержит группу статических запоминающих устройств 93(94), группу сумматоров 95(96) по модулю два, адресньй вход 50(51) блока, группу информационных выходов 60(61) и группу выходов 58(59) неисправностей блока. Блок 3(4) (фиг. 3) содержит оперативное запоминающее устройство 97(98) и сумматор 99(100) по модулю два. Блок 7(8) (фиг. 4) содержит образователь 101 кодов, коммутатор 102 или 103 выделения, группу 104 105, преобразокоммутаторовватель 106 кодов. На фиг,5 представлена временная диаграмма работы устройства при отсутствии отказов в сегментах микрокоманд: t , С , с, - тактовые импульсы на первом, втором и третьем выходах генератора 26 тактовых импульсов; А1 - А11 - коды адреса соответственно с первой по одиннадцатую микрокоманд Ml -Mil; КО,- K0,g - коды микроопераций; О,- O.JJ - соответствующие им сигналы микроопераций; КК - метка конца команды; КР - метка конца работы. Устройство (фиг.1) работает следующим образом. В исходном состоянии триггер 27 установлен в нулевое состояние, в регистрах 18 и 19 адреса, в ячейках .. , блоков 3-6 памяти записаны нулевые коды на группах информационных выходов блоков 1 - 6 сформированы нулевые коды, в полях 20.1 и 21.1 регистров 20 и 21 микроопераций соответственно записаны единичные сигналы меток конца команды, Ь полях 20.2 и 21.2 записаны нулевые коды (цепи установки в исходное состояние не показаны) . По единичному сигналу, поступающему на вход 44 пуска устройства, триггер 27 устанавливается в единичное состояние. По сигналу с единичного выхода триггера 27 запускается генератор 26 тактовых импульсов. По заднему фронту тактового импульса на выходе 86 генератора 26 в регистр 18 адреса осуществляется запись кода адреса микрокоманды, поступающего с группы адресных входов 43 устройства, так как коммутатор 9 адреса открыт для прохождения информации с группы входов 43 устройства единичными сигналами меток конца команды, поступающими с выходов полей 20.1 и 21.1 регистров 20 и 21 через элемент ИЛИ 33 на управляющий вход коммутатора 9. Код адреса с группы выходов 91 регистра 18 через коммутатор 15 адеса поступает на группу адресных ходов блоков 1, 3 и 5 памяти. Комутатор 15 адреса открыт нулевым, сигалом с выхода элемента И 31. В соотетствии с этим адресом на группах нформационных выходов блоков 1,3 и памяти формируются коды, записанные соответствующих ячейках памяти и

на группах выходов 54,58(55,59) неисправностей, появляется код результатов контроля соответственно содержимого ячейки блока 3 (4) памяти и сегментов сформированной микрокоманды. Одновременно с этим по заднему фронту тактового импульса с выхода 86 генератора 26 осуществляется запись кода микроопераций с выхода 74 микроопераций блока 8 коммутации в регистр 21 микроопераций, т.е. в данном случае, нулевого кода. Кроме этого, по переднему фронту этого же тактового импульса разрешается, а по заднему фронту запрещается выдача информации из регистра 20(21) через коммутатор 10 на группу выходов 47 микроопераций устройства.

Если в микрокоманде, сформирован ной на группе информационных выходов 58 блока 1 памяти, искажения информации ни в одном из ее сегментов не обнаружено, т.е. на группе выходов 58 неисправности сформирован нулевой код, то на группе выходов 71 резервного сегмента блока 7 коммутации и выходе 67 шифратора 24 формируются нулевые коды, на группе вькодов 73 блока 7 коммутации - код микроопераций, на группах выходов 75,80 и 77 - соответственно неизменяемая часть кода адреса очередной микрокоманды, модифицируемый разряд кода адреса и код проверяемых логических условий. Группа коммутаторов 11 и блок 32 элементов И закрыты нулевыми сигналами с группы выходов 58 неисправностей блока 1 памяти. На выходах элементов ИЛИ 34 и 36 сформированы нулевые сигналы.

В зависимости от .значения проверяемого логического условия мультиплексором 28 осуществляется модификация модифицируемого разряда адреса очередной микрокоманды. По переднему фронту тактового импульса на выходе 88 генератора 26 разрешается вьщача информации, записанной в поле 21.2 регистра 21 через коммутатор 10 на группу выходов 47 микроопераций устройства. Кроме этого, на выходе коммутатора 13 записи формируется импульс записи, так как на его управ.ляющий вход.Подан нулевой сигнал с выхода элемента ИЛИ 34.

По заднему фронту тактового импульса (на выходе 88 генератора 26)

на выходе 89 коммутатора 13 формируется задний фронт импульсй записи, по которому в блоки 5 и 3 памяти записываются нулевые коды с группы выходов 67 шифратора 24 и с группы выходов 71 блока 7 коммутации, а также осуществляется запись с группы выходов 73 блока 7 коммутации кода микроопераций в регистр 20, с группы вьпсодов 75 блока и выхода 82 мультиплексора 28 кода адреса очередной микрокоманды в регистр 19 адреса, запрещается выдача информации коммутатором 10 с выхода регистра 21 на группу выходов 47 микроопераций устройства.

Так как на управляющий вход коммутатора 16 подан с выхода элемента И 30 нулевой сигнал (элемент И 30 закрыт нулевым сигналом с выхода элемента ИЛИ 36), то в соответствии садресом, записанным в регистре 19, на группах информационных выходов 61,57 и 53 блоков 2,4 и 6 памяти формируются коды микрокоманды и ячеек памяти блоков 4 и 6 памяти. Если на группе выходов 59 неисправностей блока 2 памяти микрокоманд сформирован нулевой код, т.е. ни в одном из сегментов сформированной микрокоманды не зафиксировано искажение информации, то на группах выходов 72 (блока 8 коммутации) и 68 (шифратора 25) формируются нулевые коды. Блок 33 элементов И и группа 12 коммутаторов закрыты нулевыми сигналами с группы выходов 59 неисправности и на выходах элементов: ИЛИ 35 и 37 формируются нулевые сигналы. На группе выходов 74 блока 8 коммутации - код микроопераций, а на группах выходов 76, 81 и 78 соответственно неизменяемая часть адреса очередной микрокоманды, модифицируемой разряд адреса и код проверяемых логических условий. Мультиплексор 29 логических условий осуществляет модификацию модифицируемого разряда адреса аналогично описанному.

По переднему фронту очередного тактового импульса на выходе генератора 26 разряжается выдача коммутатором 10 сигналов микроопераций с поля 20.2 регистра 20 на группу выхо,дов 47 микроопераций устройства. Если ни в одном из полей 20..1 и 21.1 регистров 20 и 21 не записан единичный сигнал метки конца команды, то нулевым сигналом с выхода, элемента ИЛИ 38 будет разрешено прохождение через коммутатор 9 кода адреса с вы хода 83 мультиплексора 29 и с групгг выходов 76 блока 8 коммутации. Прохождение шк-эриации с группы адресных з; :одов 43 устройства зрпрещено. Если же хотя бы в одном из регистро 20 и 21 записан единичный сигнал метки конца команды, то в этом случае прохождение информации с выхода 76 блока 8 ко№4утации запрещено. На выходе коммутатора 9 поступает код адреса с группы входов 43 устройства По задне|угу фронту зтого же тактового импульса на выходе 90 коммутато ра 14 записи формируется задний фрон импульса записи, по которому в блоки 4 и 6 памяти записываются нулевые коды с группы выходов 68 и 79 соответственно шифратора 25 и блока 8 коммутации, а также осуществляется запись в регистр 21 кода микроопераций с группы выходов 74 блока 8 коммутации и запись кода адреса с группы выходов кo мyтaтopa 9 в регистр 18, запрещается выдача коммутатором 10 сигналов микроопераций из регистра 20 на группу выходов 47 микроопераций устройства. При отсутствии факта обнаружения искажений информации в сегментах, сформированной микрокоманды, устройство функционирует аналогично описан ному. Если в сформированной на группе выходов 60(61) блока 1(2) памяти 2-й микрокоманде зафиксировано искажение информации хотя бы в одном сегменте; (отказ сегмента) то на группе выходов 58(58) неисправности сформировьгоается позиционный код, номеров отказавших сегментов, отличный от нулевого. Причем, если при предыдущем обращении к 1-й микрокоманде блока 1(2) памяти искажения информации ни в одном из ее сегментов зафиксировано не было или обращения к ней после установки устройства в исходное состояние не производилось, что означает, что в 1-х ячейках блока 3(4) памяти резервных сегментов и блока 5(6) памяти номеров отказавших сегментов записаны нулевые коды и восстановление информации за счет них невозможно. Так как в этом случа блок 32(33) элементов И закры т нулевыми сигналами с выходов дешифратора 22(23), то на выходах коммутаторов 428 группы 11(12) коммутаторов, соответствующих отказавшим сегментам, будут сформированы единичные сигналы обращений и при этом на выходе элемента ИЛИ 36(37) появляется единичный сигнал а поступающий на выход 45(46) устройства и вход элемента И 30(31). При наличии на выходе 87 генератора 26 разрешающего сигнала открыт элемент И 30(31), единичный сигнал с выхода которого поступает на управляющий вход коммутатора 16(15). Этим запрещается прохождение через коммутатор 16(15) кода адреса, записанного в регистре 19(18), иразрешается прохождение кода адреса, записанного в регистре 18(19). Вследствие этого на группе выходов 61(60) блока 2(1) памяти формируется такой же код микрокоманды, , как и на группе выходов 60(61) блока 1(2) памяти. Если об.ращения в этой микрокоманде блока 2(1) памяти после установки устройг ства в исходное состояние ранее не производилось или при обращении к ней отказов ее сегментов зафиксировано не было, то в соответствующих ячейках блоков 4(3) и 6(5) памяти записаны нулевые коды. При этом блок 33(32) элементов И закрыт нулевыми сигналами с выходов дешифратора 23(22), поэтому на выходе элемента ИЛИ 34(35) сформирован нулевой сигнал. Если в сформированной на группе выходов 61(60) блока 2(1) памяти микрокоманде не зафиксировано искажение информации ни в одном из ее сегментов, что соответствует нулевому коду на группе выходов 59(58) неисправности , и выходах элементов ИЛИ 37(36) и И 31(30), то на выходах 74(73), 76(75х), 78(77) блока 8(7) коммутации, аналогично описанному, формируются коды операционной и адресной части и поля логических условий микрокоманды. Сформированный код поступает на группу входов 84(85) блока 7(8) комутации,, где осуществляется замещеие кодов отказавших сегментов микрокоманды, сформированной на группе выодов 60(61) блока 1(2) памяти, кодаи соответствующих сегментов микрокоанды, сформированной по тому же адресу на группе выходов 61(60) блока (1) памяти. При этом на группе выхоов 71(72) блока 7(8) коммутации форируется код .сегмента микрокоманды, меющего наибольший номер из числа отказавших и замещенных (код старшего из отказавших сегментов) кодом сегмента из противоположного плеча устройства с групп выходов 74(73), 76(75) и 78(77) блока 8(7) коммутаци Приоритетный шифратор 24(25) осуществляет преобразование унитарного позиционного кода номеров отказавших сегментов в двоичный код номера сегмента, код которого сформирован на группе выходов 71(72) блока 7(8) ком мутации. По заднему фронту тактового импульса с выхода 88(86). генератора 26 осуществляется запись информации в регистр 19(18) адреса и регистр 20(21) микроопераций. Кроме этого, на выходе 89(90) коммутатора 13(14) записи формируется задний фронт импульса записи, так как коммутатор 13(14) записи .открыт для прохождения тактового импульса нулевым сигналом выхода элемента ИЛИ 34(35). При этом в соответствующую адресу микрокоманд ячейку блока 3(4) памяти записан код старшего из отказавших сегментов с группы выходов 71(72) блока 7(8) коммутации, а в ячейку блока 5(6) памяти - номер этого сегмента с выхода приоритетного шифрагора 24(25), Выдача информации на группу выходов 47 микроопераций устройства в данном случае организована аналогично описанному. Далее устройство функ ционирует аналогично описанному.. Если же при организации замещения отка завших сегментов микрокоманды, сформированной на группе выходов 60(61), блока 1(2) памяти окажется, что и в J-й микрокоманде блока 2(1) памяти будет обнаружен отказ хотя бы одного из сегментов, то устройство функционирует следующим образом Аналогично описанному на выходах группы 12(11) коммутаторов, соответствующих номерам отказавших сегментов, формируются единичные сигналы обращений, вследствие чего на выходе элемента ИЛИ 37(36) формируется еди ничный сигнал. Однако при этом единичным (нулевым) сигналом с выхода 87 генератора 26 запрещено прохождение сигнала с выхода элемента ИЛИ 37(36) через элемент И 31(30) на управляющий вход коммутатора 15(16) адреса. Этим исключается нарушение работы устройства при одновременном формировании на выходах группы 11 и группы 12 коммутаторов кодов отличных от нуля, т.е. не происходит переключения коммутатора 13(16) разрешакнцего прохождение адреса на группы входов 50(51) блоков 1(2),,3(4) и 5(6) памяти с выхода регистра 19(18) адреса, если по заднему фронту ближайшего тактового импульса с выходов 86 или 88 генератора 26 осуществляется запись информации в регистры 19(18) и 20(21) с групп выходов блока 7(8) коммутации, чему соответствует единичное (нулевое) значение тактового импульса на выходе 87 генератора 26. При этом блок элементов И 33(32) закрыт нулевыми сигналами с выходов дешифратора 23(22).Если в 1-й микрокоманде, сформированной на группе выхода 61(60) блока 2 памяти,зафиксирован отказ хотя бы одного сегмента, номер которого совпадает с номером отказавшего сегмента 1-й микрокоманды блока 1(2) памяти и восстановление информации за счет информации, записанной в соответствующих ячейках блоков 3 и 4 памяти невозможно, то это означает, что на одноименных выходах группы 11 коммутаторов и группы 12, аналогично описанному, сформированы единичные сигналы обращений. Это совпадение номеров отказавш.их сегментов в обоих Микрокомандах зафиксировано при наличии разрешающего сигнала на управляющем входе 49 коммутатора 17, как ошибка в функционировании устройства. Разрешающий сигнал на входе 49 коммутатора 17 формируется тем же сигналом с выхода элемента ИЛИ 30(31), по которому было осуществлено переключение коммутатора 16(15) адреса, поступающим через элемент ИЛИ 40 на вход элемента 41 задержки. Задержка сигнала осуществляется на . время, необходимое для переключения коммутатора 16(15) адреса, формирование на выходах блоков 2(1), 4(3) и 6(5) кодов, соответствующих коду адреса, записанного в регистре 18)19), и формирования сигналов обращений . : группой 12(11) коммутаторов. Этим самым предупреждается формирование ложного сигнала при переходных процессах и при обнаружении искажения информации в одноименных сегментах микрокоманд, сформированных на выходах блоков 1 и 2 памяти в соответ;

ствии с разными адресами, т.е. сигнал ошибки формируется только в том случае, когда обнаружено искажение ни- ,;. формации в одноименных сегментах микрокоманд, сформированных на выходах блоков 1 и 2 памяти по адресу, установленному или в регистре 18 или в регистре 19, при условии, что восгстановление за счет информации, записанной в соответствующих ячейках бло-Ю ков 3 и 4 памяти резервных сегментов невозможно. Сформированный сигнал ошибки с вы хода коммутатора 17 выдается на выход 48 ошибки устройства и через эле мент ИЛИ 39 - на нулевой вход тригге ра 27 управления. Вследствие этого триггер 27 устанавливается в нулевое состояние, нулевым сигналом с его вы хода запрещается выдача генератора 26 тактовых импульсов, устройство прекращает работу. Если же -й микрокоманде, сформированной из группы выходов 61(60) блока 2(1) памяти, бу дет обнаружен отказ хотя бы одного сегмента, восстановление информации в котором невозможно за счет хода, записанного в 1-й ячейке блока 4(3) памяти, а при этом его номер не будет совпадать ни с одним из номеров отказавших сегментов 1-й микрокоманды, сформированной на группе выходов 60(61) блока 1(2) памяти, то это будет означать отсутствие факта совпаг дения единичных сигналов обращения н на одноименных выходах групп 11 и 12 коммутаторов, т.е. отсутствие факта ошибки. Вследствие этого на группах выхоДОН 78(77), 76(75) и 74(73) аналогич ,но описанному формируется код резерв ной микрокоманды, которая поступает на группу входов 84(85) блока 7(8) коммутации, где осуществляется замещение отказавших сегментов 1-й микрок рманды, сформированной на выходах блока 1(2) памяти, причем информация сегментов, номера которялх соответствуют номерам выходов группы 11(12) коммутаторов, на которых сформированы нулевые сигналы для восстановления отказавших сегментов микрокоманды, сформированной на выходах блока 1(2) памяти, не используются. Устройство функционирует аналогично описанйому.. По переднему фронту тактового импульса на выходе 88 генератора 26

разрешается вьщача информации из регистра 21(20) на группу выходов 47 микроопераций устройства. По заднему фронту этого импульса осуществляется запись информации в регистр 19(18) адреса и регистр 20(21) микроопераций, формируется задний фронт импульса записи, по которому в f-e ячейки блоков 3(4) и 5(6) памяти осуществляется запись соответственно номег ра старшего из отказавших сегментов 1-й микрокоманды блока 1(2) памяти, имеющего максимальный номер и его код, и т.д. Если после этого при очередном обращении к К-й микрокоманде блока 1(2) памяти искажения информации ни в одном из ее сегментов не обнаружено, т.е. причиной искажения информации был сбой, то, аналогично описанному, формируется код микрокоманды на вьпсодах блока 7 (8) , коммутации и в 1-е ячейки блоков 5(6) и 3(4) записываются нулевые коды. Блок 32(33) элементов И при этом закрыт нулевыми сигналами с группы выходов 58(59) неисправности, на выходах группы 11(12) коммутаторов обращений сформирован нулевой код. Если в сформированной на выходах блока 1(2) памяти 1-й микрокоманде зафиксировано искажение информации хотя бы в одном из сегментов и при последнем обращении к ней после установки устройства в исходное состояние тоже зафиксирован факт отказа одного из сегментов, т.е. в 1-й ячейке блока 5(6) памяти записан код номера сегмента, отличный от нулевого. ° Устройство функционирует следующим образом. Двоичный код номера сегмента, поступающий с группы выходов 52(53) блока 5(6) памяти номеров от- . казавших сегментов, преобразуется дешифратором 22(23) в позиционный унитарный код номера сегмента I-u микрокоманды, код которого записан в 1-й ячейке блока 3(4) памяти резервных сегментов. Если номер одного из отказавших сегментов совпадает с номером сегмента, код которого записан в Г-й ячейке блока 3(4) памяти, т.е. в микрокоманде имеет место факт устойчивого отказа одного из сегментов, то на выходе соответствующего элемента И . блока 32(33) элементов И появится единичный сигнал, так как он будет

открыт единичными сигналами с соответствующих выхода дешифратора 22(23) и выхода групп выходов 58(69) неисправности блока 1(2) памяти, благодаря чему на выходе элемента ИЛ 34(35) формируется единичный сигнал. При отсутствии на выходе 54(55) неисправности блока 3(4) памяти единичного сигнала, свидетельствующего о наличии искажения информации, записанной в его ячейке на выходе группы 11(12.) коммутаторов, соответствующем этому сегменту микрокоманды единичного сигнала обращения, не формируется, блок 7(8) коммутации организует замещение кода этого сегмента кодом, записанным в Г-й ячейке блока 3(4) памяти резервных сегментов. Далее устройство функционирует аналогично описанному, причем записи информации в блоки 5(6) и 3(4) памяти производиться не будет, так как формирование импульса записи коммутатором 13(14) запрещено нулевым сигналом с выхода 54(55) неисправности блока 3,(4) памяти и единичным сигналом с выхода элемента ИЛИ 34(35), свидетельствующим о повторении отказа одного из сегментов микрокоманды .

Если же на выходе 54(55) неисправ ности блока 3(4) памяти сформирован единичный сигнал неисправности, то на соответствующем выходе группы 11(12) коммутаторов будет сформирован единичный сигнал обращения, так как соответствующий отказавшему сегменту, номер которого записан в ячейке блока 5(6) памяти, коммутатор открыт единичными сигналами с выходов 5(53) неисправности блока 3(4) памяти и с выхода группы выходов 58(59) неисправности блока 1(2) памяти.

Далее устройство функционирует аналогично описанному, т.е. для отка завших сегментов, восстановление информации в которых за счет информации, записанной в ячейке блока 3(4), невозможно по причине отказа в бло.ке 3(4) памяти или отсутствия в нем необходимой информации, организуется замещение кодами сегментов микрокомады с выходов блока 8(7) коммутации.

;Если при организации замещения отказавших сегмейтов микрокоманды, сфорjмированной на выходах блока 1(2) памяти, будет зафиксирован факт повторения отказа какого-либо сегмента

микрокоманды, сформированной на выходах блока 2(1.) памяти, то при отсутствии единичного сигнала на выходе 55(54) блока 4(3) памяти, свидетельствующего о наличии искажения информации, записанной в ячейке памяти, организуется аналогично описанному замещение за счет кода записан.- ного в ячейке блока 3(4) памяти ре зервных сегментов.

Этим обеспечивается сохранение работоспособности устройства при отказе пары одноименных сегментов (не более одной) одноименных микрокоманд для случая, когда в один из блоков 3 или 4 памяти при предьщущем обращении к этой микрокоманде был записан правильный код этого сегмента.

Формула изобрел тения

Микропрограммное устройство управления, содержащее два блока микрокоманд, два регистра адреса, два регистра микроопераций, два блока коммутации, коммутатор микроопераций, три коммутатора адреса, две группы элементов И, триггер, генератор тактовых импульсов, пять элементов ИЛИ, первый и второй элементы И н элемент задержки, причем группа выходов первого коммутатора адреса соединена с группой информационных входов первог регистра адреса, группы выходов первого и второго регистров адреса соедин ены с первыми группами информационных входов соответственно второго и третьего коммутаторов адреса, группы выходов которых соединены с группами адресных в:содов соответственно первого и второго блоков памяти микрокоманд, группы информащюнных выходов первого и второго блоков памяти микрокоманд соединены с первьми группами информационных входов соот ветственно первого и второго блоков кдммутации, первые группы выходов которых соединены с группами информации онных входов соответственно первого и второго .регистров микроопераций, группы выходов микроопераций первого и второго регистров микроопераций соединены соответственно с первыми и вторыми группами информационных входов коммутатора микроопераций, выходы немодифицируемых разрядов адреса, второй группы выходов первого блока коммутации соединены с входами немодифицируемых разрядов адреса группы информационных входов второго регистра адреса, группы выходов неис правности первого и второго блоков памяти микрокоманд соединены соответственно с первыми входами соответ ствующих элементов И первой и второй групп элементов И, выходы которых соединены с соответствующими входами первого и второго элементов И, выход третьего элемента ИЛИ соединен с вхо дом элемента задержки, группа вькодов коммутатора микроопераций являет ся группой выходов микроопераций устройства, отличающееся тем, что, с целью повышения достовер ности эа счет повышения устойчивости I устройства к сбоям и отказам в ячейках блоков памяти микрокоманд, в него введены два блока памяти номеров отказавших сегментов, коммутатор ошибки, два коммутатора записи, две группы коммутаторов обращений, два дешифратора, два шифратора, два мультиплексора, два элемента ИЛИ и два блока памяти резервных сегментов, каждый из которых включает блок оперативной памяти информационный выход которого подключен к входу сумматора по модулю два, причем группа входов микроопераций устройства соединена с первой группой информационных входов первого коммуг. татора адреса, группа выходов разрядов немодифицируемой части адреса второго выхода второго блока коммутации соединена с входами немодифицируемых разрядов адреса второй группы информационных входов первого коммутатора адреса, вход Пуск устройства соединен с единичным входом триггера, единичный выход которого соединен с входом генератора тактовых импульсов, первый выход генератора тактовых импульсов соединен с входами синхронизации первого регистра адреса и второго регистра микроопераций, с первым управляющим входом коммутатора микроопераций, управляющим входом первого коммутатора записи, . второй выход генератора тактовых импульсов соединен с входами синхронизации первого регистра микроопераций и второго регистра адреса, с вторым управляющим входом соммутатора микроопераций и управляющим входом второго коммутат1эра записи, третий выход генератора тактовых импульсов соединен с первыми входами первого и второго 442 элементов И, группа выходов второго коммутатора адреса соединена соответственно с группами адресных входов блока оперативной памяти первого блока памяти резервных сегментов и первого блока памяти номеров отказавших сегментов, а группа выходов третьего коммутатора адреса соединена с группами адресных входов блока оперативной памяти второго блока памяти резервных сегментов и второго блока памяти номеров отказавших сегментов группы, информационные выходы блоков оперативной памяти первого и второго блоков памяти резервного сегмента соединены с вторыми группами информационных входов соответственно первого и второго блоков коммутации, выходы сумматоров по модулю два первого и второго блоков памяти резервных сегментов соединены с первыьш входами коммутаторов соответственно первой и второй групп коммутаторов обращений, с первыми информационными входами соответственно второго и первого коммутаторов записи и третьими информационными входами соответственно первого и второго блоков коммутации, группы выходов неисправностей первого и второго блоков памяти микрокоманд соединены с четвертыми групЬами информационных входов соответственно первого и второго блоков коммутации, группами входов соответственно первого и второго шифраторов, группы выходов неисправностей первого и второго блоков памяти микрокоманд соединены с информационными входами соответствующих коммутаторов обращений соответственно первой и второй групп, группы выходов коммутаторов обращений первой и второй групп соединены соответственно с первой и второй группами информационных входов коммутатора ошибки, с группами входов соответственно четвертого и пятого элементов ИЛИ и с пятыми группами информационных входов первого и второго блоков коммутации, третьи группы выходов которых соединены с группами информационных входов блоков оперативной памяти соответственно первого и второго блоков памяти резервных сегментов, выходы элементов И первой и второй групп соединены с инверсными управляющими входами соответствующих коммутаторов первой и второй групп коммутаторов обраще- : НИИ соответственно и с шестыми группами, информационных входов соответственно первого и второго блоков ком мутации, четвертые группы выходов которых соединены с первыми группами входов соответственно первого и второго мультиплексоров логических усло вий, выходы модифицируемого разряда второй группы выходов первого и второго блоков коммутации соединены с вторыми входами соответственно перво го и второго мультиплексоров логичес ких условий, группа входов логических, условий устройства соединена с третьими группами информационных вхо дов первого и второго мультиплексоров логических условий, выходы которых соединены с входами модифицируемых разрядов соответственно группы информационных входов второго регистра адреса и второй группы информационных входов первого коммутатора адреса, первая, вторая и четвертая группы выходов первого и второго бло ков коммутации соединены с входами седьмой группы входов соответственно второго и первого блоков коммутации, выходы первого и второго шифраторов соединены с группами информационных входов соответственно первого и второго блоков памяти номеров отказавших сегментов, выходы которых соединены соответственно с входами первого и второго дешифраторов, выходы первого и второго дешифраторов соединены с вторыми входами элементов И соответственно первой и второй групп элементов И, выходы первого и второго элементов ИЛИ соединены с третьими входами соответственно IBToporo и первого коммутаторов записи, выходы первого и второго коммутаторов записи соединены с входами записи блоков оперативной памяти соответственно первого и второго блоков памяти резервных сегментов и блоков памяти номеров отказавших сегментов выходы четвертого и пятого элементов ИЛИ соединены соответственно с вторыми входами первого и второго элемен тов И, выходы которых соединены с управляющими входами соответственно второго и третьего коммутаторов адреса и с первым и вторым входами третьего элемента ИЛИ, группы выходов первого и второго регистров адреса соединены с вторьми входами группы информационных входов соответственнр третьего и второго коммутаторов адреса, выход элемента задержки соединен с управляющим входом коммутатора ошибки, выход которого является выходом ошибки устройства и соединен с первым входом шестого элемента ИЛИ, выходы полей меток конца команды первого и второго регистров ю-шроопераций соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого соединен с управляющим входом первого коммутатора адреса, выход метки конца работы коммутатора микроопераций соединен с вторым входом шестого элемента ИЛИ, выход которого соединен с нулевым входом триггера, выходы четвертого и пятого элементов ИЛИ являются соответственно первым и вторым выходами неисправности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управления ЦВМ с повышенной надежностью. Цель изобретения - повьппение отказоустойчивости устройства за счет повышения устойчивости устройства к сбоям и отказам в ячейках блоков памяти микрокоманд. В устройство введены два блока памяти номеров отказавших сегментов, коммутатор ошибки, два коммутатора записи, две группы коммутаторов обращений, два дешифратора, два шифратора, два мультиплексора, два элемента ИЛИ, два блока памяти резервных, сегментов. Сущность изобретения состоит в повышении отказоустойчивости за счет использования идентичных блоков памяти, в которых по одним и тем же адресам записаны одинаковые микрокоманды, организации записи в соответствуюi щую ячейку соответствующего блока памяти резервных сегментов кода, ко(Л С торым было осуществлено замещение одного из сегментов микрокоманды,в кото-, ром было обнаружено искажение инфор- мации сегмента. 5 ил.

Фиг. 2

В9(30)п 90(51) п 11(12)

(51) п

L:J

5(5-7; i

70т) «,4 75Г75; 77(7В)

JW

97(Щ

9(Ш

f

аг.5

г-/ г/

П п п п п п

П П П П П П

q.

Поле

мго

/(К I

Поле

I I 21.1 /№li

/wr Я6/Л

to&ro 4jKXЛДайиеЫЛ Kco/f0 4J

вых.

Saofat ffojie

гаг

TX X X л вга

KBJS

/ A - X л y л д X

.

61

/ X g

oKol

fbffe

/ / X A A o

ггг ег/

Aff.

y

И pj Ы

Лаг. 73

S&if 93

п п п 11 ГТП

Air.

п п п п 30

727

t

1ГП

Т

r i.

j ж/г

-

J /f/r

Т

т

т

Г7 ГГ

Г Т

F f ГЛ

т

я

т

т т

фиг. 5

| Перестраиваемое микропрограммное устройство управления | 1976 |

|

SU646333A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1985-04-12—Подача