1 Изобретение относится к вычислительной технике и может быть использовано для контроля последовательности прохождения сигналов в различных автоматизированных системах управления и устройствах автоматики.

Цель изобретения - расширение функциональных возможностей за счет выдачи кода сигнала, на котором произошла ошибка.

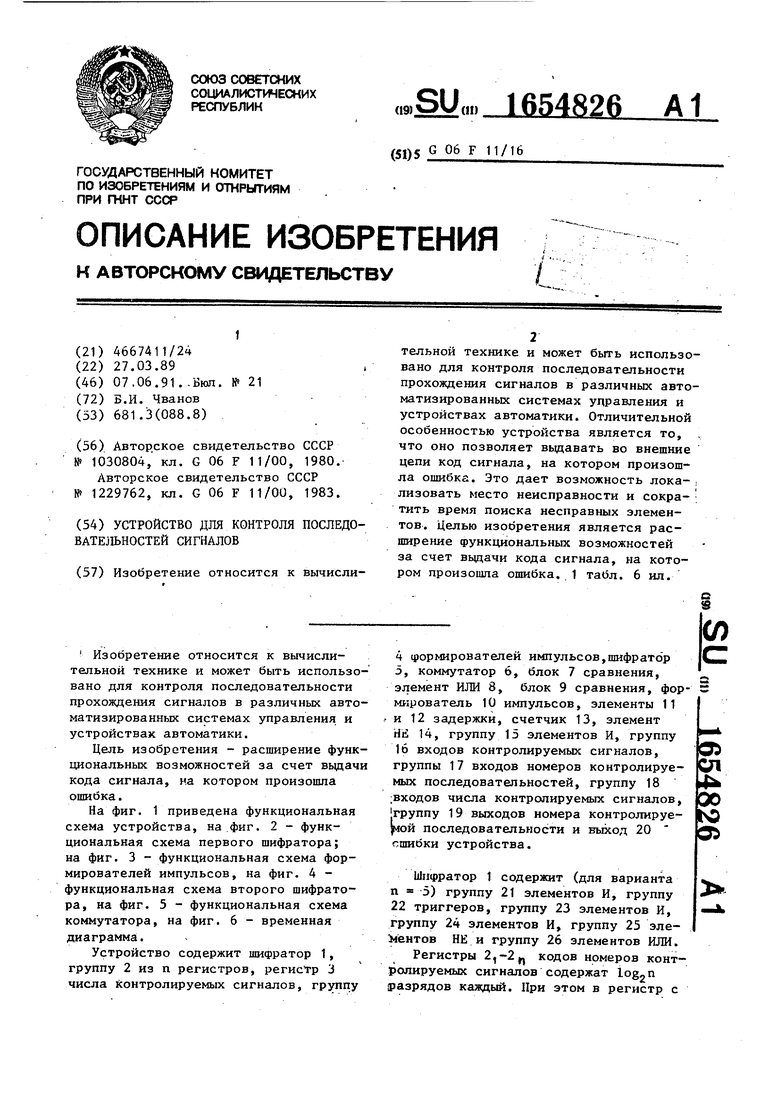

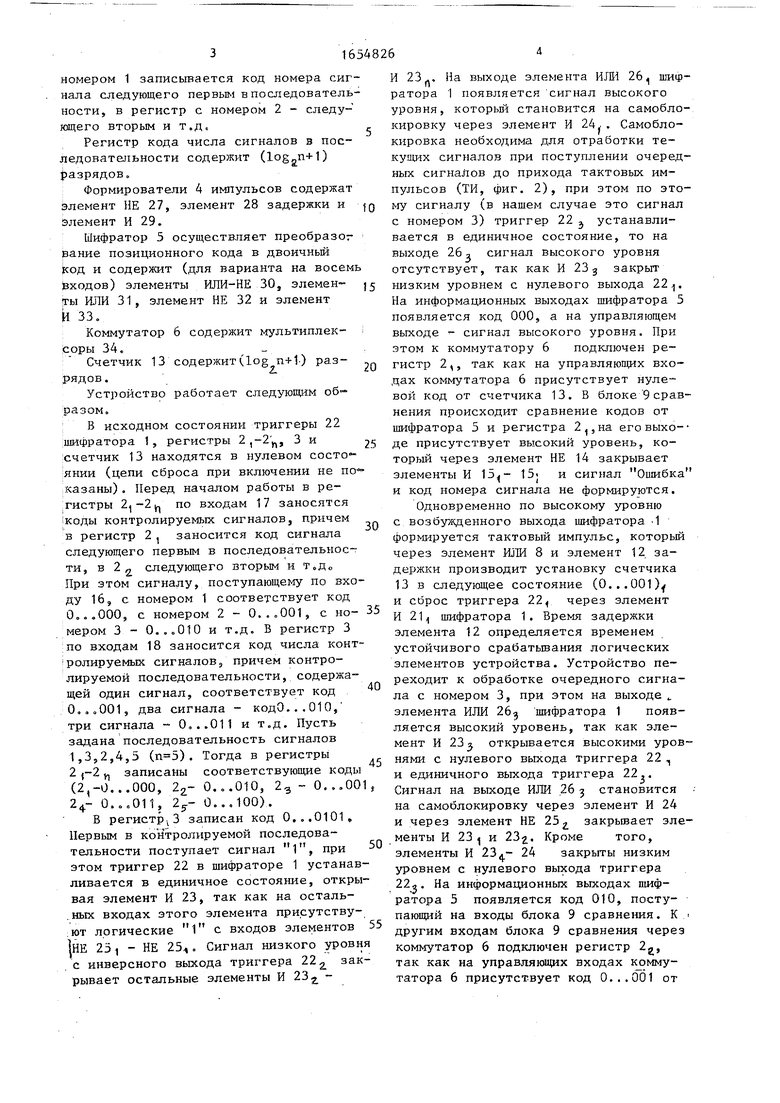

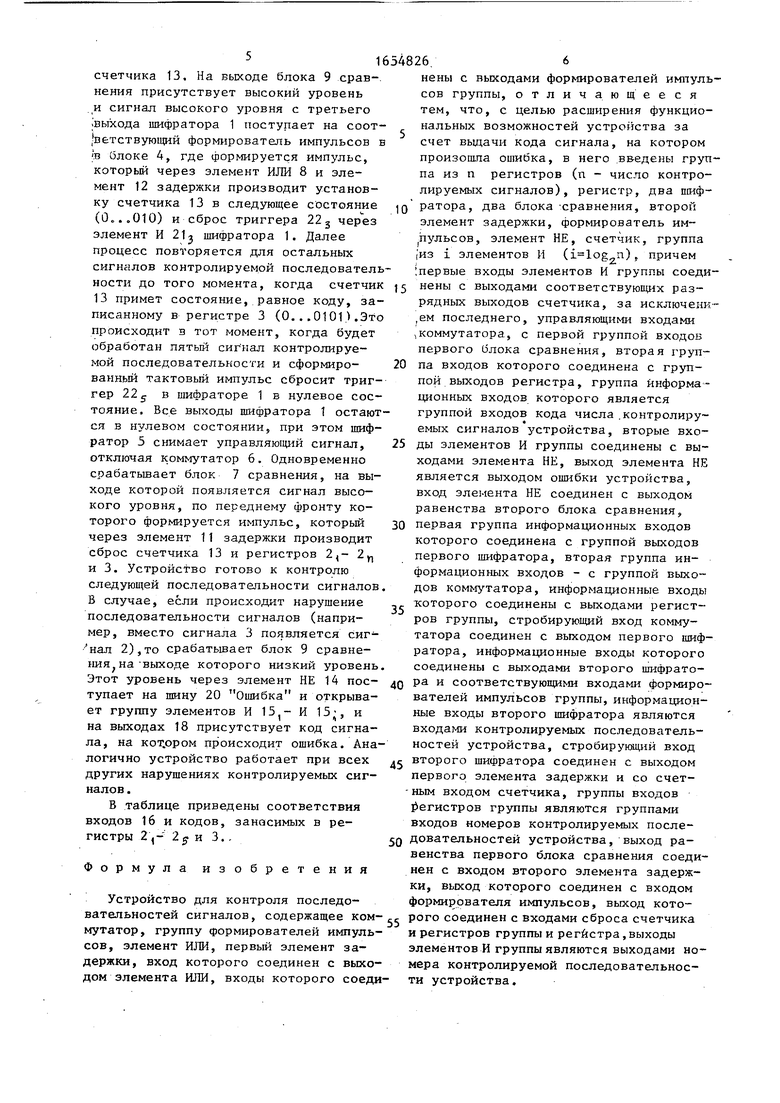

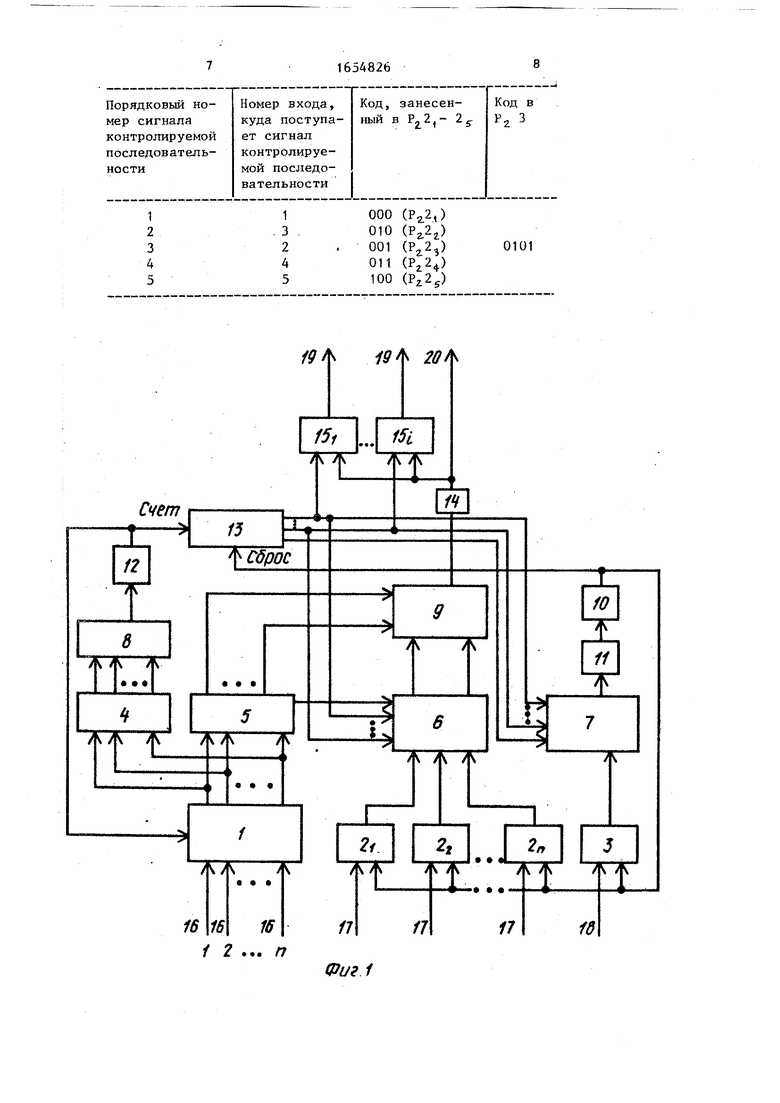

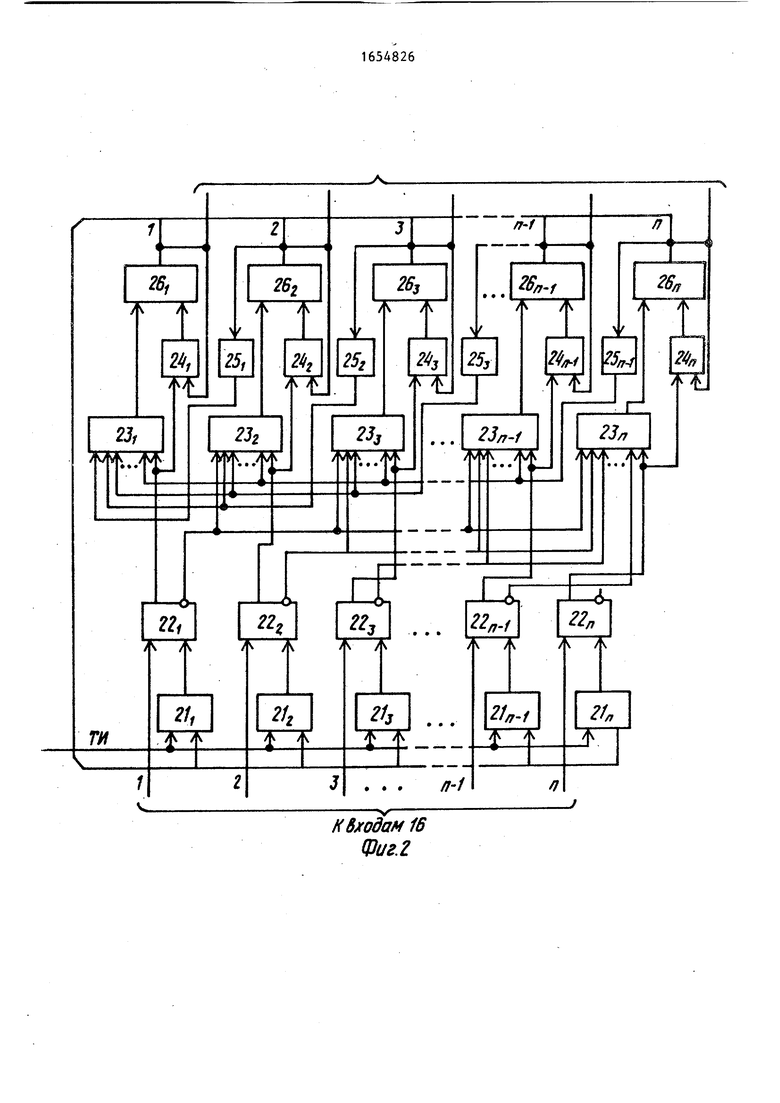

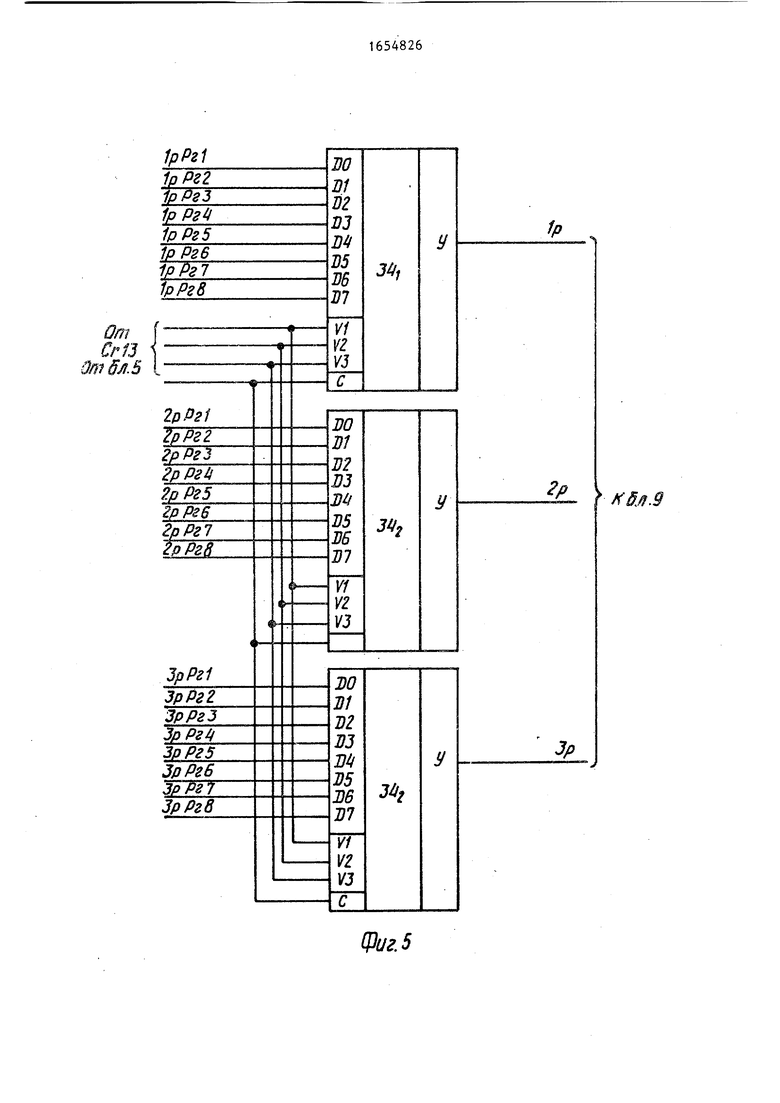

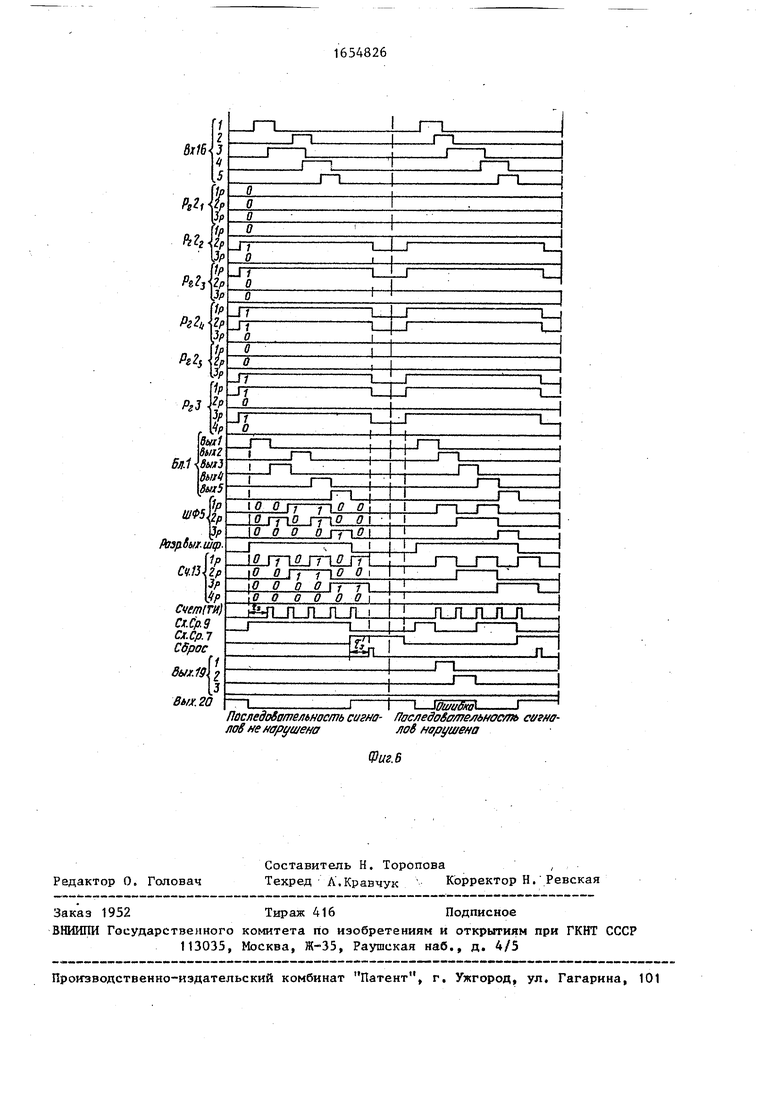

На фиг. 1 приведена функциональная схема устройства, на фиг. 2 - функциональная схема первого шифратора; на фиг. 3 - функциональная схема формирователей импульсов, на фиг. 4 - функциональная схема второго шифратора, на фиг. 5 - функциональная схема коммутатора, на фиг. 6 - временная диаграмма.

Устройство содержит шифратор 1, группу 2 из п регистров, регистр J числа контролируемых сигналов, группу

4 формирователей импульсов,шифратор 5, коммутатор 6, блок 7 сравнения, элемент ИЛИ 8, блок 9 сравнения, формирователь 10 импульсов, элементы 11 и 12 задержки, счетчик 13, элемент riri 14, группу 15 элементов И, группу 16 входов контролируемых сигналов, группы 17 входов номеров контролируемых последовательностей, группу 18 .входов числа контролируемых сигналов, группу 19 выходов номера контролируе- последовательности и выход 20 -шибки устройства.

Шифратор 1 содержит (для варианта п 5) группу 21 элементов И, группу 22 триггеров, группу 23 элементов И, группу 24 элементов И, группу 25 элементов НЕ и группу 26 элементов ИЛИ.

Регистры кодов номеров контролируемых сигналов содержат Iog2n разрядов каждый. При этом в регистр с

О

ел

-U

номером 1 записывается код номера сигнала следующего первым в последовательности, в регистр с номером 2 - следующего вторым и т.д.

Регистр кода числа сигналов в последовательности содержит (log2n-H) разрядов.

Формироватепи 4 импульсов содержат элемент НЕ 27, элемент 28 задержки и элемент И 29.

Шифратор 5 осуществляет преобразог вание позиционного кода в двоичный код и содержит (для варианта на восемь входов) элементы ИЛИ-НЕ 30, элемен- ты ИЛИ 31, элемент НЕ 32 и элемент И 33,

Коммутатор 6 содержит мультиплексоры 34.

Счетчик 13 содержит(log n-M) разрядов.

Устройство работает следующим образом.

В исходном состоянии триггеры 22 шифратора 1, регистры 2 ,-2, 3 и счетчик 13 находятся в нулевом состоянии (цепи сброса при включении не показаны) . Перед началом работы в регистры по входам 17 заносятся коды контролируемых сигналов, причем в регистр 2 j заносится код сигнала следующего первым в последовательности, в 2 2 следующего вторым и т„д0 При этом сигналу, поступающему по входу 16, с номером 1 соответствует код 0...000, с номером 2 - 0...001, с но- мером 3 - 0...010 и т.д. В регистр 3 по входам 18 заносится код числа контролируемых сигналов, причем контролируемой последовательности, содержащей один сигнал, соответствует код О ,„ „ 001, два сигнала - код 0... 010, три сигнала - 0...011 и т.д. Пусть задана последовательность сигналов 1,3,2,4,5 (). Тогда в регистры 2 {-2 у, записаны соответствующие коды (2,-0...000, 22 0...010, 23 - 0...00 24- 0...011, 2ff- 0...100).

В регистрV3 записан код 0...0101, Первым в контролируемой последовательности поступает сигнал 1, при этом триггер 22 в шифраторе 1 устанавливается в единичное состояние, открывая элемент И 23, так как на остальных входах этого элемента присутствуют логические 1 с входов элементов |НЕ 25 - НЕ 25,, о Сигнал низкого уровн с инверсного выхода триггера 22 закрывает остальные элементы И 23г

0

Q

;

5 5 ,

- 5540

И 23 п, На выходе элемента ИЛИ 261 шифратора I появляется сигнал высокого уровня, который становится на самоблокировку через элемент И 24,. Самоблокировка необходима для отработки текущих сигналов при поступлении очередных сигналов до прихода тактовых импульсов (ТИ, фиг. 2), при этом по этому сигналу (в нашем случае это сигнал с номером 3) триггер 22 5 устанавливается в единичное состояние, то на выходе 26ч сигнал высокого уровня отсутствует, так как И 23 $ закрыт низким уровнем с нулевого выхода 22,. На информационных выходах шифратора 5 появляется код 000, а на управляющем выходе - сигнал высокого уровня. При этом к коммутатору 6 подключен регистр 2, так как на управляющих вхо- цах коммутатора 6 присутствует нулевой код от счетчика 13. В блоке 9 сравнения происходит сравнение кодов от шифратора 5 и регистра 215на еговыхо-- де присутствует высокий уровень, который через элемент НЕ 14 закрывает элементы И 15| и сигнал Ошибка и код номера сигнала не формируются.

Одновременно по высокому уровню с возбужденного выхода шифратора 1 формируется тактовый импульс, который через элемент ИЛИ 8 и элемент 12 задержки производит установку счетчика 13 в следующее состояние (0...001) и сброс триггера 22 через элемент И 21,, шифратора 1. Время задержки элемента 12 определяется временем устойчивого срабатывания логических элементов устройства. Устройство переходит к обработке очередного сигнала с номером 3, при этом на выходе „ элемента ИЛИ 26 шифратора 1 появляется высокий уровень, так как элемент И 23з открывается высокими уровнями с нулевого выхода триггера 22 и единичного выхода триггера 22,. Сигнал на выходе ИЛИ 26 становится на самоблокировку через элемент И 24 и через элемент НЕ 25 закрывает элементы И 23 1 и 23. Кроме того, элементы И 23 л - 24 закрыты низким уровнем с нулевого выхода триггера 22я. На информационных выходах шифратора 5 появляется код 010, поступающий на входы блока 9 сравнения. К другим входам блока 9 сравнения через коммутатор 6 подключен регистр 2g, так как на управляющих входах коммутатора 6 присутствует код 0...001 от

счетчика 13. На выходе блока 9 сравнения присутствует высокий уровень и сигнал высокого уровня с третьего . выхода шифратора 1 поступает на соот- , ветствуюший формирователь импульсов в ;в блоке 4, где формируется импульс, который через элемент ИЛИ 8 и элемент 12 задержки производит установку счетчика 13 в следующее состояние (0...010) и сброс триггера 223 через элемент И 21 шифратора 1. Далее процесс повторяется для остальных сигшшов контролируемой последовательности до того момента, когда счетчик 13 примет состояние, равное коду, записанному в регистре 3 (0...0101).Это происходит з тот момент, когда будет обработан пятый сигнал контролируемой последовательности и сформированный тактовый импульс сбросит триггер 225 в шифраторе 1 в нулевое состояние. Все выходы шифратора t остаются в нулевом состоянии, при этом шифратор 5 снимает управляющий сигнал, отключая коммутатор 6. Одновременно срабатывает блок 7 сравнения, на выходе которой появляется сигнал высокого уровня, по переднему фронту которого формируется импульс, который через элемент 11 задержки производит сброс счетчика 13 и регистров 2{- 2п и 3. Устройство готово к контролю следующей последовательности сигналов В случае, если происходит нарушение последовательности сигналов (например, вместо сигнала 3 появляется сиг- нал 2),то срабатывает блок 9 сравне- ния;на-выходе которого низкий уровень Этот уровень через элемент НЕ 14 поступает на шину 20 Ошибка и открывает группу элементов И 15(- И 15, и на выходах 18 присутствует код сигнала, на кот.ором происходит ошибка. Аналогично устройство работает при всех других нарушениях контролируемых сигналов .

В таблице приведены соответствия входов 16 и кодов, заносимых в регистры 2,- 3..

Формула изобретения Устройство для контроля последо0

5

0

нены с выходами формирователей импульсов группы, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выдачи кода сигнала, на котором произошла ошибка, в него введены группа из п регистров (п - число контролируемых сигналов), регистр, два шифратора, два блока сравнения, второй элемент задержки, формирователь им- гпульсов, элемент НЕ, счетчик, группа , из i элементов И (i log2n)5 причем первые входы элементов И группы соединены с выходами соответствующих разрядных выходов счетчика, за исключенк- ,ем последнего, управляющими входами ,коммутатора, с первой группой входов первого блока сравнения, вторая группа входов которого соединена с группой выходов регистра, группа информационных входов которого является группой входов кода числа контролируемых сигналов устройства, вторые вхо5 ды элементов И группы соединены с выходами элемента НЕ, выход элемента НЕ является выходом ошибки устройства, вход элемента НЕ соединен с выходом равенства второго блока сравнения, первая группа информационных входов которого соединена с группой выходов первого шифратора, вторая группа информационных входов - с группой выходов коммутатора, информационные входы которого соединены с выходами регистров группы, стробирующий вход коммутатора соединен с выходом первого шифратора, информационные входы которого соединены с выходами второго шифратоQ ра и соответствующими входами формирователей импульсов группы, информационные входы второго шифратора являются входами контролируемых последовательностей устройства, стробирующий вход

с второго шифратора соединен с выходом первого элемента задержки и со счет- -ным входом счетчика, группы входов регистров группы являются группами входов номеров контролируемых послеQ довательностей устройства, выход равенства первого блока сравнения соединен с входом второго элемента задержки, выход которого соединен с входом формирователя импульсов, выход кото0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для ввода информации | 1987 |

|

SU1442999A2 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Устройство для сбора данных по табельному учету | 1986 |

|

SU1332349A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля последовательности прохождения сигналов в различных автоматизированных системах управления и устройствах автоматики. Отличительной особенностью устройства является то, что оно позволяет выдавать во внешние цепи код сигнала, на котором произошла ошибка. Это дает возможность локализовать место неисправности и сократить время поиска несправных элементов. Целью изобретения является расширение функциональных возможностей за счет выдачи кода сигнала, на котором произошла ошибка. 1 табл. 6 ил.

вательностей сигналов, содержащее ком-,, рого соединен с входами сброса счетчика мутатор, группу формирователей импуль- и регистров группы и регистра,выходы сов, элемент ИЛИ, первый элемент задержки, вход которого соединен с выходом элемента ИЛИ, входы которого соедиэлементов И группы являются выходами но мера контролируемой последовательности устройства.

рого соединен с входами сброса счетчика и регистров группы и регистра,выходы

элементов И группы являются выходами номера контролируемой последовательности устройства.

1 2 ... п

Фиг 1

К Входам 16 Фиг.2

f

I

s

Ј

Ul

f

Cw

&

(

Ul

-C00

NJ

H м

Ь1 N

Sa

ЛГ

I

4a

Кбл.9

Фиг. 5

Последовательность сигно- Паследоба/пеяьнос/пь сигналов не нарушеналов нарушена

Фиг. В

| Приспособление для смазывания этикеток клеем | 1955 |

|

SU103080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательности сигналов | 1984 |

|

SU1229762A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1989-03-27—Подача