О1

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Программируемая многоканальная система имитации объекта | 1987 |

|

SU1522250A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для преобразования сигналов информационно-измерительной системы | 1982 |

|

SU1062751A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФОРМЫ КРИВОЙ НАПРЯЖЕНИЯ | 2014 |

|

RU2580944C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для преобразования в цифровые коды множества аналоговых сигналов, изменение которых от канала к каналу имеет равномерный закон распределения по всему динамическому диапазону. Цель изобретения - повышение быстродействия устройствыа. В устройство, содержащее N триггеров (N -число каналов) 8.1-8.N, элемент И 9, цифровой сумматор 4, регистр 5 памяти, цифроаналоговый преобразователь 6, с целью повышения быстродействия введены аналоговый коммутатор 2, аналого-цифровой преобразователь 3, N вычитателей 1.1-1.N и блок 7 определения канала с минимальным сигналом. 3 ил.

Од

О)

ТИ

315206

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования в цифровые коды множества аналоговых сигналов,, изменение которых от канала к каналу имеет равномерный закон распределения по всему динамическому диапазону

Целью изобретения является повьше- ю ответствующий аналоговой величине

ние быстродействия.

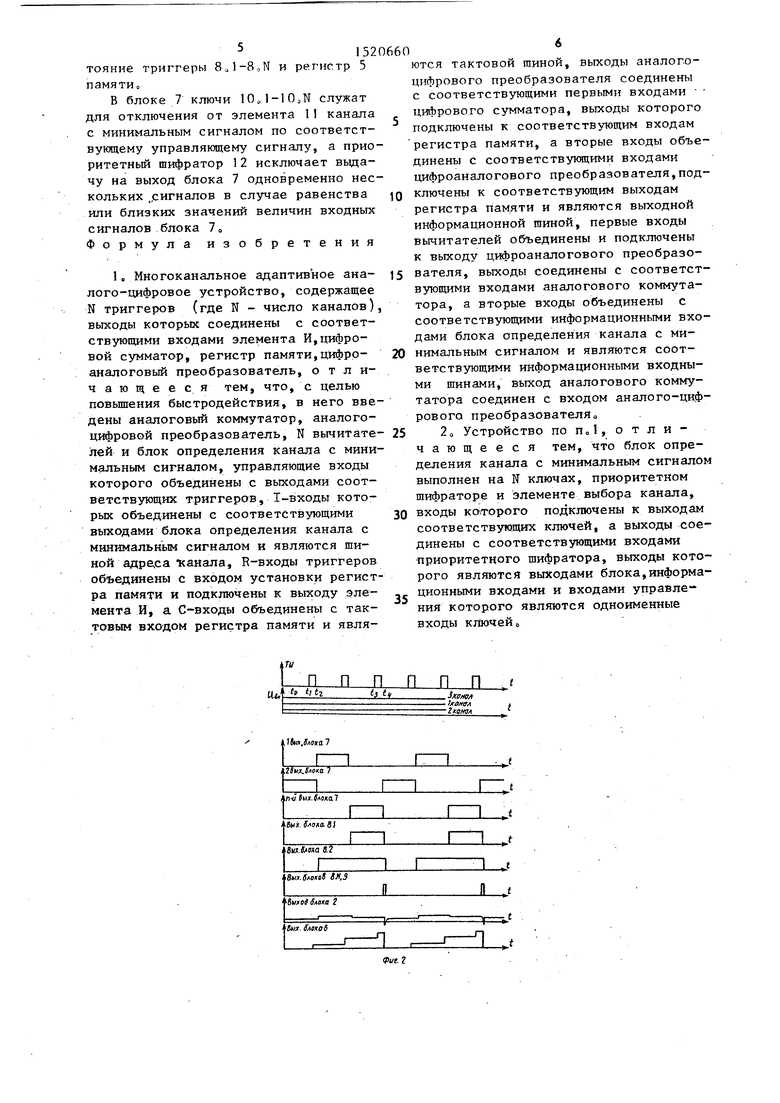

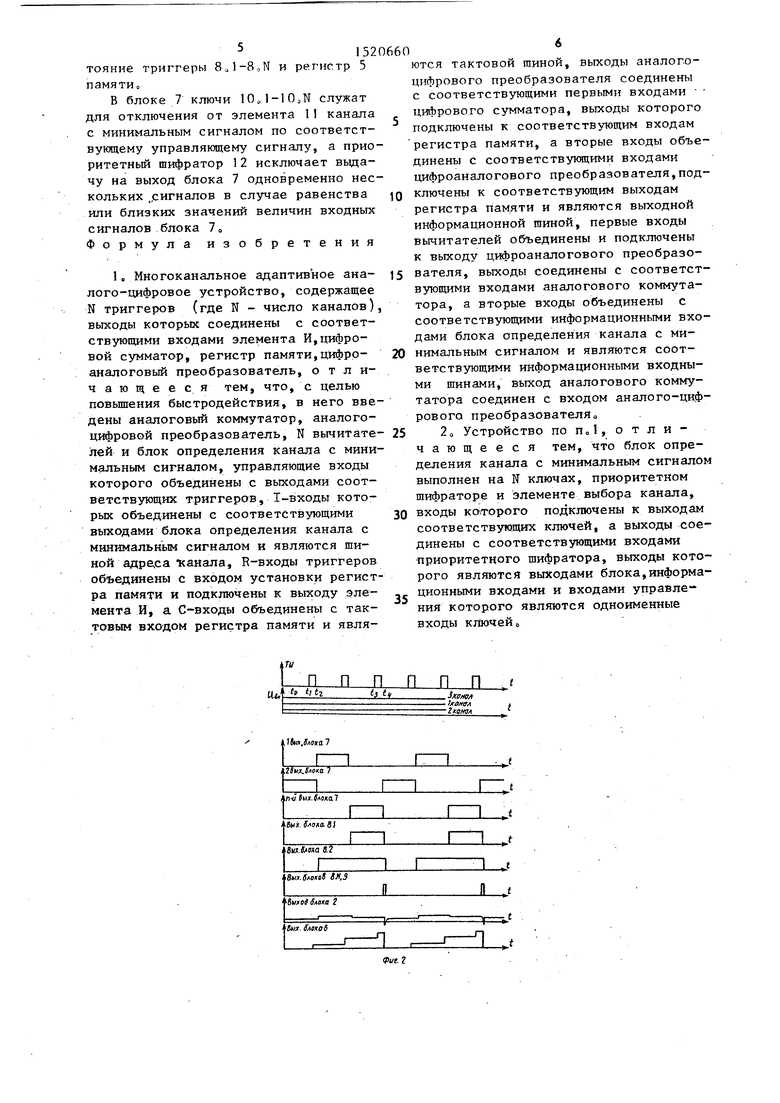

На фиго приведена структурная схема многоканального адаптивного аналого-цифрового устройства; на фиГо2 - временная диаграмма, поясняю щая работу устройства; на фиг„ 3 - функциональная схема блока определения канала с минимальным сигналом. Устройство (фиГо) содержит N вычитателей lil-l,N, аналоговый ком- мутатор 2, аналого-цифровой преобразователь (АЦП) 3, цифровой сумматор 4, регистр 5 памяти, цифроаналоговьй преобразователь (ЦАП) 6, блок 7 определения канала с минимальным сигналом, К триггеров 8.1-8oN, элемент . И9 и ключи lOol-lOoN.

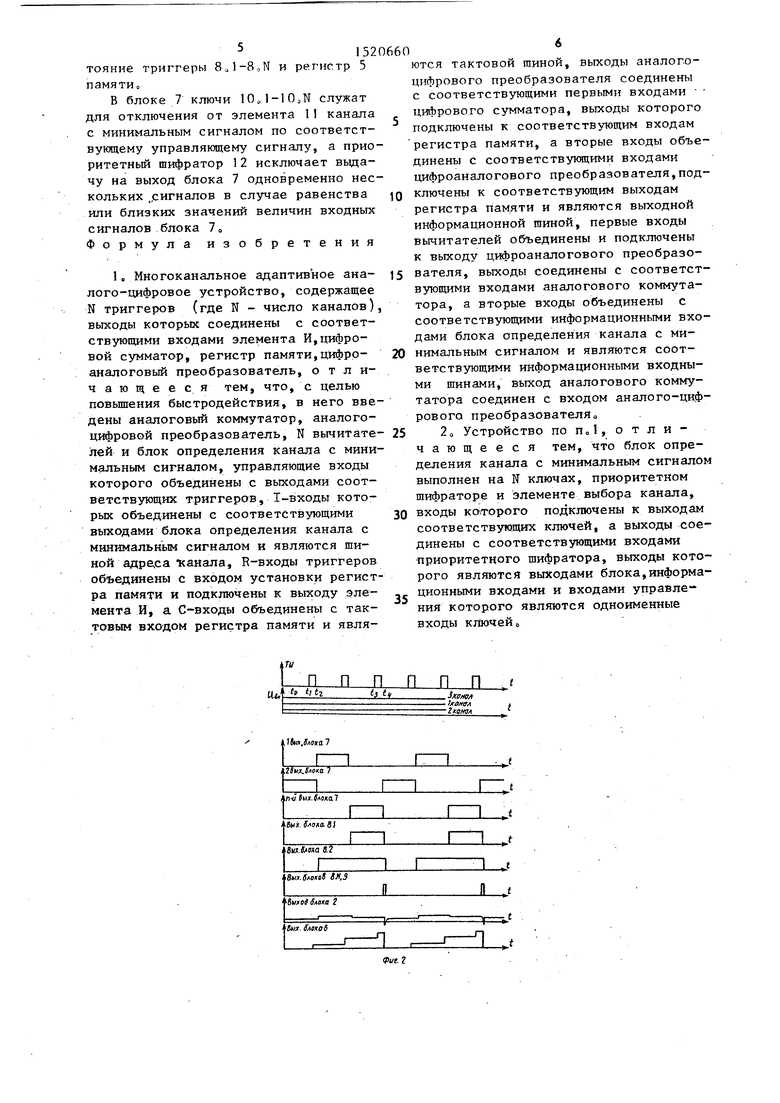

Блок 7 (фиГоЗ) содержит элемент П выбора канала и приоритетньш шифратор 12о

Многоканальное адаптивное аналого цифровое устройство работает следзпо- щим образом.

В начальный момент t триггеры 8ol-8oN и регистр 5 находятся в нулевом состоянии (установка в О на схеме не показана). Напряжение на вычитающих входах вычитателей lol-loN равно нулк1, и входные сигналы без изменения проходят на входы аналогового коммутатора 2. Входные сигналы подаются также на входы блока 7 определения канала с минимальным сигналомо На выходе этого блока соответствующем входу с минимальным в данный момент времени сигналом (например, втором), вьфабатывается

сигнал уровня логической 1 , на о.с- тальных выходах блока 7 - Уровень логической 1 с выхода блока 7 определения канала -с минимальным сигналом поступает на вход управления аналогового коммутатора 2,подключающего К; А1Ш 3 минимальный из входных сигналов, и на 1-вход соответствующего триггера 8.2„ При помощи АЦП 3 производится аналого-цифровое преобразование входного сигнала,т.е. на выходе АЦП 3 возникает код,соответствзпощии величине минимального из входных сигнала (2-й канал).Этот код суммируется цифровым сумматором 4с кодом, хранящимся в регистре 5 памяти, и подается на входы регистра 5 памятио По переднему фронту тактового импульса код записывается в регистр 5 памяти. В дальнейшем код,со5

0

второго канала, поступает на вход ЦАП 6 и на выходные шины устройства. При помощи ЦАП 6 осуществляется преобразование двоичного кода в аналого- вьй сигнал, Тоео с выхода ЦАП 6 снимается сигнал, напряжение которого равно наименьшему из входных напряжений Это напряжение поступает на вычитающие входы вычитателей 1.1 - 1«Но По заднему фронту тактового импульса триггер 8„2, на 1-входе которого находится уровень логической II til

0

5

0

, устанавливается в единичное сос- т ояниео В дальнейшем сигнал уровня логической 1 с выхода триггера 8.2 поступает на соответствукщий вход управления блока 7 определения канала с минимальным сигналом и выключает второй канаЛо Затем блок 7 определяет канал с минимальным по величине входным сигналом из оставшихся включенными каналов (1-й канал) и формирует сигнал уровня логической 1 на соответствующем выходе.

По сигналу с выхода блока 7 определения канала с минимальным сигналом аналоговый коммутатор 2 подключает к входу АЦП 3 выход первогЬ вычи- тателя 1о1, на котором находится напряжение, равное разности между вторым по величине и наименьшим входными сигналами В дальнейшем устройст- во работает аналогично, АЦП 3 преобразует разности между соседними по . величине входными сигналами канала, а в регистре 5 памяти поочередно формируются коды, соответствующие входным сигналам, которые возникают путем суммирования и накопления этих разностей о По сигналам на выходньгх . шинах адреса канала можно определить, какой именно канал включен в данньй моменто По окончании цикла опроса всех каналов многоканального адаптивного следящего АЦП триггеры S.I-B.N устанавливаются в единичное состояние (t(j), на выходе элемента И 9 формируется сигнал уровня логической 1, устанавливающий в исходное сос0

5

тояние триггеры 8ol-8oN и регистр 5 памяти

В блоке 7 ключи lO -lOoN служат для отключения от элемента 11 канала с минимальным сигналом по соответствующему управляющему сигналу, а приоритетный шифратор 12 исключает выдачу на выход блока 7 одновременно нескольких ригналов в случае равенства или близких значений величин входных сигналов блока 7, Формула изобретения

0660

10

15

20

25 ются тактовой гаиной, выходы аналого- цифрового преобразователя соединены с соответствующими первыми входами цифрового сумматора, выходы которого подключены к соответствующим входам регистра памяти, а вторые входы объединены с соответствуклцими входами цифроаналогового преобразователя,подключены к соответствующим выходам регистра памяти и являются выходной информационной шиной, первые входы вычитателей объединены и подключены к выходу цифроаналогового преобразователя, выходы соединены с соответствующими входами аналогового коммутатора, а вторые входы объединены с соответствующими информационными входами блока определения канала с минимальным сигналом и являются соответствующими информационными входными шинами, выход аналогового коммутатора соединен с входом аналого-цифрового преобразователя

2 о Устройство по По 1, о т л и чающееся тем, что блок опре25

деления канала с минимальным сигналом выполнен на N ключах, приоритетном шифраторе и элементе выбора канала, 30 входы KOiToporo подключены к выходам соответствующих ключей, а выходы соединены с соответствующими входами приоритетного шифратора, выходы которого являются выходами блока,информационными входами и входами управления которого являются одноименные входы ключей

35

i2N Входы улрад/1ения

Фш.з

71

.l

.2 .N

J

| Золотова ТоМ, Кербликов А.И, Резе.нблат МоА, Резервирование аналоговых устройств автоматики, - М, 1986, Со 95 | |||

| Адаптивный многоканальный следящий преобразователь аналог-код | 1985 |

|

SU1267618A1 |

Авторы

Даты

1989-11-07—Публикация

1987-04-22—Подача