N)

Изобретение относится к радиотехнике, может быть использовано в системах фазовой автоподстройки частоты и является усовершенствованием устройства по авт. св. К 1251289о

Цель изобретения - повышение помехоустойчивости и сокращение времени перехода в режим сравнения фаз из режима сравнения частот.

На фиг. представлена электрическая схема цифрового частотно-фазового дискриминатора; на фиг„2 и 3 - временные диаграммы, поясняющие его работу.15

Цифровой частотно-фазовый дискриминатор (фиг.Ц содержит счетчик 1, вход 2 счетных импульсов, вход 3 опор- Hbix импульсов, статический регистр 4, сигнальный вход 5, блок 6 запрета, 20 элемент ИСЮГОЧАЮЬЦЕЕ ИЛИ 7, первый 8 и второй 9 D-триггеры, формирователь Ю коротких импульсов, элемент ИЛИ 11, элемент И 12, пяты11 13, четвертый

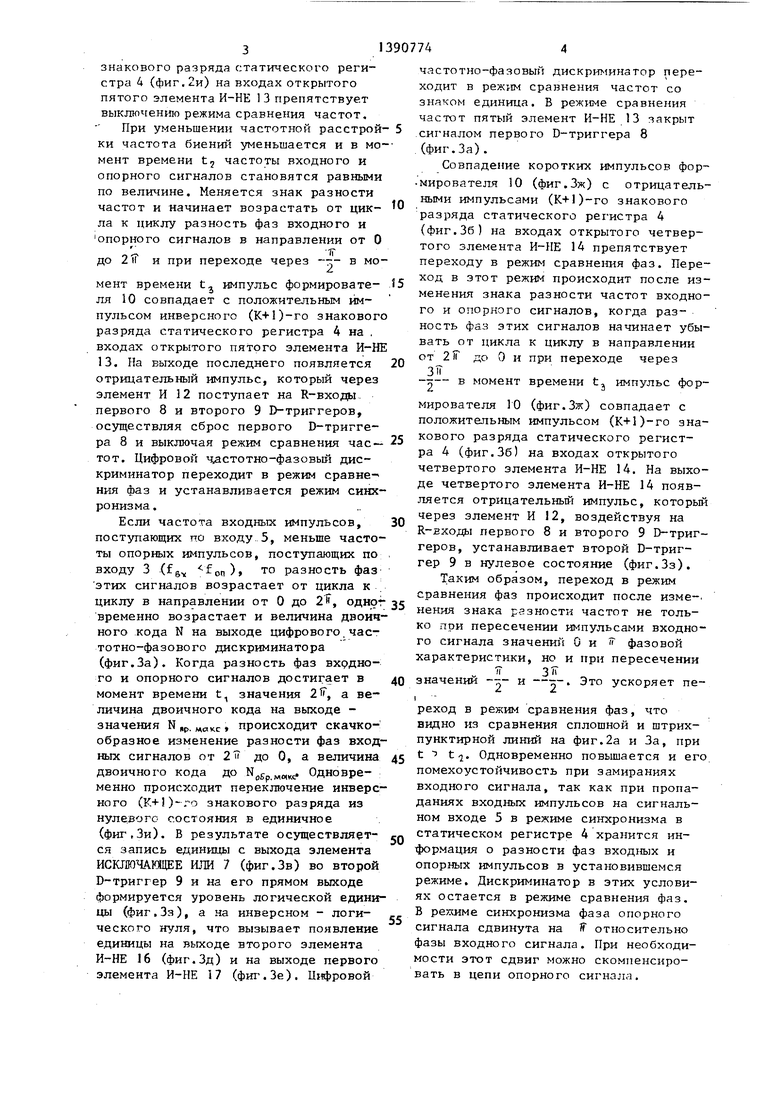

ра (фиг.2а). Когда разность фаз входного и опорного сигналов достигает в момент време1Зд t, значения О, а величина двоичного К(1да на выходе цифрового частотно-фазового дискриминатора - значения N.p , происходит скачкообразное изменение разности фаз входных сигналов от О до 2if, а величины двоичного кода до N, . Одновременно происходит переключение (К+1)-го знакового разряда статического регистра 4 из нулевого состояния в единичное (фиг.26), в результате осуществляется запись единицы с выхода элемента ИСКЛЮЧАЮУДЕЕ ИЛИ 7 (фиг.2в) в первый D-триггер 8.

На ирямом выходе D-триггера 8 формируется уровень логической единицы (фиг.2г), а на инверсном - уровень логического нуля,, что вызывает появление логической единицы на выходе второго элемента И-НЕ 16 (фиг.2д), т.е. в старшем зд aчaщeм разряде вы14, третий 15, второй .16 и первый 17 25 ходного кода цифрового частотно-фазоЭ1)ементы И-НЕ.

Цифровой частотно-фазовый дискриминатор работает следующим образом.

О.порными импульсами,, поступающими от входа 3 на R-вход установки нуля счетчика 1, на выходах последнего устанавливаются нули. На счетный Т- вход Счетчика 1 по входу 2 поступают счетные импульсы. При этом частота счетных импульсов жйнием

, 1

вого дискриминатора. Этот сигнал отключает младшие значащие разряды выходного кода, поступающего через блок 6 запрета, а также вызывает по- 30 явление логической единицы на выходе элемента ИЛИ П. На выходе первого элемента И-НЕ 17, т.е. в знаковом разряде выходного кода устанавливается уровень логического нуля (фиг.2е). определяется выра- ос В результате цифровой частотно-фазовыи дискриминатор переходит в режим сравнения частот со знаком ноль,

где

сч -

.

2 -1 - емкость счетчика 1;

Т - период опорных импульсов.

В момент прихода на сигнальный вход 5 входного импульса (на С-вход статического регистра 4) информация из счетчика 1 записывается в статический регистр 4. образом, на выходе этого регистра формируется двоичный код, величина N которого пропорциональна разности фаз входно- го и опорного импульсов.

Если частота входных импульсов,- поступающих на сигнальный вход 5, бсэльше частоты опорных импульсов, поступающих на вход 3 (f а fpn ), то разность фаз этих сигналов убывает от цикла к циклу в направлении от 2 Д|Э 0. Одновременно убывает и величин.а двоичного кода N на выходе цифро- В1ЭГО частотно-фазового дискриминатора (фиг.2а). Когда разность фаз входного и опорного сигналов достигает в момент време1Зд t, значения О, а величина двоичного К(1да на выходе цифрового частотно-фазового дискриминатора - значения N.p , происходит скачкообразное изменение разности фаз входных сигналов от О до 2if, а величины двоичного кода до N, . Одновременно происходит переключение (К+1)-го знакового разряда статического регистра 4 из нулевого состояния в единичное (фиг.26), в результате осуществляется запись единицы с выхода элемента ИСКЛЮЧАЮУДЕЕ ИЛИ 7 (фиг.2в) в первый D-триггер 8.

На ирямом выходе D-триггера 8 формируется уровень логической единицы (фиг.2г), а на инверсном - уровень логического нуля,, что вызывает появление логической единицы на выходе второго элемента И-НЕ 16 (фиг.2д), т.е. в старшем зд aчaщeм разряде вы0

5

0

5

выи дискриминатор переходит в режим сравнения частот со знаком ноль,

В режиме сравнения частот на выходе статического регистра 4 возникает сигнал биений (пунктирная кривая на фиг.2а). Частота биений равна разности частот входного и опорного сигналов. На выходе формирователя 10 коротких импульсов, работающего по отрицательному фронту выходного сигнала элемента ИСКЛОЧАЮЩЕЕ ИЛИ 7, возникают короткие импульсы (фиг.2ж), которые поступают на входы пятого 13 и четвертого 14 элементов И-НЕ. В режиме сравнения частот t t t четвертый элемент И-Ь|Е 14 закрыт нулевым уровнем прямого выхода второго D-триггера 9 (фиг.2з), а пятый элемент И-НЕ 13 открыт, так как на его вход поступает сигнал единичного - уровня с прямого выхода первого D-x триггера 8. Совпадение коротких импульсов формирователя 10 с отрицательными импульсами инверсного (К+1)-го

10

знакового разряда статического регистра 4 (фиг.2и) на входах открытого пятого элемента И-НЕ 1 3 препятствует выключению режима сравнения частот,

- При уменьшении частотной расстрой- 5 сигналом первого D-триггера 8

ки частота биений уменьшается и в мо- (фиг.За)

мент времени t частоты входного и

опорного сигналов становятся равными

по величине. Меняется знак разности

частот и начинает возрастать от цикла к циклу разность фаз входного и

опорного сигналов в направлении от О

ТС

до 2II и при переходе через --- в момент времени tj импульс формировате- 15 ля 10 совпадает с положительным импульсом инверсного (К+1)-го знакового разряда статического регистра 4 на , входах открытого пятого элемента И-НЕ 13, На выходе последнего появляется 20 отрицательный импульс, который через элемент И 12 поступает на R-входы первого 8 и второго 9 D-триггеров, осуществляя сброс первого D-триггера 8 и выключая режим сравнения час- 25 ...™ тот. Цифровой частотно-фазовый дискриминатор переходит в режим сравне-- кия фаз и устанавливается режим синхронизма .

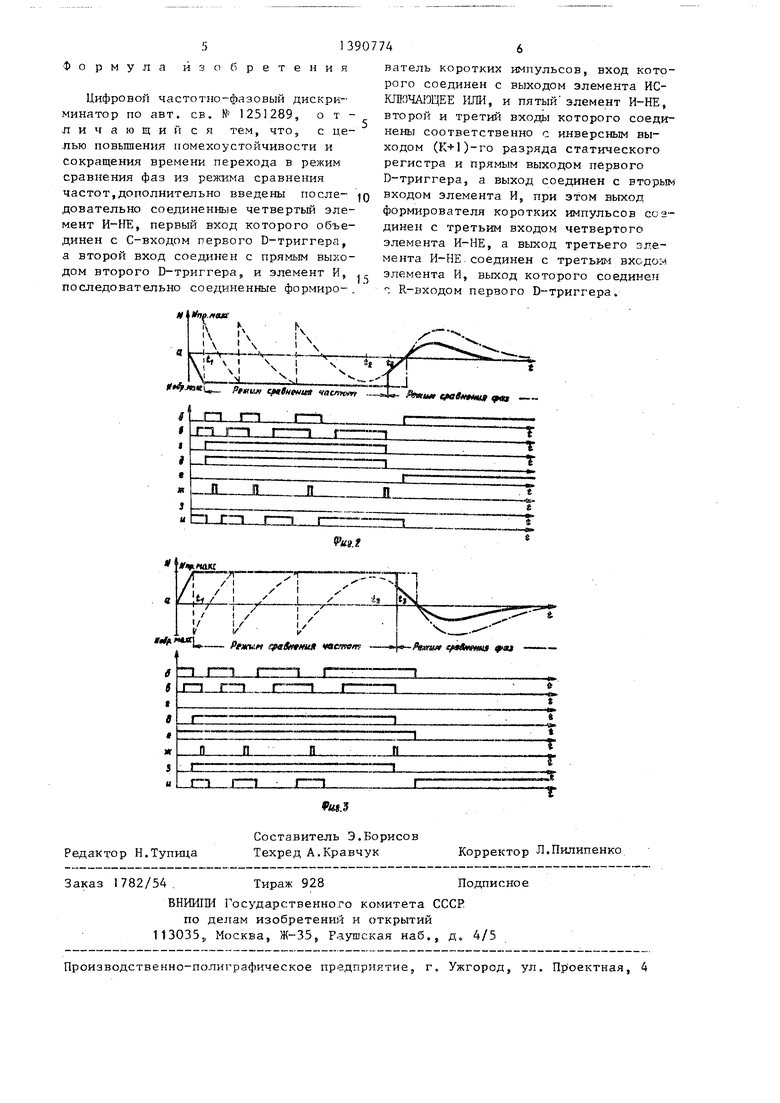

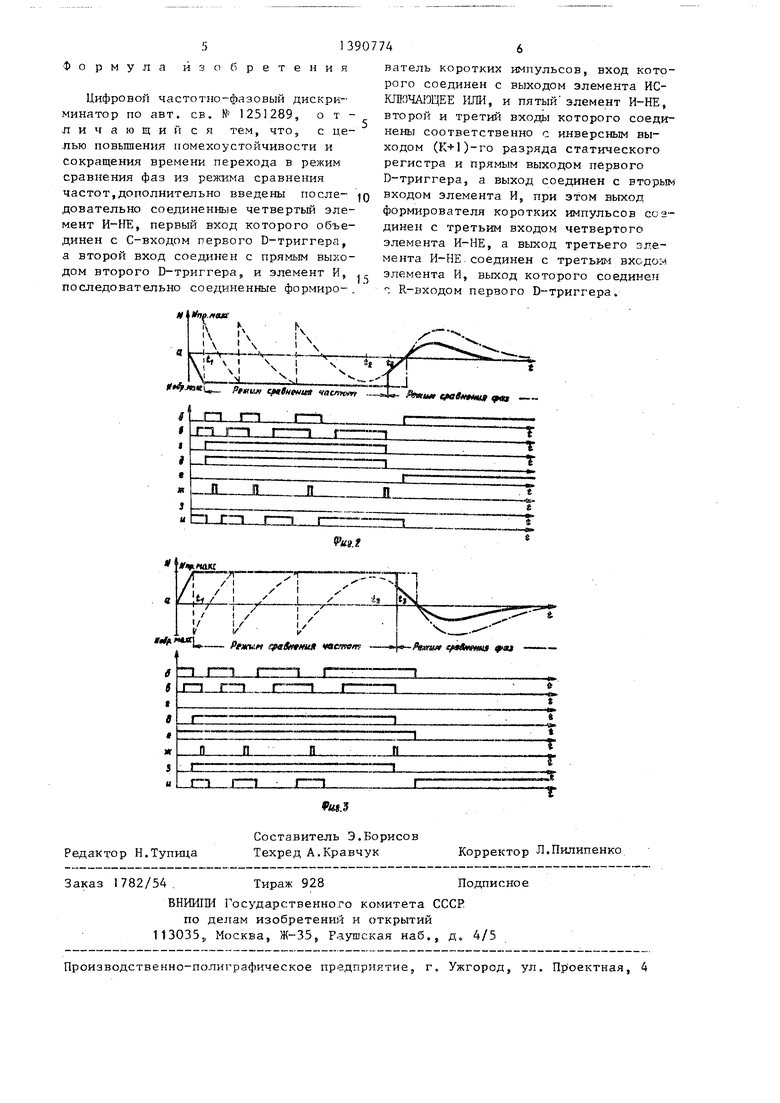

Если частота входных импульсов, 30 поступающих по входу 5, меньше частоты опорных импульсов, поступающих по . входу 3 (fg fon) то разность фаз этих сигналов возрастает от цикла к циклу в направлении от О до 2W, однрг 35 временно возрастает и величина двоичного кода N на выходе цифрового.частотно-фазового дискриминатора (фиг.За). Когда разность фаз вхрдно- го и опорного сигналов достигает в дО момент времени t., значения 2, а величина двоичного кода на выходе - значения N ,р. , происходит скачкообразное изменение разности фаз входных сигналов от 2 и до О, а величина 45 Одновременно повышается и его двоичного кода до „„ Одновре-помехоустойчивость при замираниях

менно происходит переключение инверсного (К+1)-го знакового разряда из нулевого состояния в единичное (фиг.Зи). В результате осуществляется запись единицы с выхода элемента ИСКЛЮЧАЩЕЕ ИЛИ 7 (фиг.Зв) во второй D-триггер 9 и на его прямом выходе формируется уровень логической единицы (фиг, Зз), а на инверсном - логи- В синхронизма фаза опорного ческого нуля, что вызывает появлениесигнала сдвинута на If относительно

единицы на выходе второго элемента И-НЕ 16 (фиг.Зд) и на выходе первого элемента И-НЕ 17 (фш .Зе). Цифровой

50

частотно-фазовый дискриминатор переходит в режим сравнения частот со знаком единица, В режиме сравнения частот пятый элемент И-НЕ 13 закрыт

Совпадение коротких импульсов фор- мирователя 10 (фиг.Зж) с отрицательными импульсами (К+1)-го знакового разряда статического регистра 4 (фиг.Зб) на входах открытого четвертого элемента И-НЕ 14 препятствует переходу в режим сравнения фаз. Переход в этот режим происходит после изменения знака разности частот входного и опорного сигналов, когда разность фаз этих сигналов начинает убывать от цикла к циклу в направлении от 2F до О и при переходе через

...

-«- в момент времени tj импульс формирователя 10 (фиг.Зж) совпадает с положительным импульсом (К+1)-го знара 4 (фиг.Зб) на входах открытого четвертого элемента И-НЕ 14. На выходе четвертого элемента И-НЕ 14 появляется отрицательный импульс, который через элемент И 12, воздействуя на R-Еходы первого 8 и второго 9 D-триггеров, устанавливает второй D-триггер 9 в нулевое состояние (фиг,3з).

Таким образом, переход в режим сравнения фаз происходит после изме-. нения знака разности частот не только при пересечении импульсами входного сигнала значений О и фазовой характеристики, но и при пересечении

. 3

значении -;:- и -. Это ускоряет пеI

реход в режим сравнения фаз, что видно из сравнения сплошной и штрих- пунктирной линий на фиг.2а и За, при

входного сигнала, так как при пропаданиях входных импульсов на сигнальном входе 5 в режиме синхронизма в статическом регистре 4 хранится информация о разности фаз входных и опорных импульсов в установившемся режиме. Дискриминатор в этих условиях остается в режиме сравнения фаз.

фазы входного сигнала. При необходимости этот сдвиг можно скомпенсировать в цепи опорного сигнала.

сигналом первого D-триггера 8

частотно-фазовый дискриминатор переходит в режим сравнения частот со знаком единица, В режиме сравнения частот пятый элемент И-НЕ 13 закрыт

0

5 0

Совпадение коротких импульсов фор- мирователя 10 (фиг.Зж) с отрицательными импульсами (К+1)-го знакового разряда статического регистра 4 (фиг.Зб) на входах открытого четвертого элемента И-НЕ 14 препятствует переходу в режим сравнения фаз. Переход в этот режим происходит после изменения знака разности частот входного и опорного сигналов, когда разность фаз этих сигналов начинает убывать от цикла к циклу в направлении от 2F до О и при переходе через

...

-«- в момент времени tj импульс формирователя 10 (фиг.Зж) совпадает с положительным импульсом (К+1)-го зна ...™

Одновременно повышается и его помехоустойчивость при замираниях

ра 4 (фиг.Зб) на входах открытого четвертого элемента И-НЕ 14. На выходе четвертого элемента И-НЕ 14 появляется отрицательный импульс, который через элемент И 12, воздействуя на R-Еходы первого 8 и второго 9 D-триггеров, устанавливает второй D-триггер 9 в нулевое состояние (фиг,3з).

Таким образом, переход в режим сравнения фаз происходит после изме-. нения знака разности частот не только при пересечении импульсами входного сигнала значений О и фазовой характеристики, но и при пересечении

. 3

значении -;:- и -. Это ускоряет пеI

реход в режим сравнения фаз, что видно из сравнения сплошной и штрих- пунктирной линий на фиг.2а и За, при

Одновременно повышается и его помехоустойчивость при замираниях

В синхронизма фаза опорного сигнала сдвинута на If относительно

входного сигнала, так как при пропаданиях входных импульсов на сигнальном входе 5 в режиме синхронизма в статическом регистре 4 хранится информация о разности фаз входных и опорных импульсов в установившемся режиме. Дискриминатор в этих условиях остается в режиме сравнения фаз.

В синхронизма фаза опорного сигнала сдвинута на If относительно

фазы входного сигнала. При необходимости этот сдвиг можно скомпенсировать в цепи опорного сигнала.

Формула

бретения

Цифровой частотно-фазовый дискриминатор по авт. св. № 1251289, отличающий ся тем, что, с целью повышения помехоустойчивости и сокращения времени перехода в режим сравнения фаз из режима сравнения частот,дополнительно введены после- довательно соединенные четвертый элемент И-НЕ, первый вход которого объединен с С-входом первого D-триггвра, а BTOpofi вход соединен с прямым выходом второго D-триггера, и элемент И, ,,. элемента И, выход которого соединен

последовательно соединенные формиро-.

R-входом первого D-триггера.

ватель коротких импульсов, вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и пятый элемент И-НЕ, второй и третий входы которого соединены соответственно с инверсным выходом (К+1)-го разряда статического регистра и прямым выходом первого D-триггера, а выход соединен с вторьпч входом элемента И, при этом выход формирователя коротких импульсов соэ- динен с третьим входом четвертого элемента И-НЕ, а выход третьего элемента И-FIE. соединен с третьим входом

R-входом первого D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| Цифровой частотно-фазовый дискриминатор | 1984 |

|

SU1256139A1 |

| Цифровой частотно-фазовый дискриминатор | 1982 |

|

SU1027798A1 |

| Цифровой частотно-фазовый дискриминатор | 1991 |

|

SU1826122A1 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1363431A2 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1251289A1 |

| Цифровой частотно-фазовый дискриминатор | 1983 |

|

SU1117824A1 |

| Частотный манипулятор | 1989 |

|

SU1688440A1 |

| Способ фазовой автоподстройки частоты управляемого генератора и устройство для его осуществления | 1989 |

|

SU1788576A1 |

| Цифровой фазовый дискриминатор | 1989 |

|

SU1693713A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости и сокращение времени перехода в режим сравнения фаз из режима сравнения частот. Цифровой частотно-фазовый дискриминатор (ЦЧФД) содержит счетчик 1, статический регистр (СР) А, блок 6 запрета, элемент, ИСКЛЮЧАИЧЕЕ ИЛИ 7, D-тригге- ры 8, 9, формирователь 10 коротких импульсов, элемент ИЛИ 11, элемент И 12, элементы И-НЕ 13-17. Опорные импульсы поступают на вход 3 счетчика 1, а счетные импульсы - на вход 2. Со счетчика 1 информация заносится в СР 4, На выходе СР 4 формируется код, пропорциональный разнести фаз входного и опорного импульсов. Если частота входных импульсов больше частоты опорных импульсов, то разность фаз убывает от 2ТТ до 0. При скачкообразном изменении разности фаз от О до 2Т происходит переключение знакового разряда СР 4 из нулевого состояния в единичное, что вызывает переход дискриминатора в релсзда сравнения частот. В этом режиме на выходе СР 4 возникает сигнал биений. 3 ил. (Л с

%«ШГ tfetHMHOt ftu .„

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1251289A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-23—Публикация

1986-08-25—Подача