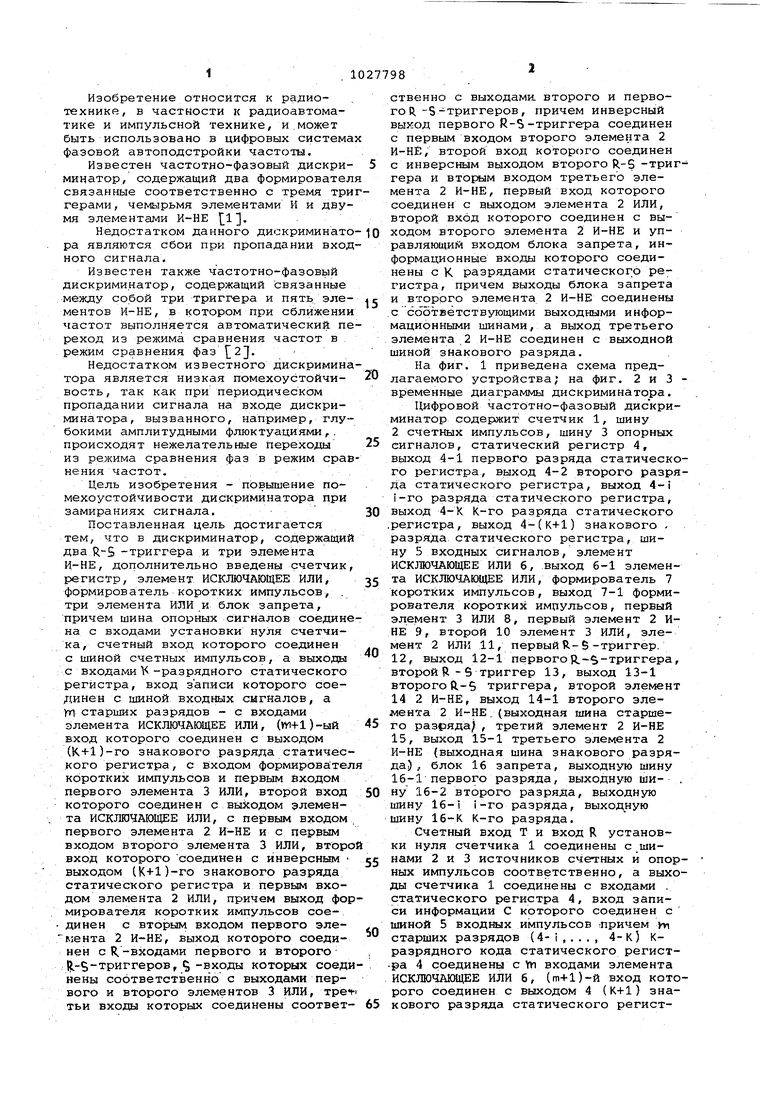

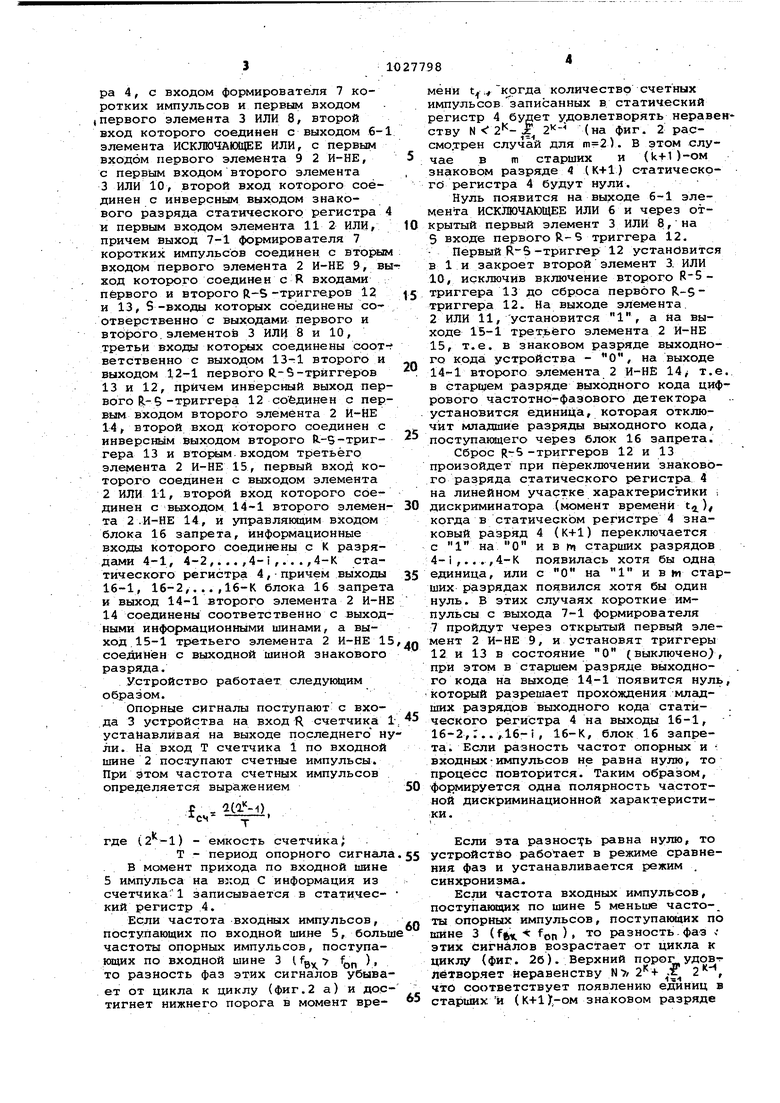

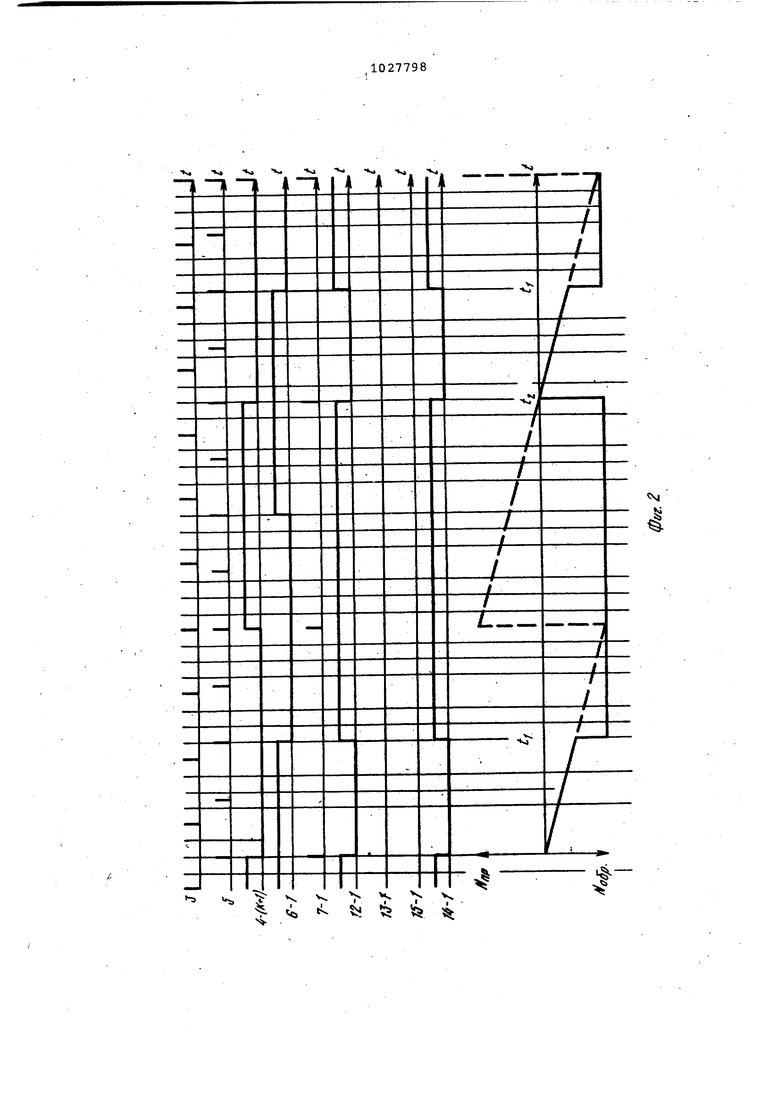

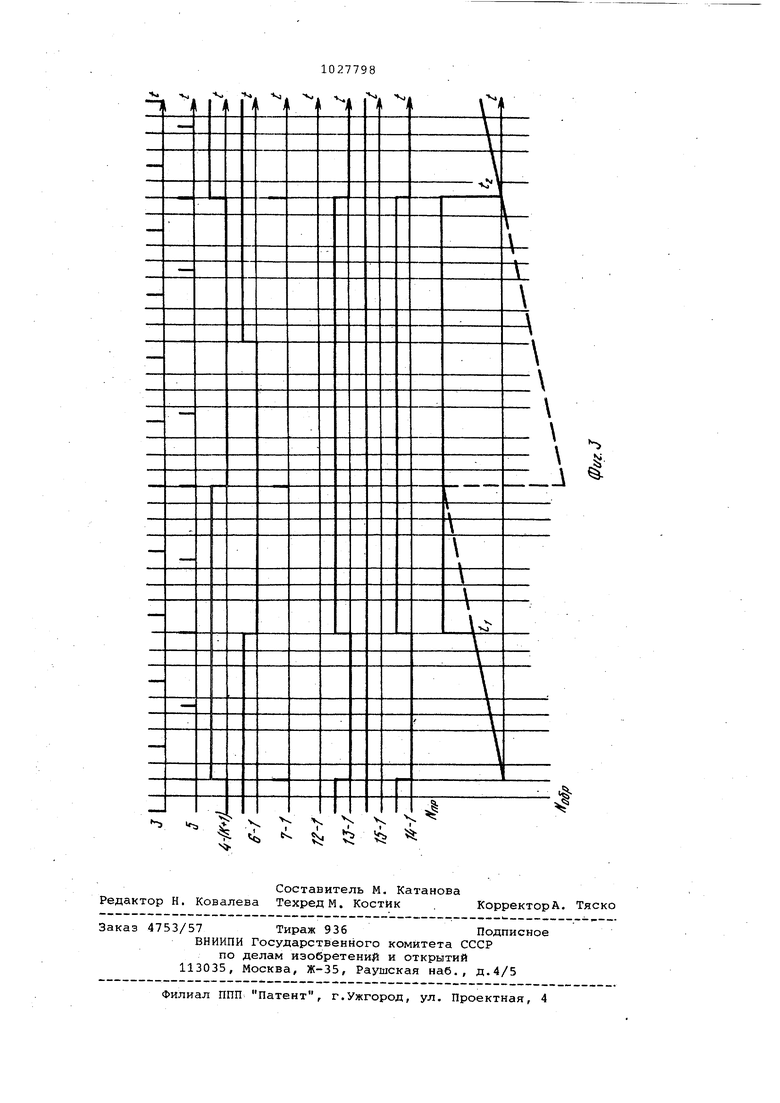

Изобретение относится к радиотехнике, в частности к радиоавтоматике и импульсной технике, и.может быть использовано в цифровых система фазовой автоподстройки частоты. Известен частотно-фазовый дискриминатор, содержащий два формировател связанные соответственно с тремя три герами, чемырьмя элементами И и двумя элементами И-НЕ 1. Недостатком данного дискриминато ра являются сбои при пропадании вход ного сигнала. Известен также частотно-фазовый дискриминатор, содержащий связанные между собой три триггера и пять элементов , в котором при сближении частот выполняется автоматический пе реход из режима сравнения частот в , режим сравнения . Недостатком известного дискримина тора является низкая помехоустойчивость , Так как при периодическом пропадании сигнала на входе дискриминатора, вызванного, например, глубокими амплитудными флюктуациями,. происходят нежелательные переходы из режима сравнения фаз в режим срав нения частот., Цель изобретения - повышение помехоустойчивости дискриминатора при замираниях сигнала. Поставленная цель достигается тем, что в дискриминатор, содержащий два R.-S -триггера и три элемента И-НЕ, дополнительно введены счетчик регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь коротких импульсов, . три элемента ИЛИ и блок запрета, причем шина опорных сигналов соедине на с входами установки нуля счетчика, счетный вход которого соединен с шиной счетных импульсов, а выходы с входами К-разрядного статического регистра, вход записи которого соединен с шиной входных сигналов, а М старших разрядов - с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (УУИ-1)-ый вход которого соединен с выходом (К+1)-го знакового разряда статичес кого регистра, с входом формировател коротких импульсов и первым входом первого элемента 3 ИЛИ, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, С первым входом первого элемента 2 И-НЕ и с первым входом второго элемента 3 ИЛИ, второ вход которого соединен с инверсным выходом (К+1)-го знакового разряда статического регистра и первым входом элемента 2 ИЛИ, причем выход фор мирователя коротких импульсов соединен с вторым входом первого элемента 2 И-НЕ, выход которого соединен с R-входами первого и второго DL-S-триггеров, 9 ВХОДЫ которых соед нены соответственно с выходами первого и второго элементов 3 ИЛИ, тре Тьи входы которых соединены соответ ственно с выходами, второго и первого R. -S -триггеров , причем инверсный выход первого R-S-триггера соединен с первым входом второго элемента 2 И-НЁ, второй вход которс5го соединен с инверсным выходом второго R-S -триггера и вторым входом третьего элемента 2 И-НЕ, первый вход которого соединен с выходом элемента 2 ИЛИ, второй вход которого соединен с выходом второго элемента 2 И-НЕ и управляющий входом блока запрета, информационные входы которого соединены с К разрядами статического регистра, причем выходы блока запрета и второго элемента 2 И-НЕ соединены с соответствующими выходными информационными шинами, а выход третьего элемента 2 И-НЕ соединен с выходной шиной знакового разряда. На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 и 3 временные диаграммы дискриминатора. Цифровой частотно-фазовый дискриминс1тор содержит счетчик 1, шину 2 счетных импульсов, шину 3 опорных сигналов, статический регистр 4, выход 4-1 первого разряда статического регистра, выход 4-2 второго разряда статического регистра, выход 4-i i-ro разряда статического регистра, выход 4-К К-го разряда статического регистра, выход 4-(К+1) знакового разряда статического регистра, шину 5 входных сигналов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ б, выход 6-1 элемента ИСКЛЮЧАКЛЦЕЕ ИЛИ, формирователь 7 коротких импульсов, выход 7-1 формирователя коротких импульсов, первый элемент 3 ИЛИ 8, первый элемент 2 ИНЕ 9, второй 10 элемент 3 ИЛИ, элемент 2 ИЛИ 11, первый R-В-триггер. 12, выход 12-1 первогоД.- -триггера, второйR-S триггер 13, выход 13-1 второго ft.-5 триггера, второй элемент 14 2 И-НЕ, выход 14-1 второго элемента 2 И-НЕ.(выходная шина старшего разряда), третий элемент 2 И-НЕ 15, выход 15-1 третьего элемента 2 И-НЕ (выходная шина знакового разряда) , блок 16 запрета, выходную шину 16-1 первого разряда, выходную ши- . ну 16-2 второго разряда, выходную шину 16-1 i-ro разряда, выходную шину 16-К К-го разряда. Счетный вход Т и вход R установки нуля счетчика 1 соединены с шинами 2 и 3 источников счетных и опорных импульсов соответственно, а выходы счетчика 1 соединены с входами . статического регистра 4, вход записи информации С которого соединен с шиной 5 входных импульсов лричем vi старших разрядов (4-i 4-К) Кразрядного кода статического регистра 4 соединены с Yn входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б, (т+1)-й вход которого соединен с выходом 4 (К+1) знакового разряда статического регистpa 4, с входом формирователя 7 коротких импульсов и первым входом (Первого элемента 3 ИЛИ 8, второй вход которого соединен с выходом 6элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом первого элемента 9 2 И-НЕ, с первым входом второго элемента 3 ИЛИ 10, второй вход которого соединен с инверсным выходом знакового разряда статического регистра и первым входом элемента 11 2 ИЛИ, причем выход 7-1 формирователя 7 коротких импульсов соединен с ВТОЕЖ входом первого элемента 2 И-НЕ 9, в ход которого соединен с R входами первого и второго R-S-триггеров 12 и 13, 5-входы которых соединены соотверственно с вых;одами первого и второго.элементов 3 ИЛИ 8 и 10, третьи входы которых соединены соот ветственно с выходом второго и выходом 12-1 первого ft.-5-триггеров 13и 12, причем инверсный выход пер вого R-S -триггера 12 соёдинен с пер вым входом второго элемента 2 И-НЕ 1:4, второй вход которого соединен с инверсным выходом второго Й.-9-триггера 13 и вTOftiM. входом третьего элемента 2 И-НЕ 15, первый вход которого соединен с выходом элемента 2 ИЛИ 11, второй вход которого соединен с выходом 14-1 второго элемен та 2 .И-НЕ 14, и управляющим входом блока 16 запрета, информационные входы которого соединены с К разрядами 4-1, 4-2,.,.,4-i,...,4-К статического регистра 4, причем выходы 16-1, 16-2,...,16-К блока 16 запрет и выход 14-1 второго элемента 2 И-Н 14соединены соответственно с выход ными информационными шинами, а выход 15-1 третьего элемента 2 И-НЕ 1 соединён с выходной шиной знакового разряда. Устройство работает следующим образом. Опорные сигналы поступают с входа 3 устройства на вход Я счетчика устанавливая на выходе последнего Н ли. На вход Т счетчика 1 по входной шине 2 поступают счетные импульсы. При этом частота счетных импульсов определяется выражением f ) Л/чо--I где (2-1) - емкость счетчика; . Т - период опорного сигнал В момент прихода по входной шине 5 импульса на вход С информация из счетчика 1 записывается в статический регистр 4. Если частота входных импульсов, поступающих по входной шине 5, боль частоты опорных импульсов, поступающих по входной шине 3 ( оп то разность фаз этих сигналов убыва ет от цикла к циклу (фиг.2 а) и дос тигнет нижнего порога в момент врекогда количество счетных импульсов/записанных в статический регистр 4 будет удовлетворять неравенству .F (на фиг. 2 рассмо.трен случай для ). В этом случае в m старших и (k+1)-ом знаковом разряде 4 (К+1) статического регистра 4 будут нули. Нуль появится на выходе 6-1 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и через открытый первый элемент 3 ИЛИ 8,на 5 входе первого R-9 триггера 12. Первый R-S-триггер 12 установится в 1 и закроет второй элемент 3. ИЛИ 10, исключив включение второго триггера 13 до сброса первого R-Sтриггера 12. На выходе элемента 2 ИЛИ 11, установится 1, а на выходе 15-1 третьего элемента 2 И-НЕ 15, т.е. в знаковом разряде выходного кода устройства - О, на выходе 14-1 второго элемента 2 И-НЕ 14/ т.е. в старшем разряде выходного кода цифрового частотно-фазового детектора установится единица, которая отключит младшие разряды выходного кода, поступающего через блок 16 запрета. Сброс R-S -триггеров 12 и 13 произойдет при переключении знакового разряда статического регистра 4 на линейном участке характеристики ; дискриминатора (момент времени t) когда в статическом регистре 4 знаковый разряд 4 (К+1) переключается с 1 на О и в m старших разрядов 4-i,...,4-К появилась хотя бы одна с О на 1 и в м старединица, или ших разрядах появился хотя бы один нуль. В этих случаях короткие импульсы с -выхода 7-1 формирователя 7 пройдут через открытый первый элемент 2 И-НЕ 9, и установят триггеры 12 и 13 в состояние О (выключено), при этом в старшем разряде выходного кода на выходе 14-1 появится нуль, котоЕДЛй разрешает прохождения младших разрядов выходного кода статического регистра 4 на выходы 16-1, 16-2,:..,16-i, 16-К, блок 16 запрета. Если разность частот опорных и входныхимпульсов не равна нулю, то процесс повторится. Таким образом, формируется одна полярность частотной дискриминационной характеристиЕсли эта разность равна нулю, то устройство работает в режиме сравнения фаз и устанавливается режим , синхронизма. Если частота входных импульсов, поступакнцих по шине 5 меньше часто- ты опорных импульсов, поступающих по вшне 3 (ffcu. оп Ь то разность, фаз чэтих сигналов возрастает от цикла к циклу (фиг. 26). Верхний порог удов-г лётворяет неравенству N .г| , что соответствует появлению единиц в старшихИ (К+1У-ОМ знаковом разряде статического регистра 1, В этом случае второй ft,-в-триггер 13 включен, а первый Ив-триггер 12 выключен, В старшем разряде выходного кода на выходе 14-1 устройства уст навливается 1 и в знаковом разря де на выходе 15-1 - 1, при этом ..младшие разряды выходного кода отключены. Таким образом, формируется другой знак частотной дискриминационной характеристики. КоличестйЬ старших разрядов, со диненных с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, позволяет произ водить регулировку диапазона линей ного участка фазовой характеристики в режиме сравнения фаз. 98 В режиме синхронизма фаза опорного сигнала сдвинута относительно фазы входного сигнала; При необходимости этот сдвиг можно скомпенсировать в цепи опорного сигнала. При пропадании входных импульсов, поступающих по шине 5 в режиме синхронизма, прекращается перепись информации о разности ф,аз опорных и входных импульсов из счетчика 1 в статический регистр 4 и цифровой частотно-фазовый детектор переходит в режим памяти. Таким образом, цифровой частот- , но-фазовый детектор .обладает высо- . кой помехоустойчивостью при замираниях входного сигнала, что расширяет область его использования.

V -ч. V. -vj -v V.

ii

I

г

€

+

+

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотно-фазовый дискриминатор | 1983 |

|

SU1117824A1 |

| Цифровой частотно-фазовый дискриминатор | 1984 |

|

SU1256139A1 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1363431A2 |

| Цифровой частотно-фазовый дискриминатор | 1986 |

|

SU1390774A2 |

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1251289A1 |

| Цифровой частотно-фазовый дискриминатор | 1991 |

|

SU1826122A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Способ фазовой автоподстройки частоты управляемого генератора и устройство для его осуществления | 1989 |

|

SU1788576A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

ЦИФРОВОЙ ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР, содержащий два ft-9триггера и три элемента й-йЕ, о т . л и ч а ю щ и я тем, что, с целью повышения помехоустойчивости дискриминатора при замираниях сигнала, в него дополнительно введены счетчик, регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь коротких импульсов, три элемента ИЛИ и блок запре та, причем шина опорных сигналов сое.динена с входами установки нуля с 1етчика, счетный входкоторого соединен с щиной счетных ИМПУЛЬСОВ, а выходы с входами К-фазрядного статического регистра, вход записи которого сое:динен с ШИВОЙ входных сигналов, а Vn старших разрядов - с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (У«-И)-ЫЙ вход которого соединен с выходом (К+1)-го знакового разряда стати,ческого регистра, с входом формирователя коротких импульсов и первым Iвходом первого элемента 3 ИЛИ, вто/,. ..:, ..рой вход которого соедкнеи с выходом элемента ИСКЛЮЧАЩЕЕ ИЛИ, с первым входом первого элемента 2 И-НЕ и с первым входом второго элемента 3 ИЛИ, второй вход которого соединен о инверсным выходом (k+1)-го знакового разряда статического регистра и первым входсм элемента 2 ИЛИ, причем выход формирователя коротких, импульсов соединен с вторьви входом первого элемента 2 И-НЕ, выход которого соединен с R-входами первого и второго R-5 -триггеров,S -входы которых соединены соответственно с выходами первого и второго элементов 3 ИЛИ, третьи входы которых соединены соответственно с выходами второго и первого R-S-триггеров, причем ин(Л версный выход первого R-S-триггера соединен с первым входом второго элемента 2 И-НЕ, второй вход rfoTopoго соединен с инверсным выходом втоporoR-S-триггера и вторьа ч входом третьего элемента 2 И-НЕ, первый вхо, которого соединен с выходом элемента 2 ИЛИ, второй вход которого соединен с выходом второго элемент 2 И-НЕ и управляющим входом блока запрета, инфо1 1ационные входа которого. сйеди : нены с К разрядами статического регистра,. причем выходы блока запрета и второго элемента 2 И-НЕ соедине - ны с соответствукяцимн выходными информационными шинами, а выход третьего элемента 2 И-НЕ соединен с выходной шиной знакового разряда.

I

S S: и

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Частотно-фазовый компаратор | 1974 |

|

SU484621A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-07-07—Публикация

1982-02-08—Подача