(Л

чины резистора в блоке 4 установки режима измерения. В регистрах блока. А хранят коды максимальной и минимальной величин напряжения питания, которые цифроаналоговый преобразователь 9 преобразовывает в напряжение питания подгоняемой цепочки. Коды, соответствующие величинам сопротивлений подгоняемой цепочки, хранят при задании оптимального режима также в регистрах блока 4. Средняя величина сопротивления подгоняемой цепочки сравнивается с текущей величиной сопротивления подгоняемой цепочки, и в момент совпадения этих величин код соответствуняций оптимальному напряжению питания подгоняемой цепочки.

с выхода блока 4 поступает на цифро- аналоговый преобразователь 9. С выхода, цифроаналогового преобразователя 9 оптимальное напряжение питания поступает на магазин кодоуправляеьых резисторов 6 и при оптимальном напряжении питания осуществляет подгонку каждой цепочки магазина кодоуправ- ляемых резисторов 6. Кроме того, устройство содержит блок 2 управления узел 1 подгонки величины сопротивления, схему 3 сравнения, преобразователь 5 сопротивления - код и дешифратор 7, осуществляющий под управлением блока 2 коммутацию соответствующих цепочек магазина 6. 2 з.п. , 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подгонки кодоуправляемых пленочных резисторов | 1975 |

|

SU552642A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Устройство для решения задач теории поля | 1985 |

|

SU1283808A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Кодоуправляемый узел сеточной модели | 1983 |

|

SU1103255A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1462475A1 |

| СПОСОБ ИЗМЕРЕНИЯ И ПОДГОТОВКИ ВЕЛИЧИНЫ СОПРОТИВЛЕНИЯ РЕЗИСТОРОВ | 2003 |

|

RU2249222C1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

Изобретение относится к вычислительной технике и может быть использовано для подгонки суммарного сопротивления кодоуправляекых пленочных резисторов. Изобретение позволяет повысить точность подгонки за счет выбора оптимального режима питания подгоняемой ветви при подгонке вели

1

Изобретение относится к вычислительной технике и мож ет быть использовано для подгонки суммарного сопротивления кодоуправляемых пленочных резисторов.

Целью изобретения является повышение точности подгонки за счет выбора оптимального режима питания подгоняемой ветви при подгонке величины резистора.

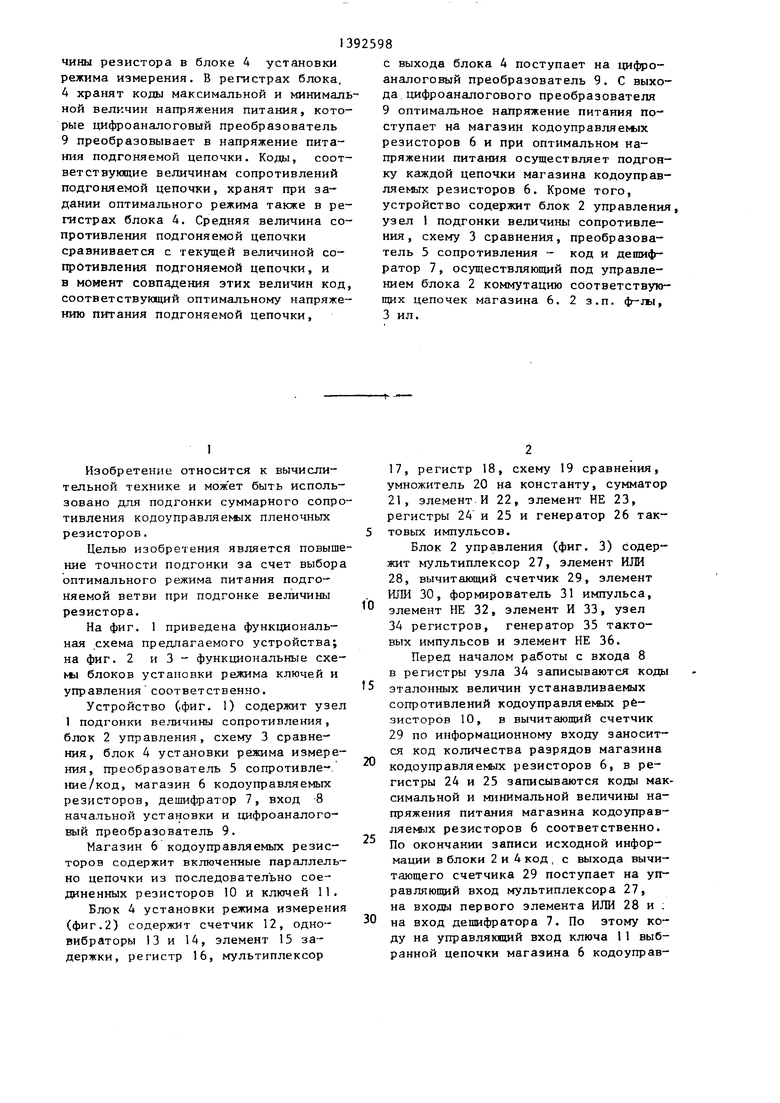

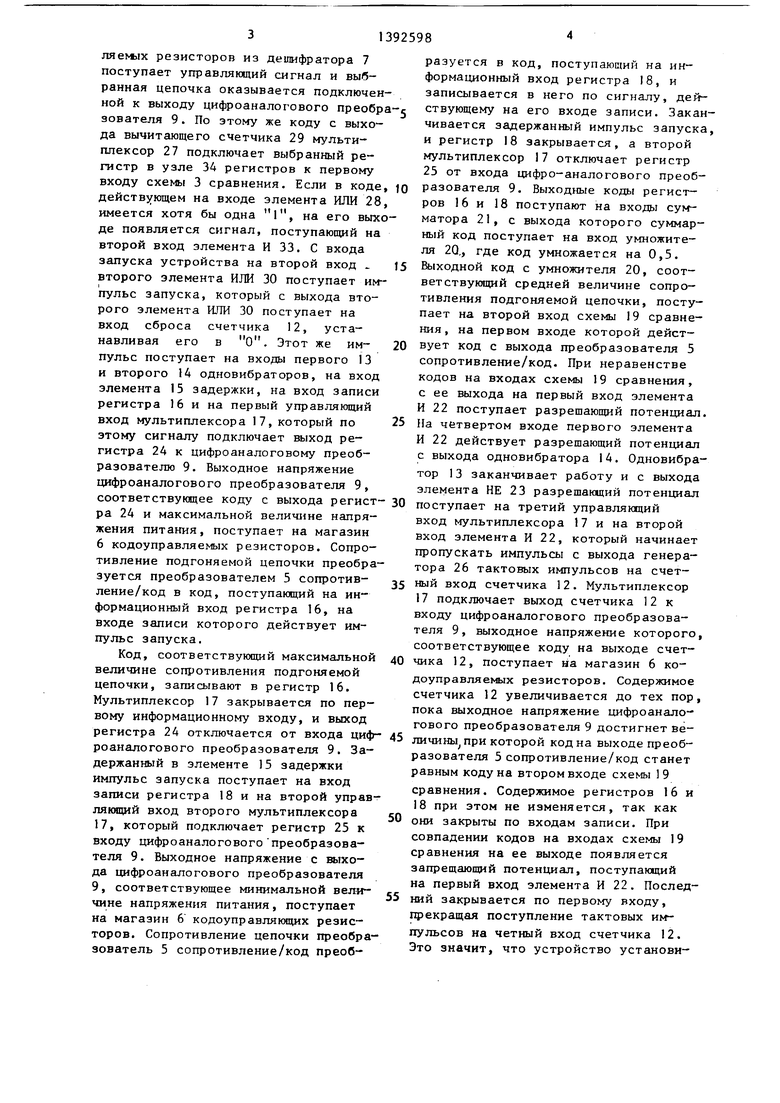

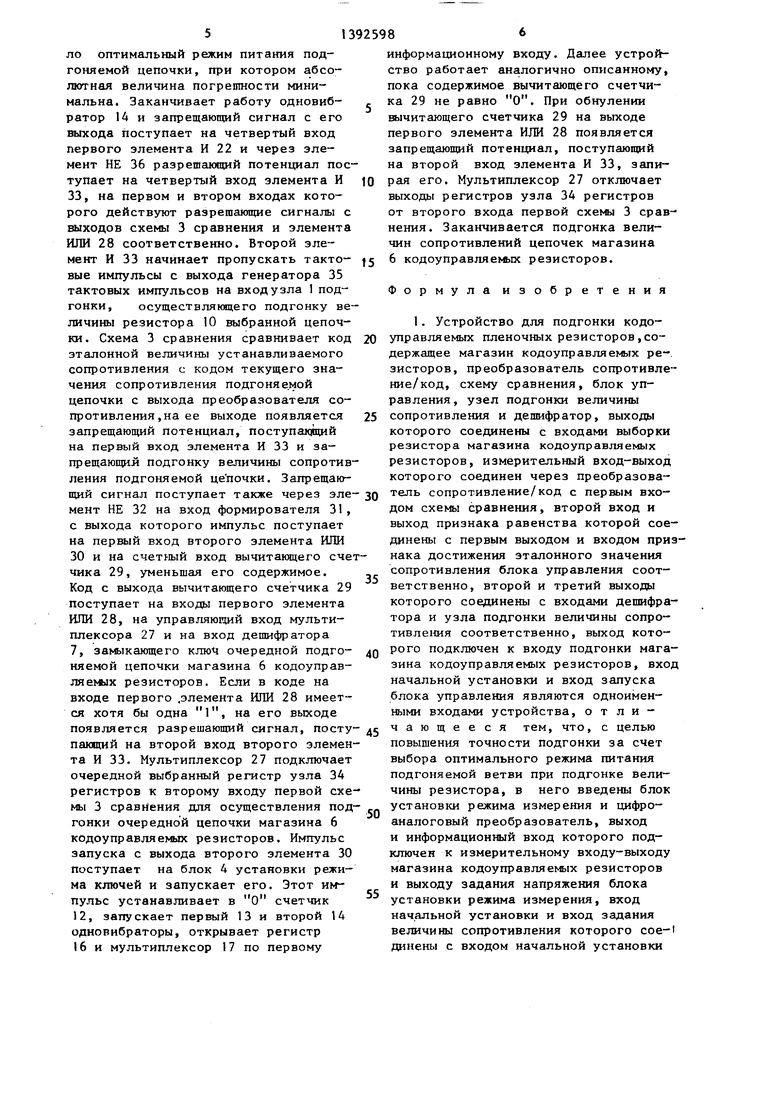

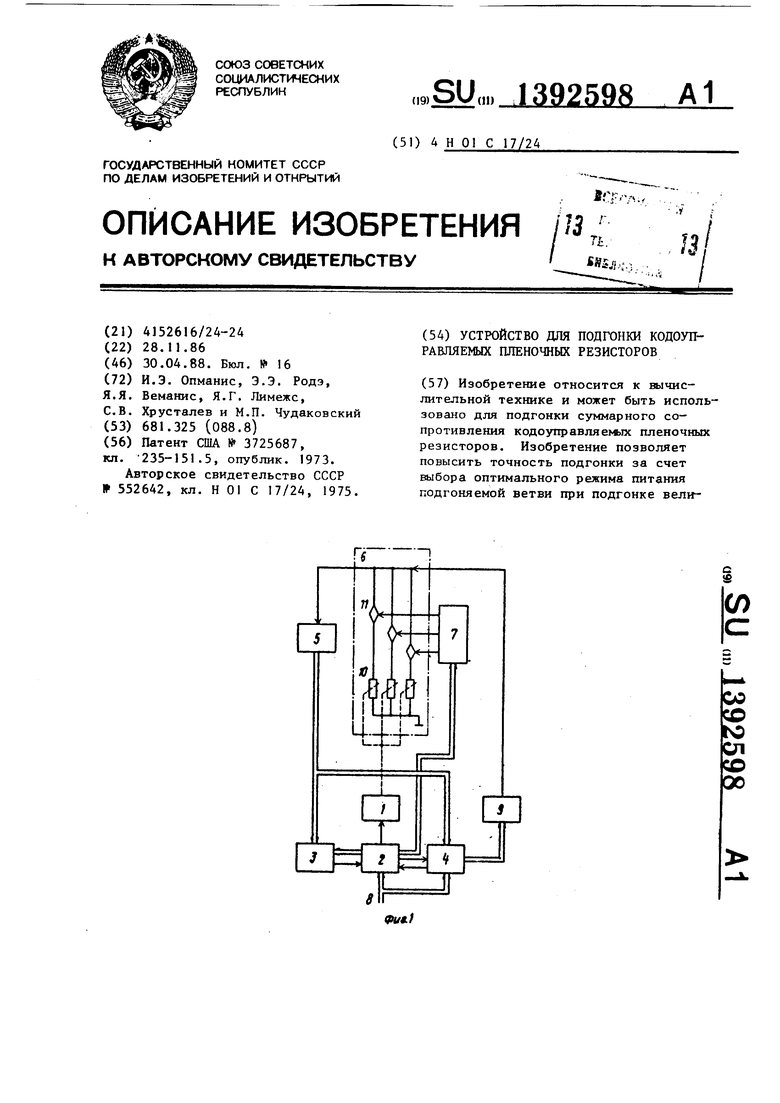

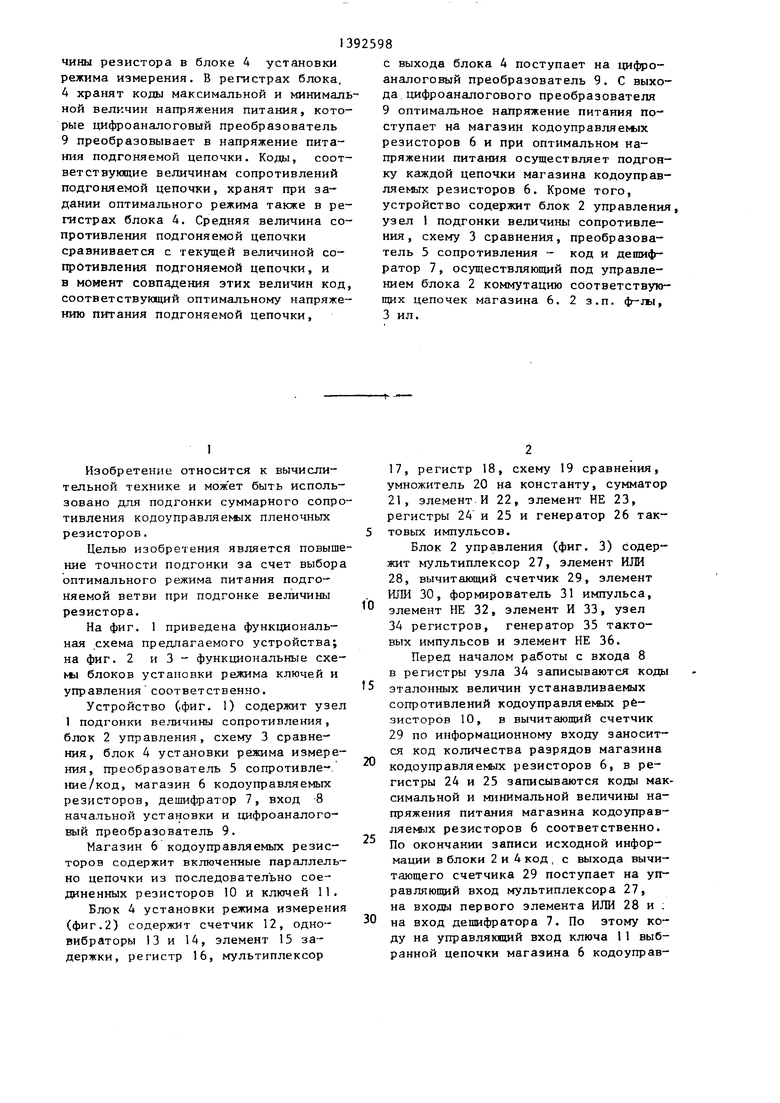

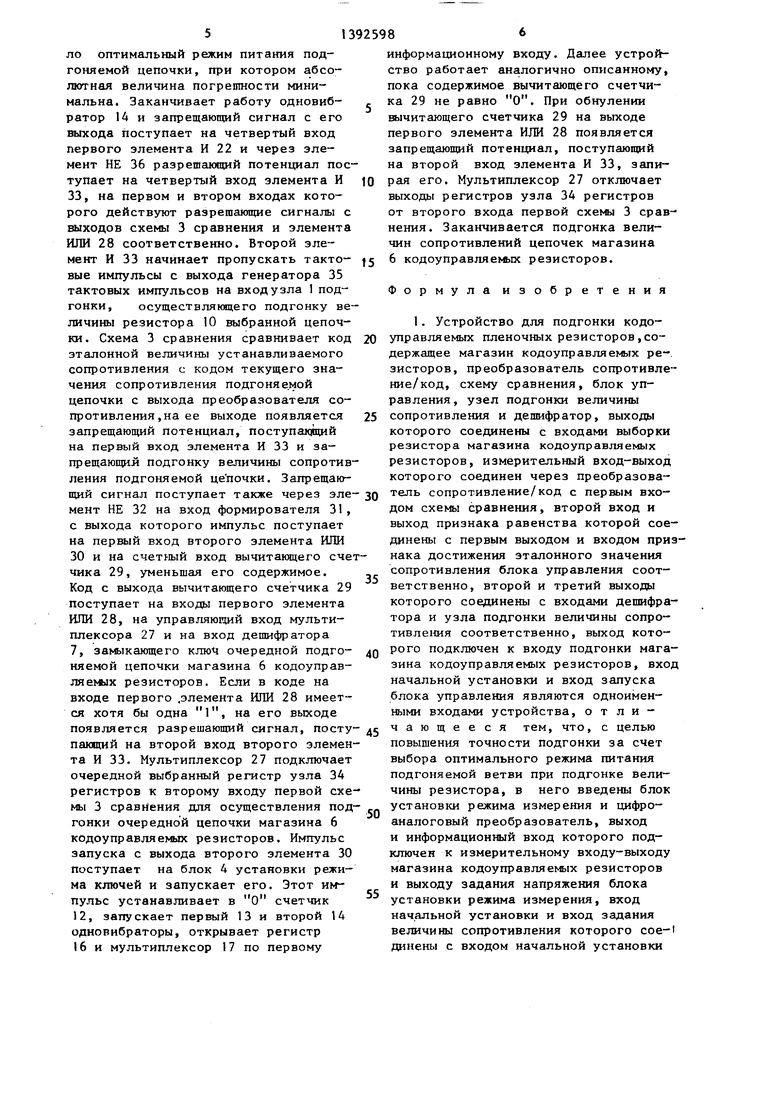

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схе- кы блоков установки режима ключей и управления соответственно.

Устройство Сфиг. 1) содержит узел 1 подгонки величины сопротивления, блок 2 управления, схему 3 сравне- ния, блок 4 установки режима измерения, преобразователь 5 сопротивле-, 1ше/код, магазин 6 кодоуправляемых резисторов, дешифратор 7, вход -8 начальной установки и цифроаналого- вый преобразователь 9.

Магазин 6 кодоуправляемых резисторов содержит включенные параллельно цепочки из последовательно соединенных резисторов 10 и ключей 11,

Блок 4 установки режима измерения (фиг.2) содержит счетчик 12, одно- вибраторы 13 и 14, элемент 15 задержки, регистр 16, мультиплексор

17, регистр 18, схему 19 сравнения, умножитель 20 на константу, сумматор 21, элемент. И 22, элемент НЕ 23, регистры 24 и 25 и генератор 26 тактовых импульсов.

Блок 2 управления (фиг. 3) содержит мультиплексор 27, элемент ИЛИ 28, вычитающий счетчик 29, элемент ИЛИ 30, формирователь 31 импульса,

элемент НЕ 32, элемент И 33, узел 34 регистров, генератор 35 тактовых импульсов и элемент НЕ 36.

Перед началом работы с входа 8 в регистры узла 34 записываются коды

эталонных величин устанавливаемых сопротивлений кoдoyпpaвляe ыx резисторов 10, в вычитающий счетчик 29 по информационному входу заносится код количества разрядов магазина

кодоуправляемых резисторов 6, в регистры 24 и 25 записываются коды максимальной и минимальной величины напряжения питания магазина кодоуправляемых резисторов 6 соответственно. По окончании записи исходной информации в блоки 2 и 4 код , с выхода вычитающего счетчика 29 поступает на управляющий вход мультиплексора 27, на входы первого элемента ИЛИ 28 и ;

на вход дешифратора 7. По этому коду на управляющий вход ключа 11 выбранной цепочки магазина 6 кодоуправляекых резисторов из дешифратора 7 поступает управляющий сигнал и выбранная цепочка оказывается подключенной к выходу цифроаналогового преобра зователя 9. По этому же коду с выхода вычитающего счетчика 29 мультиплексор 27 подключает выбранный регистр в узле 34 регистров к первому входу схемы 3 сравнения. Если в коде действующем на входе элемента ИЛИ 28 имеется хотя бы одна 1, на его выходе появляется сигнал, поступающий на второй вход элемента И 33. С входа запуска устройства на второй вход второго элемента ИЛИ 30 поступает импульс запуска, который с выхода второго элемента ИЛИ 30 поступает на вход сброса счетчика 12, устанавливая его в О. Этот же им- пульс поступает на входы первого 13 и второго 14 одновибраторов, на вход элемента 15 задержки, на вход записи регистра 16 и на первый управляющий вход мультиплексора 17, который по этому сигналу подключает выход регистра 24 к цифроаналоговому преобразователю 9. Выходное напряжение цифроаналогового преобразователя 9, соответствукнцее коду с выхода регист- ра 24 и максимальной величине напряжения питания, поступает на магазин 6 кодоуправляемых резисторов. Сопротивление подгоняемой цепочки преобразуется преобразователем 5 сопротив- ление/код в код, поступающий на информационный вход регистра 16, на входе записи которого действует импульс запуска.

Код, соответствующий максимальной величине сопротивления подгоняемой цепочки, записывают в регистр 16. Мультиплексор 17 закрывается по первому информационному входу, и выход регистра 24 отключается от входа циф- роаналогового преобразователя 9. Задержанный в элементе 15 задержки импульс запуска поступает на вход записи регистра 18 и на второй управляющий вход второго мультиплексора 17, который подключает регистр 25 к входу цифроаналогового преобразователя 9. Выходное напряжение с выхода цифроаналогового преобразователя 9, соответствующее минимальной вел-и чине напряжения питания, поступает на магазин 6 кодоуправляющих резисторов. Сопротивление цепочки преобразователь 5 сопротивление/код преобразуется в код, поступающий на информационный вход регистра 18, и записывается в него по сигналу, действующему на его входе записи. Заканчивается задержанный импульс запуска и регистр 18 закрывается, а второй мультиплексор 17 отключает регистр 25 от входа цифро-аналогового преобразователя 9. Выходные коды регистров 16 и 18 поступают на входы сумматора 21, с выхода которого суммарный код поступает на вход умножителя 2Q., где код умножается на 0,5. &11ХОДНОЙ код с умнояштеля 20, соответствующий средней величине сопротивления подгоняемой цепочки, поступает на второй вход схемы 19 сравнения, на первом входе которой действует код с выхода преобразователя 5 сопротивление/код. При неравенстве кодов на входах схемы 19 сравнения, с ее выхода на первый вход элемента И 22 поступает разрешающий потенциал На четвертом входе первого элемента И 22 действует разрешающий потенциал с выхода одновибратора 14. Одновибра тор 13 заканчивает работу и с выхода элемента НЕ 23 разрешающий потенциал поступает на третий управляющий вход мультиплексора 17 и на второй вход элемента И 22, который начинает пропускать импульсы с выхода генератора 26 тактовых импульсов на счетный вход счетчика 12. Мультиплексор

17подключает выход счетчика 12 к входу цифроаналогового преобразователя 9, выходное напряжение которого соответствующее коду на выходе счетчика 12, поступает на магазин 6 кодоуправляемых резисторов. Содержимое счетчика 12 увеличивается до тех пор пока выходное напряжение цифроаналогового преобразователя 9 достигнет величины при которой код на выходе преобразователя 5 сопротивление/код станет равным коду на втором входе схемы 19 сравнения. Содержимое регистров 16 и

18при этом не изменяется, так как они закрыты по входам записи. При совпадении кодов на входах схемы 19 сравнения на ее выходе появляется запрещающий потенциал, поступающий

на первый вход элемента И 22. Последний закрывается по первому входу, црекращая поступление тактовых импульсов на четный вход счетчика 12. Это значит, что устройство установи-

информационному входу. Далее устройство работает аналогично описанному, пока содержимое вычитающего счетчика 29 не равно О. При обнулении вычитающего счетчика 29 на выходе первого элемента ИЛИ 28 появляется запрещающий потенциал, поступающий на второй вход элемента И 33, запирая его. Мультиплексор 27 отключает выходы регистров узла 34 регистров от второго входа первой схемы 3 сравнения. Заканчивается подгонка величин сопротивлений цепочек магазина

ло оптимальный режим питания подгоняемой цепочки, при котором абсолютная величина погрешности минимальна. Заканчивает работу одновиб- ратор 14 и запрещающий сигнал с его выхода поступает на четвертый вход первого элемента И 22 и через элемент НЕ 36 разрешающий потенциал поступает на четвертый вход элемента И to 33, на первом и втором входах которого действуют разрешающие сигналы с выходов схемы 3 сравнения и элемента ИЛИ 28 соответственно. Второй элемент И 33 начинает пропускать такто- 15 6 кодоуправляемых резисторов, вые импульсы с выхода генератора 35 тактовых импульсов на вход узла 1 подгонки, осуществляющего подгонку величины резистора 10 выбранной цепочки. Схема 3 сравнения сравнивает код эталонной величины устанавливаемого сопротивления с кодом текущего значения сопротивления подгоняемой цепочки с выхода преобразователя сопротивления, на ее выходе появляется запрещающий потенциал, поступающий на первый вход элемента И 33 и запрещающий подгонку величины сопротивления подгоняемой цепочки. Запрещающий сигнал поступает также через эле- зо тель сопротивление/код с первым вхо- мент НЕ 32 на вход формирователя 31, дом схемы сравнения, второй вход и с выхода которого импульс поступает на первый вход второго элемента ИЛИ 30 и на счетный вход вычитающего счетчика 29, уменьшая его содержимое.

20

Формула изобретения

выход признака равенства которой соединены с первым выходом и входом при нака достижения эталонного значения сопротивления блока управления соответственно, второй и третий выходы которого соединены с входами дешифратора и узла подгонки величины сопротивления соответственно, выход которого подключен к входу подгонки магазина кодоуправляемых резисторов, вход начальной установки и вход запуска блока управления являются одноименными входами устройства, о т л и Код с выхода вычитающего счетчика 29 поступает на входы первого элемента ИЛИ 28, на управляющий вход мультиплексора 27 и на вход дешифратора 7, замыкающего ключ очередной подгоняемой цепочки магазина 6 кодоуправляемых резисторов. Если в коде на входе первого .элемента ИЛИ 28 имеется хотя бы одна 1, на его выходе

появляется разрешающий сигнал, посту- д5 чающееся тем, что, с целью пающий на второй вход второго элемен- повышения точности подгонки за счет та И 33. Мультиплексор 27 подключает выбора оптимального режима питания

очередной выбранный регистр узла 34 регистров к второму входу первой схемы 3 сравнения для осуществления подгонки очередной цепочки магазина 6 кодоуправляемых резисторов. Импульс запуска с выхода второго элемента 30 поступает на блок 4 установки режима ключей и запускает его. Этот импульс устанавливает в О счетчик 12, запускает первый 13 и второй 14 одновибраторы, открывает регистр 16 и мультиплексор 17 по первому

информационному входу. Далее устройство работает аналогично описанному пока содержимое вычитающего счетчика 29 не равно О. При обнулении вычитающего счетчика 29 на выходе первого элемента ИЛИ 28 появляется запрещающий потенциал, поступающий на второй вход элемента И 33, запирая его. Мультиплексор 27 отключает выходы регистров узла 34 регистров от второго входа первой схемы 3 сравнения. Заканчивается подгонка величин сопротивлений цепочек магазина

6 кодоуправляемых резисторов, тель сопротивление/код с первым вхо- дом схемы сравнения, второй вход и

6 кодоуправляемых резисторов, тель сопротивление/код с первым вхо- дом схемы сравнения, второй вход и

Формула изобретения

выход признака равенства которой соединены с первым выходом и входом признака достижения эталонного значения сопротивления блока управления соответственно, второй и третий выходы которого соединены с входами дешифратора и узла подгонки величины сопротивления соответственно, выход которого подключен к входу подгонки магазина кодоуправляемых резисторов, вход начальной установки и вход запуска блока управления являются одноименными входами устройства, о т л и

подгоняемой ветви при подгонке величины резистора, в него введены блок установки режима измерения и цифро- аналоговый преобразователь, выход и информационный вход которого подключен к измерительному входу-выходу магазина кодоуправляекых резисторов и выходу задания напряжения блока установки режима измерения, вход начальной установки и вход задания величины сопротивления которого сое-1 динены с входом начальной установки

устройства и выходом преобразователя сопротивление/код соответственно, четвертый выход блока управления подключен к входу запуска блока уста- новки режима измерения, выход признака режима подгонки которого подключен к одноименному входу блока управления .

достижения эталонного значения сопро- 20 И, вход запуска блока соединен с тивления которого соединен с первым входом элемента И и через последовательно соединенные первый элемент НЕ и формирователь импульса с первым входом второго элемента ИЛИ и с счетным входом вычитающего счетчика, выходы которого образуют второй выход блока и соединены с входами первого элемента ИЛИ и с управляювходом сброса счетчика, с входом записи первого регистра, с первым управляющим входом мультиплексор с первым управляющим входом мульт 25 плексора через элемент задержки с входом записи иторого регистра вторым управляющим входом мультиплексора, а через последовательно соединенные первый одновибратор и

щими входами мультиплексора, информа- JQ элемент НЕ - с вторым входом элеменционные входы и выход которого соединены с выходами узла регистров и первым выходом блока соответственно, вход запуска которого и ииход первого элемента ИЛИ соединены с вторыми входами второго элемента ИЛИ и элемента И соответственно, выходы которых являются четвертым и третьим выходами блока, выход генератора тактовых импульсов соединен с третьим входом элемента И, четвертый вход которого соединен через второй элемент НЕ с входом признака режима подгонки блока. 3. Устройство по п. 1, о т л и чающееся тем, что блок. уста-д5 режима подгонки блока.

новки режима изменения содержит четыре регистра, сумматор, умножитель на константу, схему сравнения, генератор тактовых импульсов, элемент И, два одновибратора, элемент задержки, элемент НЕ и счетчик, вход зада-, ния величины сопротивления блока соединен с информационными входами первого и второго регистров и с первым входом схемы сравнения, выходы первого и второго регистров соединены с входами первого и второго слагаемого сумматора, выход которого соединен с информационным входом умножителя на константу, выход которого соединен с вторым входом схемы сравнения, выход признака равенства которой подключен к первому входу элемента

И, вход запуска блока соединен с

входом сброса счетчика, с входом записи первого регистра, с первым управляющим входом мультиплексора, с первым управляющим входом мульти- плексора через элемент задержки - с входом записи иторого регистра и вторым управляющим входом мультиплексора, а через последовательно соединенные первый одновибратор и

5

0

та И и третьим управляющим входом мультиплексора, с первого по третий информационные входы и выход которого соединены с выходами третьего, четвертого регистров, счетчика и выходом задания напряжения блока соответственно, информационные входы третьего и четвертого регистров образуют вход начальной установки блока, выход генератора тактовых импульсов соединен с третьим входом элемента И, вход запуска блока соединен через второй одновибратор с четвертым входом элемента И и выходом приз /r je

.

I

Sm 31

tmJ

| Патент США № 3725687, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Устройство для подгонки кодоуправляемых пленочных резисторов | 1975 |

|

SU552642A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-30—Публикация

1986-11-28—Подача