входу второго счетчика, выход первого блока задержки Соединен с вторым входом второго элемента И, nepBbtft, второй, третий, четвертый и пятый выходы первого блока синхронизации подключены соответственно ко второму

входу пятого элемента ИЛИ, к третьему входу пятого элемента ИЛИ, к второму входу четвертого элемента ИЛИ, к третьему входу четвертого элемента ИЛИ и к второму входу третьего элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Устройство для ввода информации | 1983 |

|

SU1113793A1 |

| Информационное устройство стеллажного склада | 1986 |

|

SU1364585A1 |

КОДОУПРАВЛЯЕМЬт УЗЕЛ СЕТОЧНОЙ МОДЕЛИ, содержащий R-сетку, . два блока памяти, три регистра и два элемента И, отличающийся тем, что, с целью повьшения точности, в него введены пять элементов ИЛИ, два счетчика, блок задержки, два блока синхронизации, два-формирователя прямоугольных импульсов, мультиплексор, шифратор и генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, выход которого соединен с входом сдвига первого регистра и со счетным входом первого счетчика, знаковый выход которого подключен к входу направления сдвига первого регистра, выход которого соединен с информационным входом первого блока памяти, выход которого соединен с входами задания параметров R -сетки, вход записи данньк устройства подключен к информационному входу второго блока памяти, выход которого соединен с разрядными входами второго и третьего регистров, выходы которых подключены к разряднь1м входам Соответственно Первого регистра и первого счетчика, адресный вход устройства соединен с первым входом первого t.;Huti,, элемента ИЛИ и с первым информационным входом мультиплексора, выход которого подключен к адресному входу второго блока памяти, вход разрешения работы которого соединен с выходом первого элемента ИЛИ, вход пуска устройства соединен с вторым входом первого элемента ИЛИ, с управляющим входом мультиплексора, с входами блока задержки и первого формирователя прямоугольных импульсов, выход которого подключен к входу первого блока синхронизации и к установочному входу второго счетчика, выход которого соединен с вторым информационным входом мультиплексора и со входом шифk/) ратора, выход которого подключён к первому входу второго элемента И, выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с выходом второго элемента ИЛИ и с входом второго формирователя прямоугольных импульсов, выход которого подключен к управляющему входу первого блока памяти и к входу второго блока синхронизации, первый выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к входам разрешения записи первого регистра и первого счетчика, группа информационных выходов которого подключена. к группе входов второго элемента ИЛИ, второй и третий выходы второго блока синхронизации подключены к первым входам соответственно четвертого и пятого элементов ИЛИ, выход четвертого элемента ИЛИ соединен с входами разрешения записи второго и третьего регистров, выход пятого элемента ИЛИ подключен к счетному

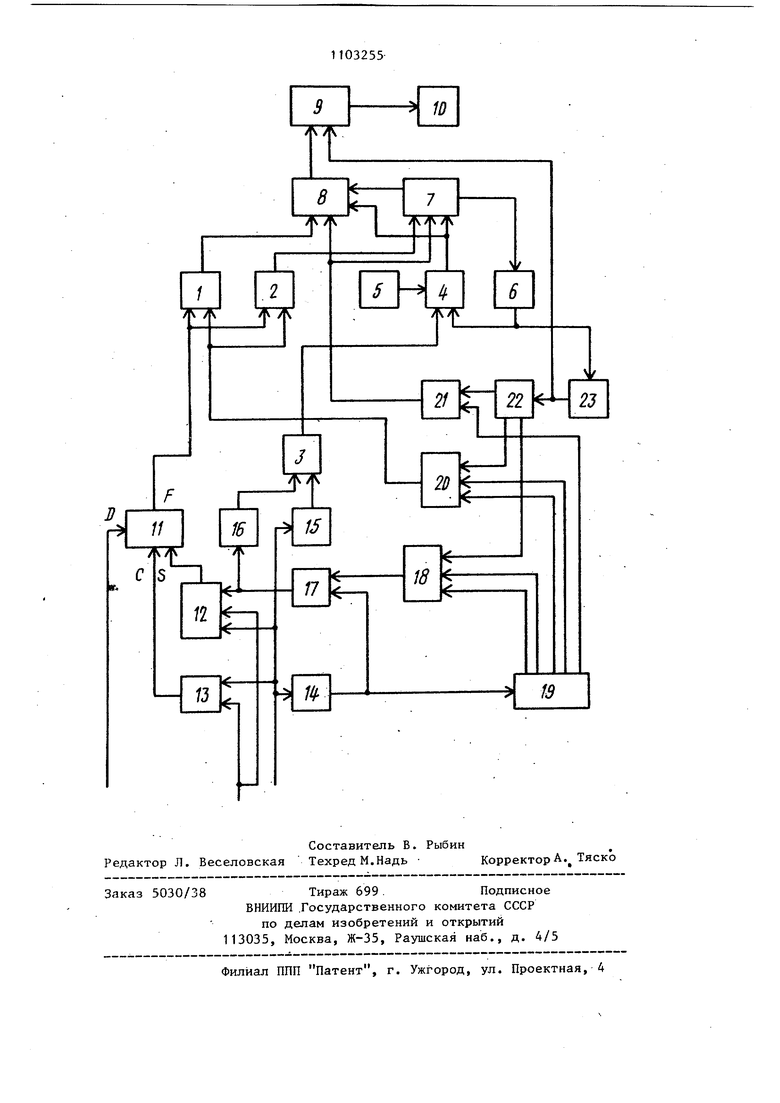

Изобретение относится к вычислительной технике и может быть использовано в специализированных аналоговых вычислительных системах, в сеточных моделях. Известно устройство для моделирования функционального сопротивления содержащее преобразователь код сопротивление, связанный с регистром кода сопротивления, арифметическим блоком и блоком управления, соединенным с блоком памяти и блоком синх ронизации II J. В этом устройстве в процессе эксплуатации в результате разогрева кодоуправляемого сопротивления величина сопротивления изменяется, вызывая изменение напряжения отпирания, приводит к снижению точности задания сопротивления. ,Наиболее близким по техническому решению к предлагаемому является кодоуправляемый элемент сеточной модели, содержащий Р -сетку, два блока памяти, три регистра и два элемента И, блок слежения, блок развязки, программный блок соединен с блоком управления t2. Однако это устройство при задании проводимости в конце диапазона при задании малых величин проводимости имеет значительную относительную погрешность. Целью изобретения является повышение точности задания проводимости в конце диапазона при задании малых величин проводимости. Поставленная цель достигается тем что в кодоуправляемый узел сточной модели, содержащий R-сетку, два бл ка памяти, три регистра и два элемен та И, введены пять элементов И.ПИ, два счетчика, блок задержки, -два блока синхронизации, два формировате ля прямоугольных импульсов, мультиплексор, шифратор и генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, выход которого соединен с входом сдвига первого регистра и со счетньм. входом первого счетчика, знаковый выход которого подключен к входу направления сдвига первого регистра, выход которого соединен с информационным входом первого блока памяти, выход которого соединен с входами задания, параметров R-сетки, вхоД записи данных устройства подключен к информационному входу второго блока памяти, выход которого соединен с разрядными входами второго и третьего регистров, выходы которых подключены к разрядным входам соответственно первого регистра и первого счетчика, адресный вход устройства соединен с первым входом первого элемента ИЛИ и с первым информационным входом мультиплексора, выход которого подключен к адресному входу второго блока памяти, вход разрешения работы которого соединен с выходом первого элемента ИЛИ, вход пуска устройства со)гдинен с вторым входом первого элемента ИЛИ, с управляющим входом мультиплексора, с входами блока задержки и первого формирователя прямоугольных импульсов, выход которого подключен к входу первого блока синхронизации и к установочному входу второго счетчика, выход которого соединен с вторым информационным входом мультиплексора и с входом шифратора, выход которого подключен к первому входу/ второго элемента И, выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с выходом второго элемента ИЛИ и с входом формирователя пря3моугольных импульсов, выход которого подключен к управляющему входу первого блока памяти и к входу второго блока синхронизации, первый выход которого соединен с первым входом третьего элемента ШШ, выход которого подключен к входам разрешения записи первого регистра и первого счетчика, группа информационных выходов которого подключена к группе, входов второго элемента ИЛИ, второй и третий выходы второго блока синхронизации подключены к первым входам соответственно четвертого и пятого элементов ИЛИ, выход четвертого элемента ИЛИ соединен с входами разреше ния записи второго и третьего регистров, выход пятого элемента ИЛИ подключен к счетному входу второго счетчика, выход первого блока задержки соединен с вторым входом второго элемента И, первый, второй, третий, четвертый и пятый выходы пер вого блока синхронизации подключены соответственно к второму входу пятого элемента ИЛИ, к третьему входу пятого элемента ИЛИ, к второму входу четвертого элемента ШШ, к третьему входу четвертого элемента ИЛИ и к второму входу третьего элемента ИЛИ На чертеже представлена схема устройства. Устройство содержит регистры 1 и 2, элементы И 3 и 4, генератор 5 так товых импульсовi элемент ИЛИ 6,счетчик 7, регистр 8, блок 9 памяти, R-сетку 10, блок 11 памяти, мультиплексор 12, элемент ИЛИ 13, формирователь 14 прямоугольных импульсов, блок 15 задержки, шифратор 16, счетчик 17, элемент ИЛИ 18, блок 19 синхронизации, элементы ИЛИ 20 и 21 блок 22 синхронизации, формирователь 23 прямоугольных импульсов. Устройство работает следующим об разом. Перед началом работы в оперативное запоминающее устройство (ОЗУ) в блок 11 памяти записывают массив кодов проводимости в представлении с плавающей запятой. Для этого на вход 1 блока 11 подают записываемый код , на адресный вход через мульти плексор 12 подают адрес, а в момент записи на вход разрешения работы подается импульс с выхода первой схемы ИЛИ 13. 554 После завершения загрузки блока 11 на вход пуска устройства подают уровень Пуск, который поступает на вход первого формирователя 14, через блок 15 задержки на вход элемента И 3 и через элемент ИЛИ 13 на вход разрешения работы блока 11. С выхода, формирователя 14 импульс поступает на вход блока 19 синхронизации и на вход счетчика 17, устанавливая его в исходное состояние. С перйого выхода блока 19 синхронизации импульс поступает.на вход элемента ИЛИ 20 и далее на вторые входы регистров 1 и 2, разрешая запись кодов с выхода блока 11 в регистры 1 и 2. Импульс с второго выхода блока 19 синхронизации через четвертый элемент ИЛИ 21 поступает на входы регистра 8 и реверсивного счетчика 7 соответственно, разрешая перезапись кодов в них. Импульс с третьего выхода блока 19 синхронизации через второй элемент ИЛИ 18 поступает на вход счетчика 17, перебрасывая его в следующее состояние. Содержимое счетчика 17 поступает на второй вход мультиплексора 12 и шифратор 16. Мультиплексор вьдает на адресный вход блока 11 очередной адрес, и на выходе блока 11 появляются новые коды мантиссы и порядка заносимой проводимости. Импульс с четвертого выхода блока 19 синхронизации поступает на вход элемента ИЛИ 20, с выхода которого на входы регистра мантиссы 1 и регистра 2 поступает сигнал разрешения записи. По этому сигналу коды с выхода блока 11 перезаписываются в регистр 1 и в регистр 2. Импульс с пятого выхода блока 19 синхронизации поступает на вход элемента ИЛИ 18 и далее на вход счетчика 17, перебрасывая его в следующее состояние. Содержимое счетчика 17 поступает через мультиплексор 12 на адресный вход блока 11, и на его выходе появляются очередные коды. Шифратор 16 в ответ на сигнал из счетчика 17 выдает потенциал на первый вход элемента И 3, на втором входе которого действует сигнал с выхода блока 15 задержки. С выхода элемента И 3 сигнал поступает на первый вход элемента И 4. Если код порядка, записанный в реверсивный счетчик 7, отличается от нуля, от элемента ИЛИ 6 на третий вход элемента И 4 также поступает разрешающий потенциал. С выхода генератора 5 тактовых импульсов импуль сы, поступаюпще на второй вход элемента И 4, подаются через элемент И 4 на первый вход реверсивного счет чика 7.и на второй вход регистра сдвига 8, сдвигая код мантиссы. Импульсы через элемент И 4 от генерато 5 тактовых импульсов проходят до тех пор, пока содержимое реверсивного счетчика 7 станет равным нулю, при этом на выходе элемента ИЛИ 6 появляется запрещаюпщй потенциал, и элемент И 4 закрывается по третьему входу, прекращая доступ импульсов в регистр 8 и в реверсивньй счетчик 7 и прекращая сдвиг кода. Направление сдвига определяет знаковый разряд реверсивного счетчика 7, действующий на первом входе регистра 8. Запрещающий потенциал с выхода элемента ИЛИ 6 поступает также на вход формирователя 23, с выхода которого на первьш вход блока 9 памяти поступает импульс, разрешения записи. Сдвинутый код мантиссы с выхода регистра 8 поступает на второй вход блока 9 памяти и под воздействием импульса разрешения записи заносится в блок 9 памяти, устанавливая величину проводимости Р сетки 10. Импульс с выхода второго формирователя 23 поступает также на вход 6jioKa 22 синхронизации. С первого выхода блока 22 импульс поступает на второй вход четвертого элемента ИЛИ 21 и далее на четвертый и третий входы регистра 8 и реверсивного счетчика 7 соответственно. П6 этому сигналу осуществляют перезапись содержимого регистра 1 в регистр 8, регистра 2 - в реверсивный счетчик 7. Импульс с второго выхода блока 22 поступает на третий вход элемента ИЛИ 20 и далее на вторые входы регистров 1 и 2, разрешая перезапись кодов с выхода блока 11,. Импульс с третьего выхода блока 22 поступает на третий вход второго элемента ИЛИ 18 и далее на счетчик 17. Содержимое счетчика 17 поступает на второй вход мультиплексора 12 и шифратор 16. Мультиплексор 12 вьщает на адресньй вход блока 11 очередной адрес, и на выходе блока 11 появляются очередные коды. Шифратор 16 вьщает на первьй вход элемента 3 разрешающий потенциал, и устройство работает,как описано вьш1е, задавая величину проводимости очередного кодо управляемого элемента сеточной модели, при этом код установленной проводимости в представлении с фиксированной запятой хранится в блоке 9 памяти до следующего обращения к R-сетке 10. Применение изобретения повьш1ает точность решения задачи на сеточной модели и сокращает время подготовки данных перед введением их в память сеточной модели.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1972 |

|

SU417803A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кодоуправляемый элемент сеточной модели | 1975 |

|

SU547790A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-01-11—Подача