BHMoff

СО СО

to

О5 ts9

о:

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи цифровой информации | 1984 |

|

SU1185636A1 |

| Устройство для передачи и приема цифровых сигналов | 1986 |

|

SU1415452A1 |

| Устройство для передачи информации по двухпроводной линии связи | 1987 |

|

SU1496001A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Устройство передачи двоичных сигналов | 1987 |

|

SU1467782A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1985 |

|

SU1368996A1 |

| Устройство для управления многоканальным электроприводом тренажера | 1984 |

|

SU1180846A1 |

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации. Цель изобретения - формирование линейного сигнала (лс) с потенциальной помехоустойчивостью. Формирователь содержит генератор 1 импульсов, делитель 2 частоты импульсов на два, блок 3 хранения информации, элемент И 4, элемент 2И-ИЛИ 5, счетный триггер 6, элемент ИЛИ 7, управляемый суммирующий усилитель (УСУ 8 и согласующий усилитель 9, Цифровая двоичная информация в виде последовательного бинарного сигнала генерируется блоком 3 и поступает в прямом и инверсном виде на элемент 2И-ИЛИ 5. Элемент 2И-ИЛИ 5 перекодирует информационный двоичный сигнал в последовательность импульсов. Счетный триггер 6 формирует биимпульсный ЛС, сдвинутый на четверть такта. При одноименных сигналах на выходах УСУ 8 согласующий усилитель 9 формирует нулевой уровень ЛС, а при разноименных - положит, или отриц, уровень В спектре сформированного ЛС отсутст- .вует постоянная составляющая. Основная энергия ЛС сосредоточена на тактовой частоте. Введены элементы И 4, ИЖ 7. 2 ило СЛ

Фиг. f

Изобретение относится к электросвязи и может быть использовано в системах передачи цифровой информации

Цель изобретения. - формирование линейного сигнала с потенциальной помехоустойчивостьюо

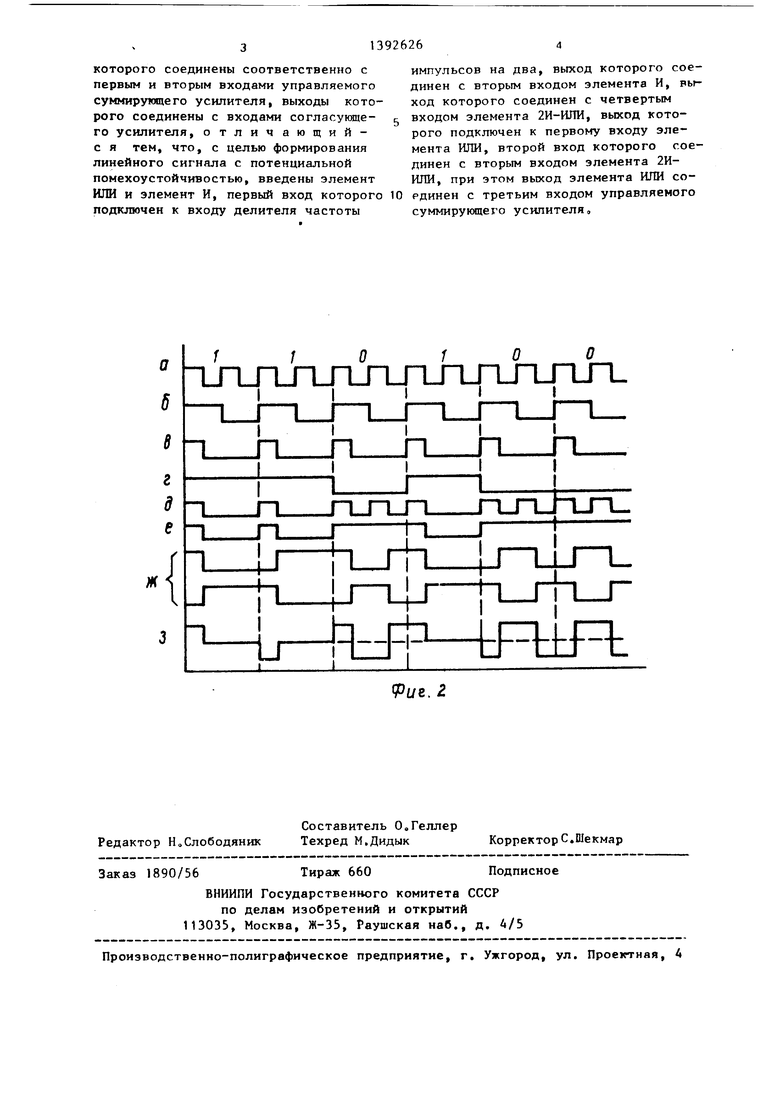

На фиг„1 изображена структурная электрическая схема предлагаемого формирователя; на фиг о2 - временная диаграмма

Формирователь цифрового линейного сигнала содержит генератор 1 импульсов, делитель 2 частоты импульсов на два, блок 3 хранения информации, элемент И 4, элемент 2И-ИЛИ 5 счетный триггер 6, элемент ИЛИ 7, управляемый суьтмируюпщй усилитель 8

и согласующий усилитель 9.

Согласующий усилитель содержит трансформатор 10 и резисторы 11,12,

Формирователь работает следующим образомо

Цифровая двоичная информация, например, содержащая кодовые символы 110100 для одного слова по тактам, формируемым генератором 1 им- 1гульсов (фиГо2а) и делителем 2 частоты импульсов на два (фиГо2б), гене рируется блоком 3 хранения информаци в виде последовательного бинарного сигнала (фиГо2г)о Црямой и инверсный сигналы блока 3 хранения информации поступают на второй и третий входы элемента 2И-ИЛИ 5, на первый вход которого одновременно поступают импульсы эталонной частоты с генератора 1 импульсов (фиго2а), а на четвертый вход - импульсы (фиГо2в), формируемые элементом И АО Элемент 2И-ИЛИ 5 перекодирует информационный двоичный сигнал в последовательность импульсов (фиг.2д)о Счетный триггер 6 формирует биимпульсный линейный сигнал, сдвинутый на четверть такта (фиГс2ж), а элемент ИЛИ 7 суммирует импульсы элемента 2И-ШШ 5 и инверсный информационный сигнал блока 3 (фиг„2е)„ На пер вьй и второй входы управляемого суммирующего усилителя 8 поступает прямой и инверсный биимпульсный сигналы, формируемые счетным триггером 6, а на третий вход - сигнал с элемента ИЛИ 7. В качестве управляемого суммируемого усилителя 8 используется токовый формирователь с логикой на входе, выполняюгдий ло

гическую функцию F , А , С

F.

AJ-C о К выходам F, и Fj подключены входы трансформаторов 10, на выходе которого формируется цифровой линейный сигнал (фиГо2э)о Одновременно трансформатор 10 осуществляет гальваническую развязку линии свяаи. Резисторы 11 и 12 согласования, имеющие сопротивление, равное волновому сопротивлению конкретной линии связи, устраняют переотражения в линии, а также используют как нагрузочные по питанию трансформатора 10,

5

0

5

0

0

При одноименных потенциалах (.одно- Эременно О или +1) на выходах F,F j управляемого суммирующего усилителя 8, на выходе согласующего усилителя 9 - нулевой уровень сигнала, а при разноименных (на одном О, на другом +1) - положительный или отрицательный уровень линейного сигнала.

Сформированный таким образом линейный сигнал (фиг„2з) хорошо согласуется с проводными каналами связи тем, что в энергетическом спектре такого сигнала отсутствует постоянная составляющая; на низких частотах энергия имеет незначительный вес, а основная энергия сосредоточена на тактовой частоте (тактовая частота - частота следования информационных символов); от отношения сигнал/шум на тактовой частоте зависит помехо- 5 устойчивый прием. Такой цифровой сигнал позволяет использовать верхнюю граничную полосу щирокополосного проводного канала, ранее не использованную, и одновременно повысить скорость передачи информации, а также при параллельной передаче на низких частотах других сигналов уменьшить влияние цифрового сигнала на соседние сигналы.

Формула изобретения

Формирователь цифрового линейного сигнала, содержащий генератор импульсов, выход которого соединен с первым входом элемента 2И-ИЛИ и с входом делителя частоты импульсов на два,выход которого соединен с входом блока хранения информации, первый и второй выходы которого подключены соответственно к второму и третьему входам элемента 2И-ИЛИ, выход которого подключен к входу счетного триггера, единичный и инверсный выходы

которого соединены соответственно с первым и вторым входами управляемого суммирующего усилителя, выходы которого соединены с входами согласующего усилителя, отличающий- с я тем, что, с целью формирования линейного сигнала с потенциальной помехоустойчивостью, введены элемент ИЛИ и элемент И, первый вход которого подключен к входу делителя частоты

а 6 S

J1 ог о о

TJ LJTnXlJ LTlJlJTrLJlJ

I

I

ж

-Г 1

1г

импульсов на два, выход которого соединен с вторым входом элемента И, выход которого соединен с четвертым

входом элемента 2И-ИЛИ, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с вторым входом элемента 2И- ИЛИ, при этом выход элемента ИЛИ сординен с третьим входом управляемого суммирующего усипителя.

J-14J

bPttFt

.г

Авторы

Даты

1988-04-30—Публикация

1986-02-13—Подача