Изобретение относится к электросвязи н может быть использовано в цифровых системах связи с различными передающими средами.

Цель изобретения - повышение помехоустойчивости.

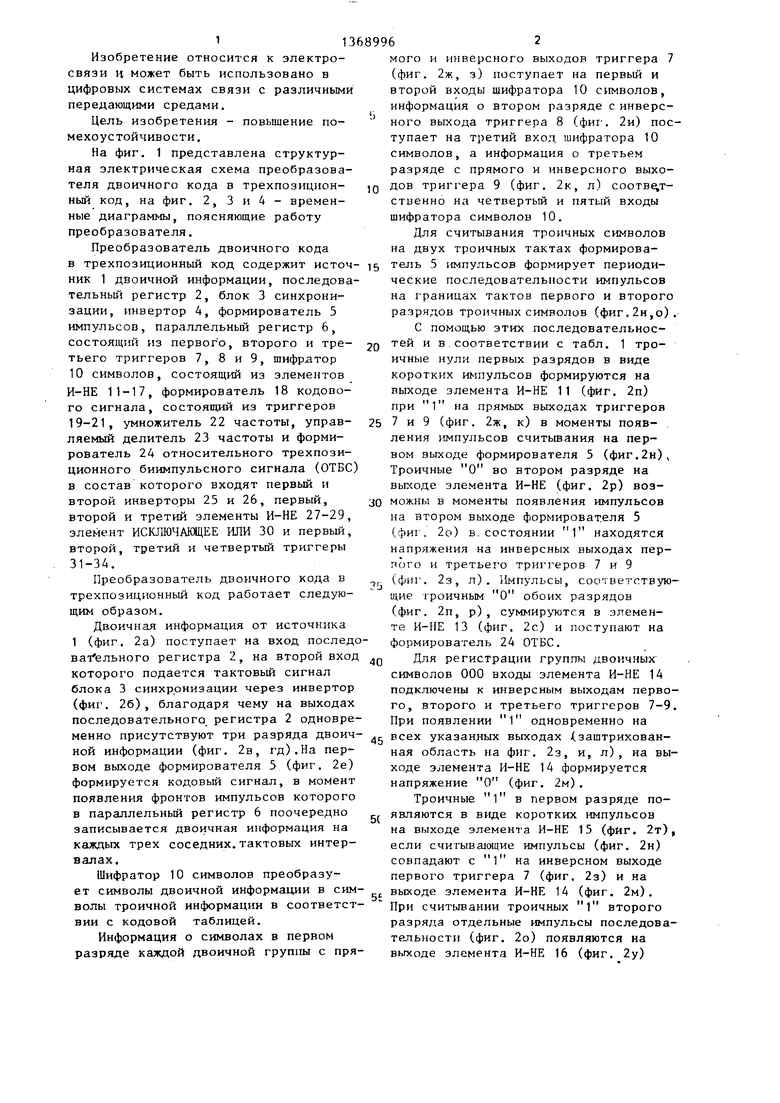

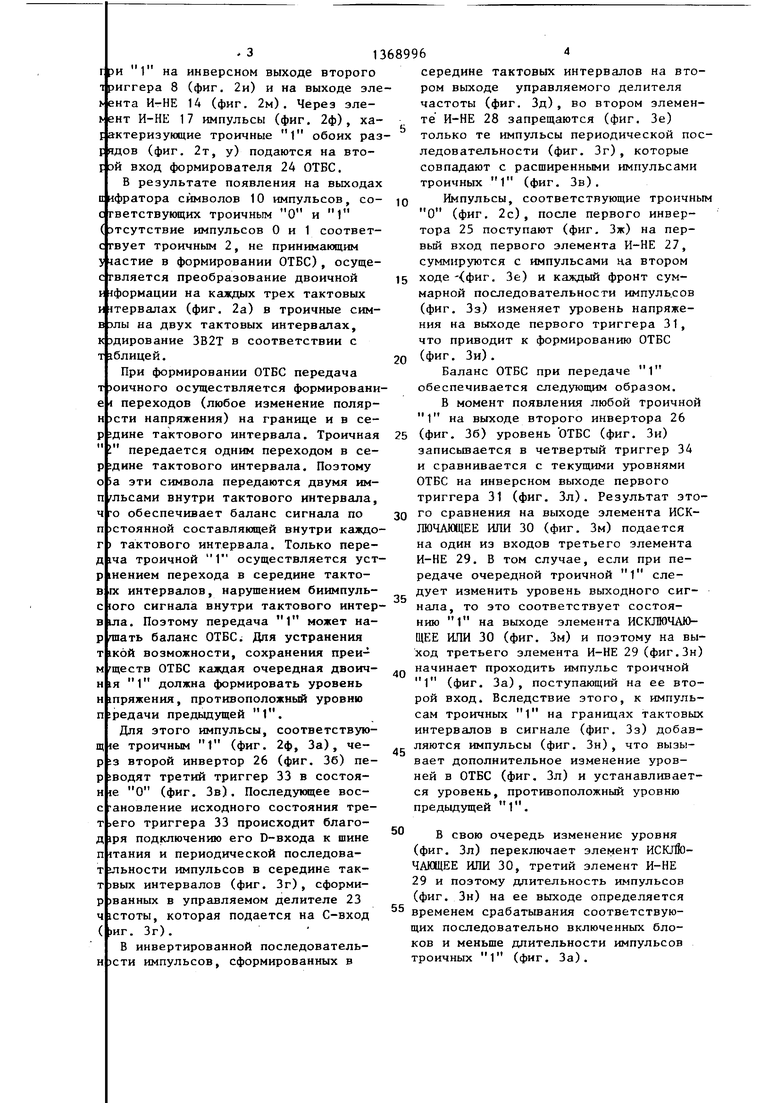

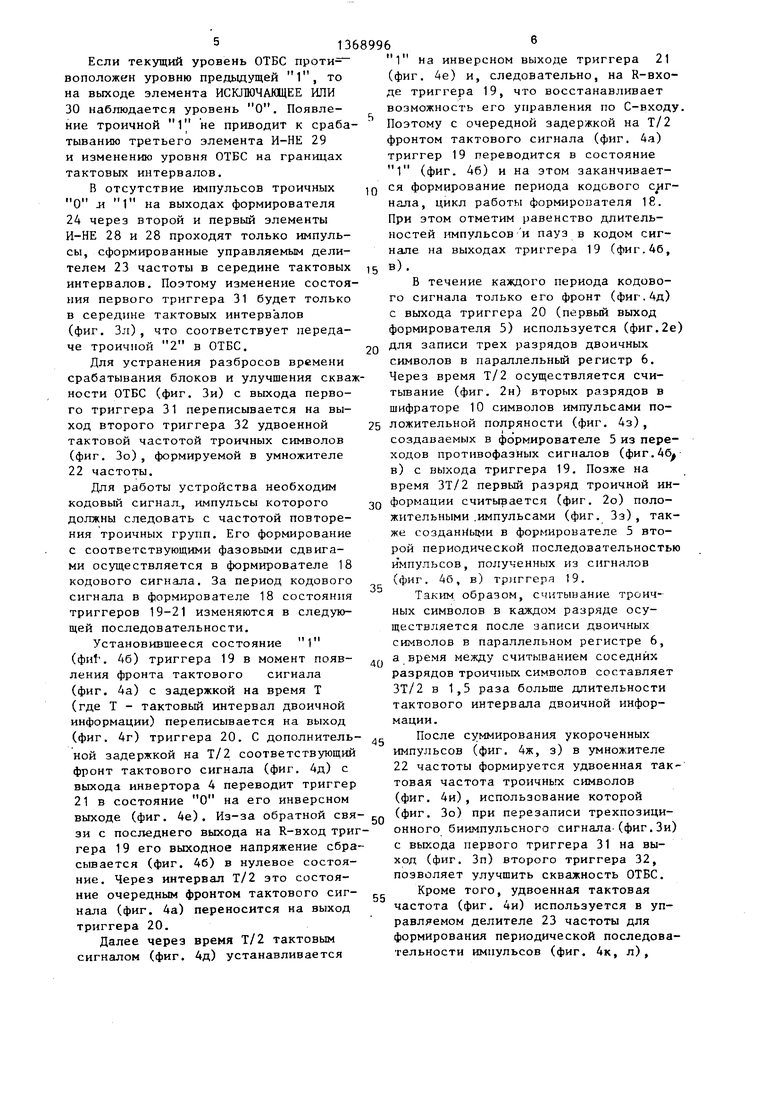

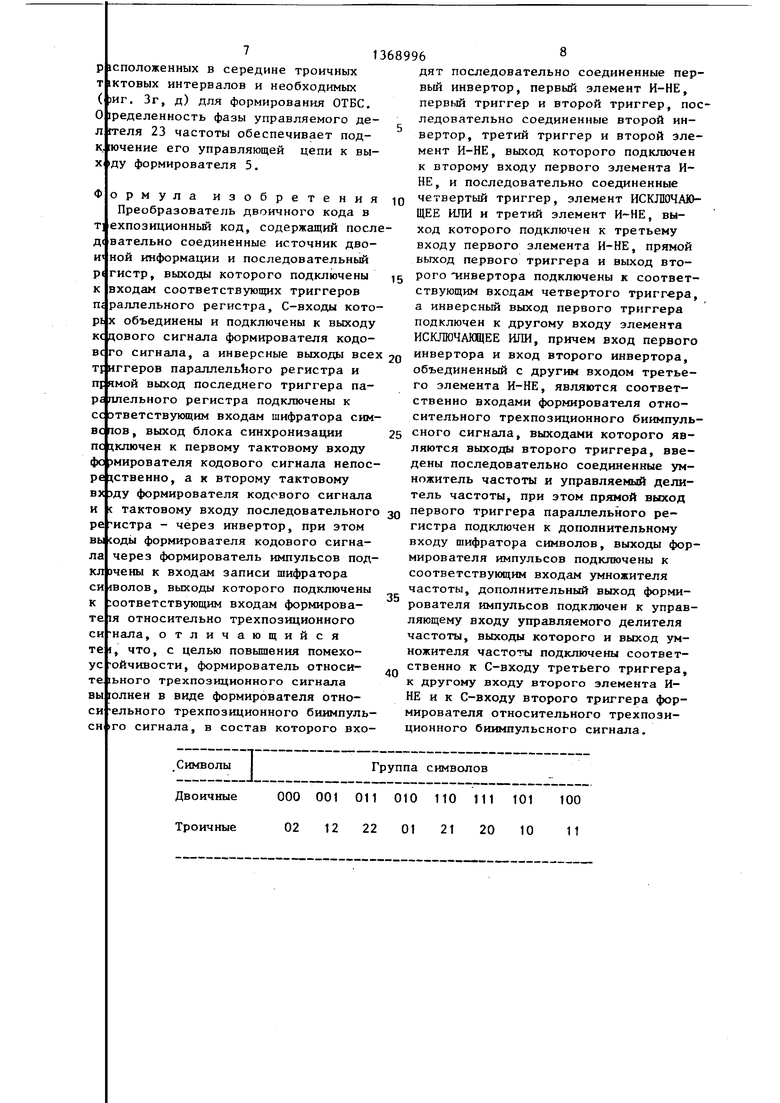

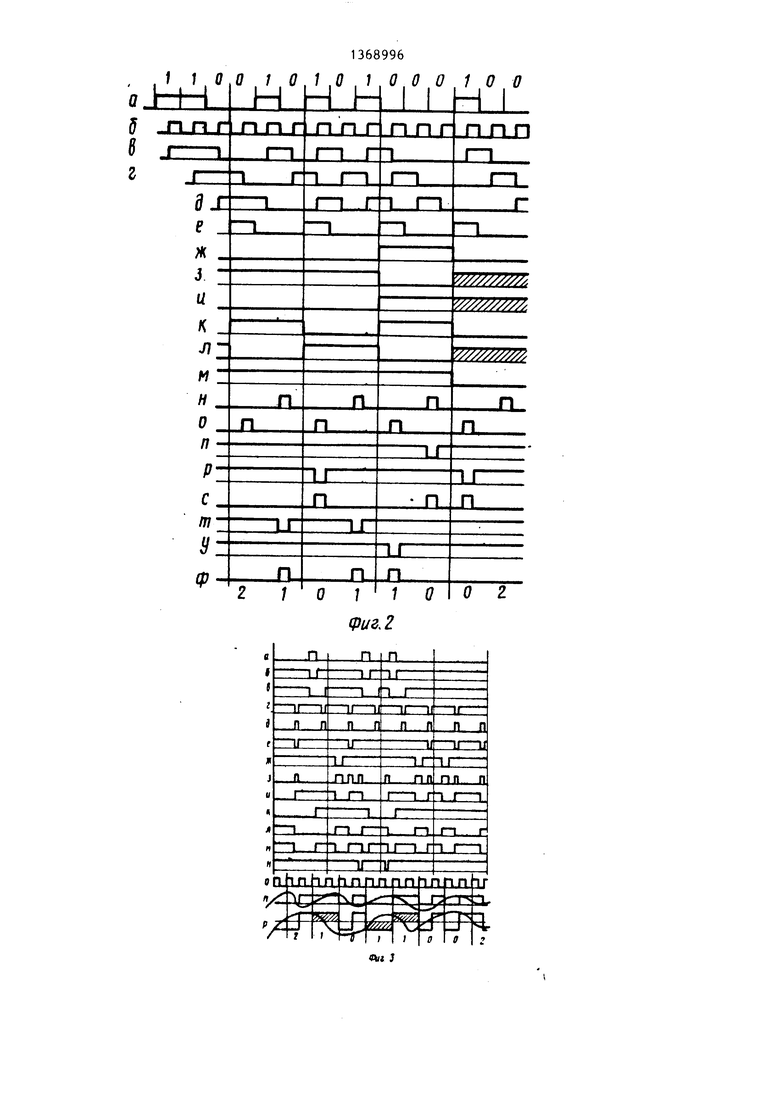

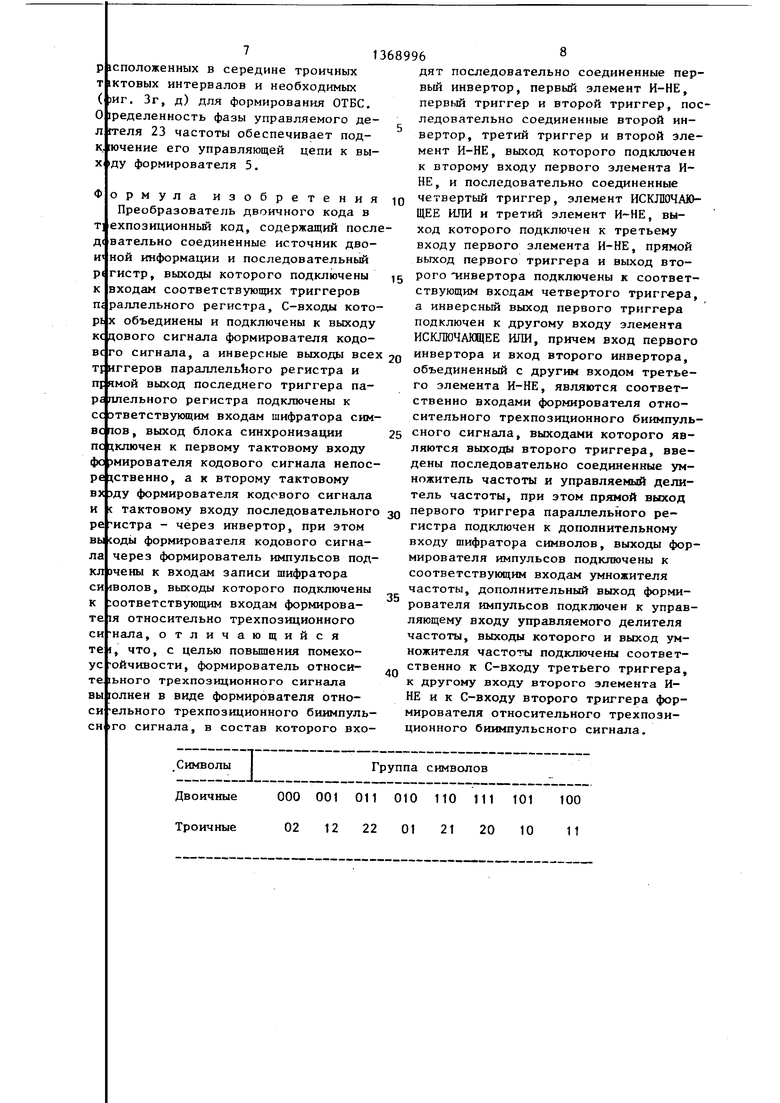

На фиг, 1 представлена структурная электрическая схема преобразователя двоичного кода в трехпозицион- ный код, на фиг. 2, 3 и 4 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь двоичного кода

мого и инверсного выходов триггера 7 (фиг. 2ж, з) поступает на первый и второй входы шифратора 10 символов, информация о втором разряде с инверсного выхода триггера 8 (фиг . 2и) поступает на третий вход шифратора 10 символов, а информация о третьем

10

разряде с прямого и инверсного выходов триггера 9 (фиг. 2к, л) соотв т- ственно на четвертый и пятый входы шифратора символов 10,

Для считывания троичных символов на двух троичных тактах формирова- в трехпозиционный код содержит источ- 5 тель 5 импульсов формирует периоди- ник 1 двоичной информации, последова- ческие последовательности импульсов тельный регистр 2, блок 3 синхрони- на границах тактов первого и второго зации, инвертор 4, формирователь 5 разрядов троичных символов (фиг.2н,о).

импульсов, параллельный регистр 6, состоящий из первог о, второго и третьего триггеров 7, 8 и 9, шифрлтор 10 символов, состоящий из элементов И-НЕ 11-17, формирователь 18 кодового сигнала, состоящий из триггеров 19-21, умножитель 22 частоты, управляемый делитель 23 частоты и формирователь 24 относительного трехпози- ционного биимпульсного сигнала (ОТБС) в состав которого входят первый и второй инверторы 25 и 26, первый.

20

С помощью этих последовательностей и в.соответствии с табл, 1 троичные нули первых разрядов в виде коротких импульсов формируются на выходе элемента И-НЕ 11 (фиг. 2п) при 1 на прямых выходах триггеров 7 и 9 (фиг, 2ж, к) в моменты появления импульсов считьшания на первом выходе формирователя 5 (фиг.2н), Троичные О во втором разряде на выходе элемента И-НЕ (фиг. 2р) воз- 30 можны в моменты появления импульсов

25

мого и инверсного выходов триггера 7 (фиг. 2ж, з) поступает на первый и второй входы шифратора 10 символов, информация о втором разряде с инверсного выхода триггера 8 (фиг . 2и) поступает на третий вход шифратора 10 символов, а информация о третьем

С помощью этих последовательностей и в.соответствии с табл, 1 троичные нули первых разрядов в виде коротких импульсов формируются на выходе элемента И-НЕ 11 (фиг. 2п) при 1 на прямых выходах триггеров 7 и 9 (фиг, 2ж, к) в моменты появления импульсов считьшания на первом выходе формирователя 5 (фиг.2н), Троичные О во втором разряде на выходе элемента И-НЕ (фиг. 2р) воз- можны в моменты появления импульсов

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

второй и третий элементы И-НЕ 27-29, элемент ИСКЛЮЧАЩЕЕ ИЛИ 30 и первый, второй, третий и четвертый триггеры 31-34,

Преобразователь двоичного кода в трехпозиционный код работает следующим образом.

Двоичная информация от источника 1 (фиг. 2а) поступает на вход последо ват ельного регистра 2, на второй вход которого подается тактовый сигнал блока 3 синхронизации через инвертор (фиг, 26), благодаря чему на выходах

Для регистрации группы двоичных символов 000 входы элемента И-НЕ 14 подключены к инверсным выходам первого, второго и третьего триггеров 7-9. При появлении 1 одновременно на

последовательного регистра 2 одновременно присутствуют три разряда двоич- всех указанных выходах Хзаштрихованная область на фиг, 2з, и, л), на выходе элемента И-НЕ 14 формируется напряжение О (фиг. 2м),

Троичные 1 в первом разряде по- gj являются в виде коротких импульсов на выходе элемента И-НЕ 15 (фиг. 2т), если считывающие импульсы (фиг, 2н) совпадают с 1 на инверсном выходе первого триггера 7 (фиг. 2з) и на gj выходе элемента И-НЕ 14 (фиг. 2м). При считьтании троичных 1

ной информации (фиг, 2в, гд).На первом выходе формирователя 5 (фиг. 2е) формируется кодовый сигнал, в момент появления фронтов импульсов которого в параллельный регистр 6 поочередно записывается двоичная информация на каждых трех соседних.тактовых интервалах.

Шифратор 10 символов преобразует символы двоичной информации в символы троичной информации в соответствии с кодовой таблицей.

Информация о символах в первом разряде каждой двоичной группы с прявторого

разряда отдельные импульсы последова- тапьности (фиг, 2о) появляются на выходе элемента И-НЕ 16 (фиг, 2у)

на втором выходе формирователя 5 (фиг. 2о) в.состоянии 1 находятся напряжения на инверсных выходах пер- пого и третьего триггеров 7 и 9 (фиг. 2з, л), Ямпульсы, соответствующие троичным О обоих разрядов (фиг. 2п, р), суммируются в элементе И-НЕ 13 (фиг. 2с) и поступают на формирователь 24 ОТБС,

Для регистрации группы двоичных символов 000 входы элемента И-НЕ 14 подключены к инверсным выходам первого, второго и третьего триггеров 7-9. При появлении 1 одновременно на

всех указанных выходах Хзаштрихованная область на фиг, 2з, и, л), на выходе элемента И-НЕ 14 формируется напряжение О (фиг. 2м),

Троичные 1 в первом разряде по- являются в виде коротких импульсов на выходе элемента И-НЕ 15 (фиг. 2т), если считывающие импульсы (фиг, 2н) совпадают с 1 на инверсном выходе первого триггера 7 (фиг. 2з) и на выходе элемента И-НЕ 14 (фиг. 2м). При считьтании троичных 1

второго

разряда отдельные импульсы последова- тапьности (фиг, 2о) появляются на выходе элемента И-НЕ 16 (фиг, 2у)

1 на инверсном выходе второго триггера 8 (фиг. 2и) и на выходе эле- Nента И-НЕ 14 (фиг. 2м). Через эле- ент И-НЕ 17 импульсы (фиг. 2ф), ха- Jактеризующие троичные 1 обоих разрядов (фиг. 2т, у) подаются на вто- ррй вход формирователя 24 ОТБС.

В результате появления на выходах фратора символов 10 импульсов, со- сгветствующих троичным О и 1

(

этсутствие импульсов О и 1 соответс гвует троичным 2, не принимающим у 1астие в формировании ОТБС), осуще с гвляется преобразование двоичной V 1формации на каждых трех тактовых и 1тервалах (фиг. 2а) в троичные сим- в шы на двух тактовых интервалах, крдирование ЗВ2Т в соответствии с аблицей.

При формировании ОТБС передача оичного осуществляется формировани 4 переходов (любое изменение поляр- эсти напряжения) на границе и в се- здине тактового интервала. Троичная передается одним переходом в се- 2дине тактового интервала. Поэтому 5а эти символа передаются двумя им- лъсамя внутри тактового интервала, го обеспечивает баланс сигнала по эстоянной составляющей внутри каждо ) тактового интервала. Только пере- троичной 1 осуществляется уст шением перехода в середине такто- IX интервалов, нарушением биимпуль- юго сигнала внутри тактового интер 1ла. Поэтому передача 1 может на- iraiaTb баланс ОТБС; Для устранения 1к6й возможности, сохранения преи- м| ществ ОТБС каждая очередная двоич- 1я 1 должна формировать уровень 1пряжения, противоположный уровню гредачи предыдущей 1.

Для этого импульсы, соответствую- щ|1е троичным 1 (фиг. 2ф, За), че- ;з второй инвертор 26 (фиг. Зб) пе- гводят третий триггер 33 в состоя- le О (фиг. Зв). Последующее вос- гановление исходного состояния тре- эего триггера 33 происходит благо- подключению его D-входа к шине 1тания и периодической последова- гльности импульсов в середине так- эвых интервалов (фиг. Зг), сформи- званных в управляемом делителе 23 1СТОТЫ, которая подается на С-вход (|)иг. Зг).

В инвертированной последователь- зсти импульсов, сформированных в

0

0

середине тактовых интервалов на втором выходе управляемого делителя частоты (фиг. Зд), во втором элементе И-НЕ 28 запрещаются (фиг. Зе) только те импульсы периодической последовательности (фиг. Зг), которые совпадают с расширенными импульсами троичных 1 (фиг. Зв).

Импульсы, соответствующие троичным О (фиг. 2с), после первого инвертора 25 поступают (фиг, Зж) на первый вход первого элемента И-НЕ 27, суммируются с импульсами на втором 5 ходе-(фиг. Зе) и каждый фронт суммарной последовательности импуль.сов (фиг. Зз) изменяет уровень напряжения на выходе первого триггера 31, что приводит к формированию ОТБС (фиг. Зи).

Баланс ОТБС при передаче 1 обеспечивается следующим образом.

В момент появления любой троичной 1 на выходе второго инвертора 26 5 (фиг. 36) уровень ЪТБС (фиг. Зи) записывается в четвертый триггер 34 и сравнивается с текущими уровнями ОТБС на инверсном выходе первого триггера 31 (фиг. 3л). Результат этого сравнения на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 (фиг. 3м) подается на один из входов третьего элемента И-НЕ 29. В том случае, если при передаче очередной троичной 1 следует изменить уровень выходного сигнала, то это соответствует состоянию 1 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 (фиг. 3м) и поэтому на выход третьего элемента И-НЕ 29 (фиг.Зн) начинает проходить импульс троичной 1 (фиг. За), поступающий на ее второй вход. Вследствие этого, к импульсам троичных 1 на границах тактовых интервалов в сигнале (фиг. Зз) добавляются импульсы (фиг. Зн), что вызывает дополнительное изменение уровней в ОТБС (фиг. 3л) и устанавливается уровень, противоположный уровню предыдущей 1.

0

5

0

5

В свою очередь изменение уровня (фиг. 3л) переключает элемент ИСКГЙО- ЧАЮЩЕЕ ИЛИ 30, третий элемент И-НЕ 29 и поэтому длительность импульсов (фиг. Зн) на ее выходе определяется

55 временем срабатьшания соответствующих последовательно включенных блоков и меньще длительности импульсов троичных 1 (фиг. За).

51368996

Если текущий уровень ОТБС проти

II

воположен уровню предьщущей 1, то на выходе элемента ИСКЛЮЧАМДЕЕ ИЛИ 30 наблюдается уровень О. Появление троичной 1 не приводит к срабатыванию третьего элемента И-НЕ 29 и изменению уровня ОТБС на границах тактовых интервалов.

В отсутствие импульсов троичных О л 1 на выходах формирователя 24 через второй и первый элементы И-НЕ 28 и 28 проходят только импульсы, сформированные управляемым делителем 23 частоты в середине тактовых интервалов. Поэтому изменение состояния первого триггера 31 будет только в середине тактовых интервалов (фиг. 3л), что соответствует передаче троичной 2 в ОТБС.

Для устранения разбросов времени срабатывания блоков и улучшения скваности ОТБС (фиг. Зи) с выхода первого триггера 31 переписывается на выход второго триггера 32 удвоенной тактовой частотой троичных символов (фиг. Зо), формируемой в умножителе 22 частоты.

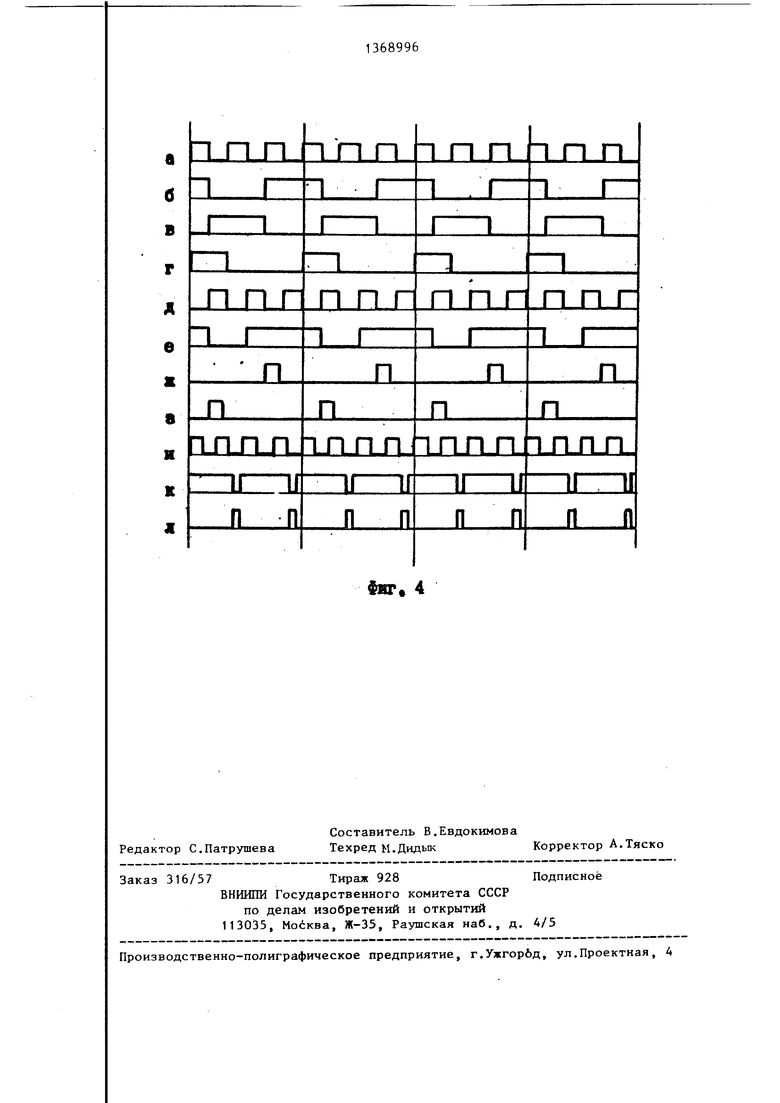

Для работы устройства необходим кодовый сигнал., импульсы которого должны следовать с частотой повторения троичных групп. Его формирование с соответствующими фазовыми сдвигами осуществляется в формирователе 18 кодового сигнала. За период кодового сигнала в формирователе 18 состояния триггеров 19-21 изменяются в следующей последовательности.

Установившееся состояние 1 (фи. Аб) триггера 19 в момент появления фронта тактового сигнала (фиг. 4а) с задержкой на время Т (где Т - тактовьй интервал двоичной информации) переписывается на выход (фиг. Аг) триггера 20. С дополнитель ной задержкой на Т/2 соответствующий фронт тактового сигнала (фиг. 4д) с выхода инвертора 4 переводит триггер 21 в состояние О на его инверсном выходе (фиг. 4е). Из-за обратной связи с последнего выхода на R-вход тригера 19 его выходное напряжение сбрасывается (фиг. 46) в нулевое состояние. Через интервал Т/2 это состояние очередным фронтом тактового сигнала (фиг. 4а) переносится на выход триггера 20.

Далее через время Т/2 тактовым сигналом (фиг. 4д) устанавливается

6

5

0

на инверсном выходе триггера 21 (фиг. 4е) и, следовательно, на R-BXO- де триггера 19, что восстанавливает возможность его управления по С-входу. Поэтому с очередной задержкой на Т/2 фронтом тактового сигнала (фиг. 4а) триггер 19 переводится в состояние 1 (фиг. 4б) и на этом заканчивается формирование периода кодового сигнала, цикл работы формирователя 18. При этом отметим равенство длительностей импульсов и пауз в кодом сигнале на выходах триггера 19 (фиг.46, в).

В течение каждого периода кодового сигнала только его фронт (фиг.4д) с выхода триггера 20 (первый выход формирователя 5) используется (фиг.2е) для записи трех разрядов двоичных символов в параллельный регистр 6. Через время Т/2 осуществляется счи- тьшание (фиг. 2н) вторых разрядов в шифраторе 10 символов импульсами по5 ложительной полряности (фиг. 4з),

создаваемых в формирователе 5 из переходов противофазных сигналов (фиг.4б в) с выхода триггера 19. Позже на время ЗТ/2 первый разряд троичной ин0 формации считывается (фиг. 2о) положительными .импульсами (фиг. Зз), также созданными в формирователе 5 второй периодической последовательностью и мпульсов, полученных из сигналов (фиг. 4б, в) триггера 19.

Таким образом, считывание троичных символов в каждом разряде осуществляется после записи двоичных символов в параллельном регистре 6, а время между считыванием соседних разрядов троичных символов составляет ЗТ/2 в 1,5 раза больше длительности тактового интервала двоичной информации.

После суммирования укороченных импульсов (фиг. 4ж, з) в умножителе 22 частоты формируется удвоенная тактовая частота троичных символов (фиг. 4и), использование которой (фиг. Зо) при перезаписи трехпозици- онного биимпульсного сигнала-(фиг. Зи) с выхода первого триггера 31 на выход (фиг. Зп) второго триггера 32, позволяет улучшить скважность ОТБС.

Кроме того, удвоенная тактовая частота (фиг. 4и) используется в управляемом делителе 23 частоты для формирования периодической последовательности импульсов (фиг. 4к, л).

5

0

0

5

ф

р

пг Pi

сположенных в середине троичных ктовых интервалов и необходимых )иг. Зг, д) для формирования ОТБС. феделенность фазы управляемого де- гтеля 23 частоты обеспечивает под- ючение его управляющей цепи к вы- ду формирователя 5.

ормула изобретения

Преобразователь двоичного кода в ехпозиционный код, содержащий посл вательно соединенные источник дво- ной информации и последовательный гистр, выходы которого подключены входам соответствующих триггеров раллельного регистра, С-входы кото X объединены и подключены к выходу

КС цового сигнала формирователя кодовсго сигнала, а инверсные выходы всех 2о инвертора и вход второго инвертора.

дят последовательно соединенные пер вый инвертор, первый элемент И-НЕ, первый триггер и второй триггер, по ледовательно соединенные второй инвертор, третий триггер и второй эле мент И-НЕ, выход которого подключен к второму входу первого элемента И- НЕ, и последовательно соединенные четвертый триггер, элемент ИСКЛЮЧАЮ ЩЕЕ ИЛИ и третий элемент И-НЕ, выход которого подключен к третьему входу первого элемента И-НЕ, прямой выход первого триггера и выход второго -инвертора подключены к соответствующим входам четвертого триггера а инверсный выход первого триггера подключен к другому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход первого

TIиггеров параллельного регистра и щ ямой выход последнего триггера пара плельного регистра подключены к ее этветствующим входам шифратора сим- пов, выход блока синхронизации

вс

ПС включен к первому тактовому входу фо )мирователя кодового сигнала непос- petCTBeHHo, а к второму тактовому вх )ду формирователя кодового сигнала

объединенный с другим входом третьего элемента И-НЕ, являются соответственно входами формирователя относительного трехпозиционного биимпуль 25 сного сигнала, выходгши которого являются выходы второго триггера, введены последовательно соединенные умножитель частоты и управляемый делитель частоты, при этом прямой выход

и ре

с тактовому входу последовательного зо ПЕРВОГО триггера параллельного реистра - через инвертор, при этом

гистра подключен к дополнительному входу шифратора символов, выходы фо мирователя импульсов подключены к соответствующим входам умножителя частоты, дополнительный выход форми рователя импульсов подключен к упра ляющему входу управляемого делителя частоты, выходы которого и выход ум ножителя частоты подключены соответ ственно к С-входу третьего триггера к другому входу второго элемента И- НЕ и к С-входу второго триггера формирователя относительного трехпозиционного биимпульсного сигнала.

вы соды формирователя кодового сигнала через формирователь импульсов под- клэчены к входам записи шифратора волов, выходы которого подключены

си

соответствующим входам формирова- 1я относительно трехпозиционного нала, отличающийся 1, что, с целью повышения помехо- гойчивости, формирователь относи-

те си те ус

теЬьного трехпозиционного сигнала вы голнен в виде формирователя относисн

ельного трехпозиционного биимпуль- го сигнала, в состав которого вхо

ю

е- 15

368996

дят последовательно соединенные первый инвертор, первый элемент И-НЕ, первый триггер и второй триггер, последовательно соединенные второй инвертор, третий триггер и второй элемент И-НЕ, выход которого подключен к второму входу первого элемента И- НЕ, и последовательно соединенные четвертый триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и третий элемент И-НЕ, выход которого подключен к третьему входу первого элемента И-НЕ, прямой выход первого триггера и выход второго -инвертора подключены к соответствующим входам четвертого триггера, а инверсный выход первого триггера подключен к другому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход первого

инвертора и вход второго инвертора.

объединенный с другим входом третьего элемента И-НЕ, являются соответственно входами формирователя относительного трехпозиционного биимпуль- сного сигнала, выходгши которого являются выходы второго триггера, введены последовательно соединенные умножитель частоты и управляемый делитель частоты, при этом прямой выход

гистра подключен к дополнительному входу шифратора символов, выходы формирователя импульсов подключены к соответствующим входам умножителя частоты, дополнительный выход формирователя импульсов подключен к управляющему входу управляемого делителя частоты, выходы которого и выход умножителя частоты подключены соответственно к С-входу третьего триггера, к другому входу второго элемента И- НЕ и к С-входу второго триггера формирователя относительного трехпозиционного биимпульсного сигнала.

I 100 1 о 1.0 . 1 0.0.0 100

a

г

(риг, 2

Фиг 4

Авторы

Даты

1988-01-23—Публикация

1985-10-10—Подача