4 О5 1 00 to

15

1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации.

Цель изобретения - передача асинхронных сигналов.

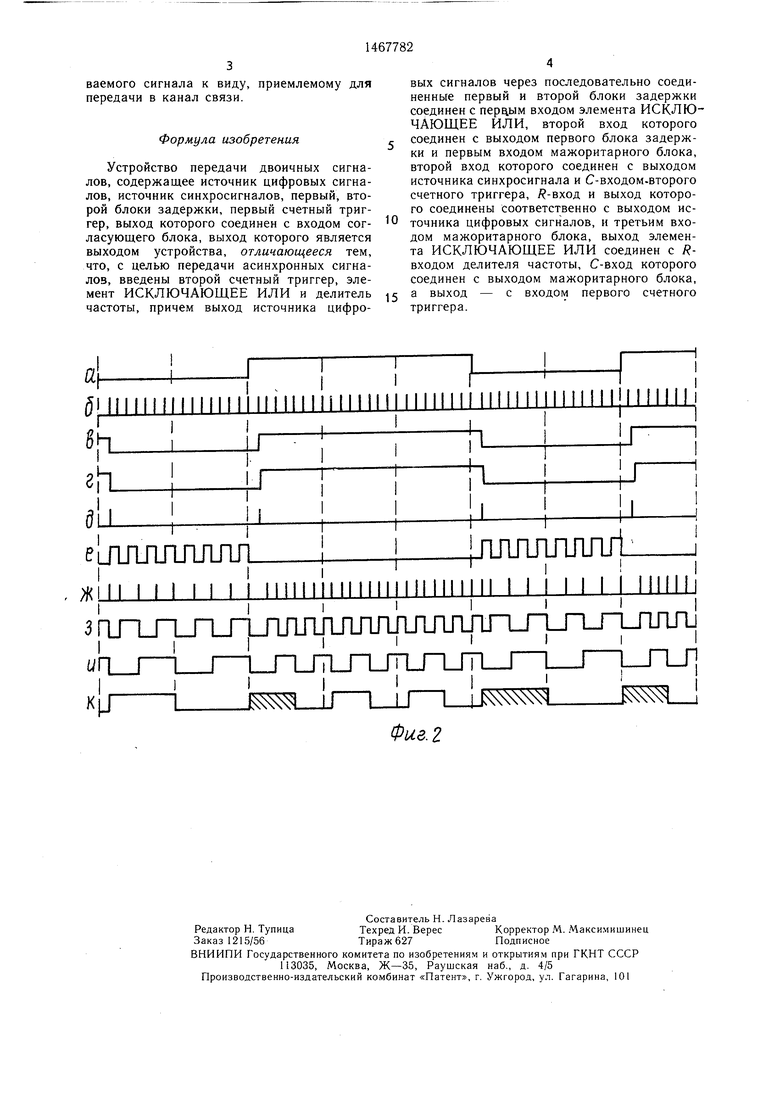

На фиг. 1 изображена структурная элект- рическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит источник 1 цифровых сигналов, источник 2 синхросигналов, Ю блоки 3 и 4 задержки, второй счетный триггер 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, мажоритарный блок 7, делитель 8 частоты, первый счетный триггер 9, согласующий блок 10.

Устройство работа ет следующим образом.

Цифровой двоичный сигнал (фиг. 2 а), задержанный в блоке 3 (фиг. 2 в), поступает на вход элемента 6 и, после задержки в блоке 4 (фиг. 2 г), на другой вход элемента 6.20

Блок 4 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ б образуют схему детектирования изменений входного сигнала, на выходе которой (фиг. 2 д) формируются короткие импульсы, передние фронты которых совпадают с моментами смены уровня сигнала на выходе блока 3, а длительность определяется задержкой блока 4.

Входной информационный сигнал непосредственно от источника 1 поступает на R-Бход счетного триггера 5, на С-вход которого подается сигнал от источника 2 (фиг. 2 б). Этот сигнал представляет из себя импульсную последовательность, частота которой в раза превыщает темп поступления информации от источника 1, где п,2... (для больщей наглядности на ос фиг. 2 предствлен случай ). Фаза синхросигнала никак не связана с моментами смены значений информационного сигнала, т. е. эти сигналы асинхронны. В качестве источника 2 может использоваться как встроенный, так и внещний генератор тактовых импульсов. Включение счетного триггера 5 определяет его работу как управляемого делителя частоты синхросигнала на два, причем низкий уровень информац и- онного сигнала разрешает деление, а высокий - блокирует его, сбрасывая в «О триггер 5 (фиг. 2 е).

Совместное включение источника 2, блока 3, счетного триггера 5 и мажоритарного блока 7 обеспечивает формирование

на выходе мажоритарного блока 7 формируется импульсная последовательность, закон изменения частоты которой можно представить выражением

. FJf(l+D),

где F - частота формируемой последовательности;fan - частота исходного синхросигнала;

(О - при логическом нуле на выходе блока 3 1 - при логической единице на выходе

блока 3.

Очевидно, что поделив сигнал на выходе мажоритарного блока 7 на можно получить на выходе устройства импульсную последовательность, соответствующую биимпульсному представлению исходного информационного сигнала от источника 1. Это обеспечивается последовательным включением делителя 8 и счетного триггера 9, которые в сумме создают нужный коэффи- циет деления.

25

30

Задержка исходного информационного сигнала в блоке 3 заставляет делитель 8 постоянно «опаздывать со сменой частоты выходного сигнала. Как видно из фиг. 2з (первый каскад делителя) и фиг. 2и (второй каскад делителя), изменения частоты формируемых импульсных последовательностей происходят с запаздывани ем по отнощению к исходному информационному сигналу на время задержки блока 3 (в данном случае, равное периоду исходного синхросигнала). Это запаздывание приводит к тому, что фаза последовательности импульсов на выходе счетного триггера 9 меняется не скачками, а через некоторое промежуточное значение (фиг. 2/с, защтрихованные импульсы). Сигнал, полученный на выходе счетного триггера 9, соответствует биимпульсному представ- 40 лению исходного информационного сигнала, причем главная смена фазы обеспечивает заданную достоверность передачи.

Как видно из фиг. 2д, импульсы, формируемые на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и поступающие на R-вход делителя 8, не оказывают влияния на его работу, когда они присутствуют в моменты циклического обнуления разрядов делителя 8, т. е., когда цикл работы делителя 8 совпадает с фазой входной информации.

45

на выходе мажоритарного блока 7 импульс- Иначе происходит при их рассинхронизации

ной последовательности переменной частоты (фиг. 2 ж). Фаза и длительность формируемых импульсов совпадает с фазой и длительностью синхросигнала от источника 2. Частота , формируемой последовательности равна частоте синхросигнала в интервалах, когда уровень сигнала на выходе блока 3 соответствует логической единице и вдвое меньше при логическом нуле. Таким образом.

(начальный участок диаграммы фиг. 2ж), когда делитель 8 принудительно сбрасывается в «О, что обеспечивает требуемую синхронность работы счетчика и поступления входных данных, а в конечном итоге - 55 возможность работы с асинхронной входной информацией.

Согласующий блок 10 обеспечивает преобразование электрических параметров переда

на выходе мажоритарного блока 7 формируется импульсная последовательность, закон изменения частоты которой можно представить выражением

. FJf(l+D),

где F - частота формируемой последовательности;fan - частота исходного синхросигнала;

(О - при логическом нуле на выходе блока 3 1 - при логической единице на выходе

блока 3.

Очевидно, что поделив сигнал на выходе мажоритарного блока 7 на можно получить на выходе устройства импульсную последовательность, соответствующую биимпульсному представлению исходного информационного сигнала от источника 1. Это обеспечивается последовательным включением делителя 8 и счетного триггера 9, которые в сумме создают нужный коэффи- циет деления.

с

5

0

Задержка исходного информационного сигнала в блоке 3 заставляет делитель 8 постоянно «опаздывать со сменой частоты выходного сигнала. Как видно из фиг. 2з (первый каскад делителя) и фиг. 2и (второй каскад делителя), изменения частоты формируемых импульсных последовательностей происходят с запаздыванием по отнощению к исходному информационному сигналу на время задержки блока 3 (в данном случае, равное периоду исходного синхросигнала). Это запаздывание приводит к тому, что фаза последовательности импульсов на выходе счетного триггера 9 меняется не скачками, а через некоторое промежуточное значение (фиг. 2/с, защтрихованные импульсы). Сигнал, полученный на выходе счетного триггера 9, соответствует биимпульсному представ- 0 лению исходного информационного сигнала, причем главная смена фазы обеспечивает заданную достоверность передачи.

Как видно из фиг. 2д, импульсы, формируемые на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и поступающие на R-вход делителя 8, не оказывают влияния на его работу, когда они присутствуют в моменты циклического обнуления разрядов делителя 8, т. е., когда цикл работы делителя 8 совпадает с фазой входной информации.

5

Иначе происходит при их рассинхронизации

Иначе происходит при их рассинхронизации

(начальный участок диаграммы фиг. 2ж), когда делитель 8 принудительно сбрасывается в «О, что обеспечивает требуемую синхронность работы счетчика и поступления входных данных, а в конечном итоге - возможность работы с асинхронной входной информацией.

Согласующий блок 10 обеспечивает преобразование электрических параметров передаваемого сигнала к виду, приемлемому для передачи в канал связи.

Формула изобретения

Устройство передачи двоичных сигналов, содержащее источник цифровых сигналов, источник синхросигналов, первый, второй блоки задержки, первый счетный триггер, выход которого соединен с входом согласующего блока, выход которого является выходом устройства, отличающееся тем, что, с целью передачи асинхронных сигналов, введены второй счетный триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и делитель частоты, причем выход источника цифровых сигналов через последовательно соединенные первый и второй блоки задержки соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого блока задержки и первым входом мажоритарного блока, второй вход которого соединен с выходом источника синхросигнала и С-входом-второго счетного триггера, R-вход, и выход которого соединены соответственно с выходом ис- точника цифровых сигналов, и третьим входом мажоритарного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с R- входом делителя частоты, С-вход которого соединен с выходом мажоритарного блока, а выход - с входом первого счетного триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема биимпульсных сигналов | 1985 |

|

SU1241512A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1564735A1 |

| Биимпульсный регенератор | 1986 |

|

SU1413727A2 |

| Устройство синхронизации | 1983 |

|

SU1107314A1 |

| Устройство для формирования биимпульсного сигнала | 1989 |

|

SU1626423A1 |

| Устройство формирования тактового синхросигнала | 1987 |

|

SU1524192A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

Изобретение относится к электросвязи. Цель изобретения - обеспечение передачи асинхронных сигналов. Устройство содержит источник I цифровых сигналов, источник 2 синхросигналов, блоки задержки 3 и 4, счетные триггеры 5 и 9, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 6, мажоритарный блок 7, делитель 8 частоты и согласующий блок Ю. Цель достигается за счет принудительного сбрасывания в «О делителя 8. Это обеспечивает требуемую синхронность работы счетного триггера 9 и поступления входных данных, а в конечном итоге - возможность работы с асинхронной входной информацией. 2 ил.

3 rin rbJTJiJiJirmJiimju

K|J

J li LJJ LjJSS

Фиг. 2

| Устройство передачи двоичных сигналов | 1983 |

|

SU1100749A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-23—Публикация

1987-07-30—Подача