/f

со со ю

со

Изобретение относится к вычислительной технике и может быть использовано в качестве цифровой задержки для медленно изменяющейся информации

Цель изобретения - упрощение устройства за счет уменьшения емкости блока памяти,

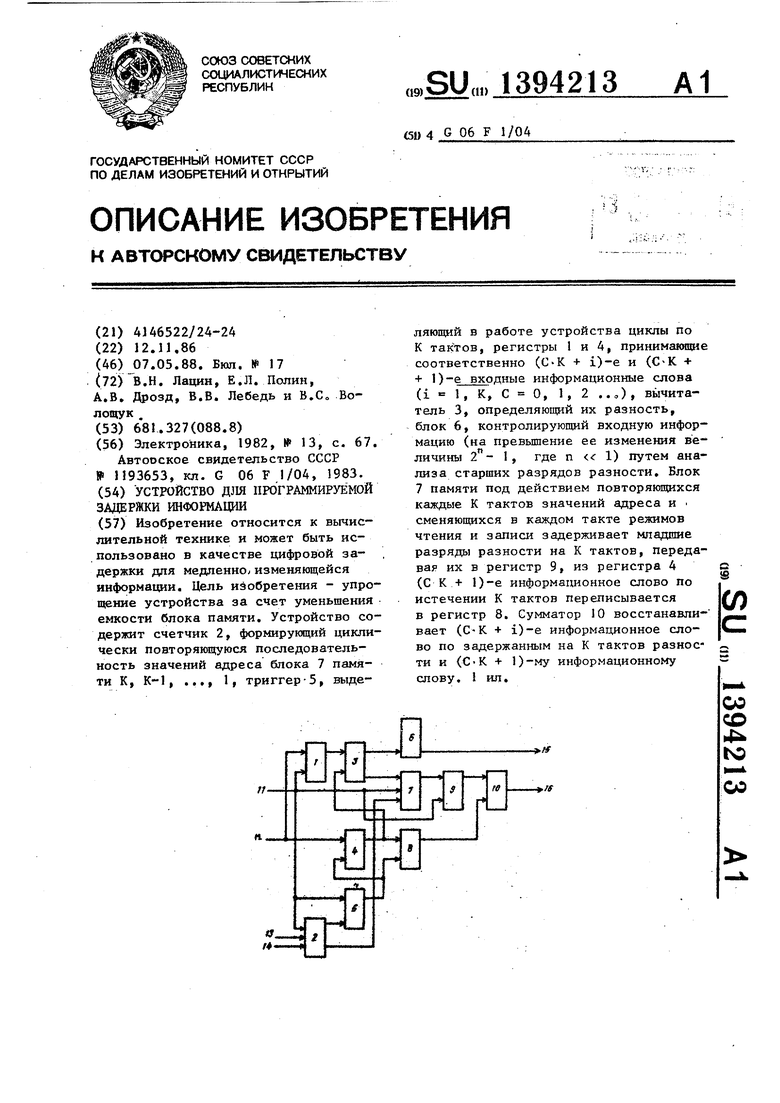

На чертеже изображена структурная схема устройства для программируемой задержки информации.

Устройство содержит входной регистр I , счетчик 2 адреса, вычита тель 3, первый буферный регистр 4, триггер 5, блок 6 контроля, блок 7 памяти, второй буферный регистр 8, выходной регистр 9, сумматор 10, син- хровход 11 устройства, информационный вход 12 устройства, вход 13 кода задержки устройства, вход 14 начально установки устройства, выход Ошибка устройства 15, информационный выход 16 устройства.

Устройство работает следующим образом,

В начальный момент времени на входы 13 и 14 устройства поступают соответственно код задержки К и сопровождающий его сигнал приема П, по которому осуществляется прием кода К в счетчик 2 адреса. На счетный вход счетчика 2 поступают синхросигналы СИ с синхровхода I1 устройства. Под действием этих сигналов, отмеряющих задним фронтом такты работы устройства, счетчик 2 формирует циклически повторяющуюся последовательность значений К, К-1, .,., 1, Синхросигналы с синхровхода 1I устройства поступают также на синхровходы входного 1 и выход- ного 9 регистров, вход запись/чтение блока 7 и вход установки триггера 5,

В конце каждой последовательности значений, а также по сигналу приема II на выходе заема счетчика 2 вырабатывается короткий импульс, который поступает на вход сброса триггера 5, устанавливая его в нулевое состояние. По истечении полутакта триггер 5 возвращается в единичное состояние под действием синхросигнала СИ, поступающего на его установочный вход (вход сброса и установочньй вход триггера 5 являются инверсными, т,е. обнуление и установка в Г обеспечиваются нулевым уровнем), Таким образом, триггер 5 выделяет в работе устройства циклы по к тактов.

На информационный вход 12 устройства поступают медленно изменяющиеся 1-разрядные числа (слова). Изменение слов за К тактов работы устройства не превътает величины 2 -1, причем ti 1, По синхросигналам СК информационные слова принимаются во входной регистр 1, а калодое (СК+1)--е информационное слово (С О, I, 2, .,,) записывается в регистр 4 по переднему фронту сигнала S, поступающего с выхода триггера 5 на синхровход регистра 4, Сигнал S поступает также на синхровход регистра 8, обеспечивая запись в него (через информацибнный вход) информационного слова с выхода регистра 4 в момент приема в него следующего слова. Такая перезапись информационных слов происходит кажды К тактов.

Информационное слово а

с вы0

О

5 0

-

хода регистра 4 поступает также на вичитающий вход вычитателя 3, на другой вход которого подается информа- ционное слово аск4, i 1, К с выхода регистра 1, Вычитатель 3 определяет разность р поступивших на его входы чисел (в дополнительном коде), Р cm-i ckti Поскольку изменениб входной информации за К тактов не превышает величины 2 - 1, то разность на выходе вычитателя 3 содержит п f I младших значащих разрядов, а старшие разряды, начиная с (п + 1), принимают нулевые значения, если разность- положительная или ноль, и единичные значения - для отрицательной разности. Старшие разряды поступают с первого выхода вычитателя 3 на вход блока 6 контроля, который анализирует их значения на равенство всех нулю или равенство всех единиц и при повышении хотя бы одного из зтих условий вырабатывает сигнал ошибки входной информации, поступающей на выход 15 устройства.

Младшие разряды разности снимаются с второго выхода вычитателя 3 и поступают на информационный вход блока 7, На адресный вход блока 7 поступает циклически повторяющаяся после- довательность значений. К, К-1, ,,,, I с выхода счетчика 2 адреса. Эта последовательность адресов обеспечивает обращение к каждбй из К ячеек памяти блока 7 с интервалом в К тактов. Причем при каждом обращении к ячейке

памяти в одном полутакте происходит считывание информации, записанной К тактов тому назад, а в следующем полутакте - запись очередных младших разрядов разности. Таким образом, организуется задержка младших разрядов разности на К тактов. Чередование в каждом такте режимов записи и чтения достигается путем подачи на вход запись/ чтение блока 7 синхросигналов СИ типа меандр. По этим же сигналам происходит прием в выходной регистр 9 считываемой из блока 7 информации, С выхода регистра 9 младшие разряды разности поступают на вход сумматора 10, на его (п + 1)-е младшие разряды, старшие разряды этого входа объединены между собой и подключены к (п + 1)-му разряду разнос- ти. На другой вход сумматора 10 поступает информационное слово с выхода.регистра 8. Сумматор 10 воссстанавСК fl

ливает информационное слово а

а., р и подает его на- выход 16

устройства.

По сравнению с известным, предлагаемое устройство задерживает информационные слова а-„. на К тактов,

-- К т-1

используя (п + 1)-разрядный блок па- мяти вместо 1-разрядного, что с учетом условия п « 1 обеспечивает уменьшение емкости блока памяти.

БЛОК 6 контроля может быть выполнен из двухвходового элемента ИЛИ и (1 - п)-разрядных элементов И и ИЛИ-НЕ, причем входы элементов И и ИЛИ-НЕ подключены к старшим разряд разности соответственно, начиная с п + 1-го разряда, а выходы этих эле- ментов соединены с входами элемента ШШ, выход которого является выходом блока контроля. Элемент И идентифицирует единичные значения всех старших разрядов разности, принимая при этом также единичное значение, элемент ШШ-НЕ идентифицирует нулевые значения всех старших разрядов разности, принимая при этом единичное значение Элемент ИЛИ объединяет эти значения, принимая на выходе единичное значени при всех нулевых или всех единичных значениях старших разрядов разности и нулевое значение в противном случа

5 0

5

5

0

0 5

соответствующее формации.

Ф

ошибке во входной инормула изобретени я Устройство для программируемой задержки информации, содержащее счетчик адреса, входной и выходной регистры и блок памяти, причем информационный вход и вход приема информации счетчика адреса являются соответственно входом кода задержки устройства и входом начальной установки устройства, выход счетчика адреса соединен с адресным входом блока памяти, выход которого соединен с информационным входом выходного регистра, синхровход которого и синхровход входного регистра устройства являются синхровходом устройства, информационный вход входного регистра является информационным входом устройства, отличающееся тем, что, с целью упрощения устройства за счет уменьшения емкости блока памяти, в него введены вычитатель, триггер, блок контроля, сумматор, первый и второй буферные регистры, причем счетный вход счетчика адреса, вход запись/ /чтение блока памяти, синхровход . входного регистра и установочный вход триггера подключены к синхровхо- ду устройства, вход сброса триггера соединен с выходом заема счетчика адреса, выход триггера соединен с синхровходами первого и второго буферных регистров, информационный вход первого буферного регистра соединен с информационным входом второго буферного регистра и вычитающим входом вычитателя, информационный вход которого соединен с выходом входного регистра, первый выход вычитателя соединен с выходом входного регистра, первый выход вычитателя соединен с входом блока контроля, выход которого является выходом Ошибка устройства, второй выход вычитателя соединен с информационным входом блока памяти, выход выходного регистра соединен с первым входом сумматора, второй вход которого соединен с выходом второго буферного регистра, выхьд сумматора является информационным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для вычисления коэффициентов цифрового фильтра | 1980 |

|

SU961103A1 |

| Устройство для приведения полиномов по модулям циклотомических полиномов | 1985 |

|

SU1357948A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383327A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве цифровой задержки для медленно, изменяющейся информации. Цель изобретения - упрощение устройства за счет уменьшения емкости блока памяти. Устройство содержит счетчик 2, формирующий циклически повторяющуюся последовательность значений адреса блока 7 памяти К, К-1, ..,, 1, триггер-5, выделяющий в работе устройства циклы по К так тов, регистры 1 и 4, принимающие соответственно ( + i)-e и (С К + + 1)-е входные информационные слова (,K, С 0, 1,2..,) вычита- тель 3, определяющий их разность, блок 6, контролирующий входную информацию (на превышение ее изменения величины 1, где п « 1) путем анализа старших разрядов разности. Блок 7 памяти под действием повторяющихся каждые К тактов значений адреса и сменяющихся в каждом такте режимов чтения и записи задерживает младшие разряды разности на К тактов, передавая их в регистр 9, из регистра 4 (С К + 1)-е информационное слово по истечении К тактов переписывается в регистр В. Сумматор 10 восстанавли- вает (С К + i)-e информационное слово по задержанным на К тактов разнос- ти и (С К + 1)-му информационному слову, I ил. а 5 (Л

| Электроника, 1982, 13, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Способ уменьшения водопроницаемости грунтов в гидротехнических сооружениях | 1949 |

|

SU93653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-07—Публикация

1986-11-12—Подача