13

W гЧ

J5

ОО 00

ОО со го

ком, вычисленным для этого же слова до записи его в блок 7 памяти.

При нормальной работе устройства или при незначительном искажении слова (искажение младших разрядов) признаки, вычисленные до записи и после чтения слова, совпадают и на выходе блока 12 удерживается сигнал логического «О. Если же в процессе задержки произошло значительное искажение информационного слова (искажеИзобретение относится к вычислительной технике и может быть использовано в блоках задержки цифровой информации.

Цель изобретения - повышение достоверности задержанной устройством инфор- мации.

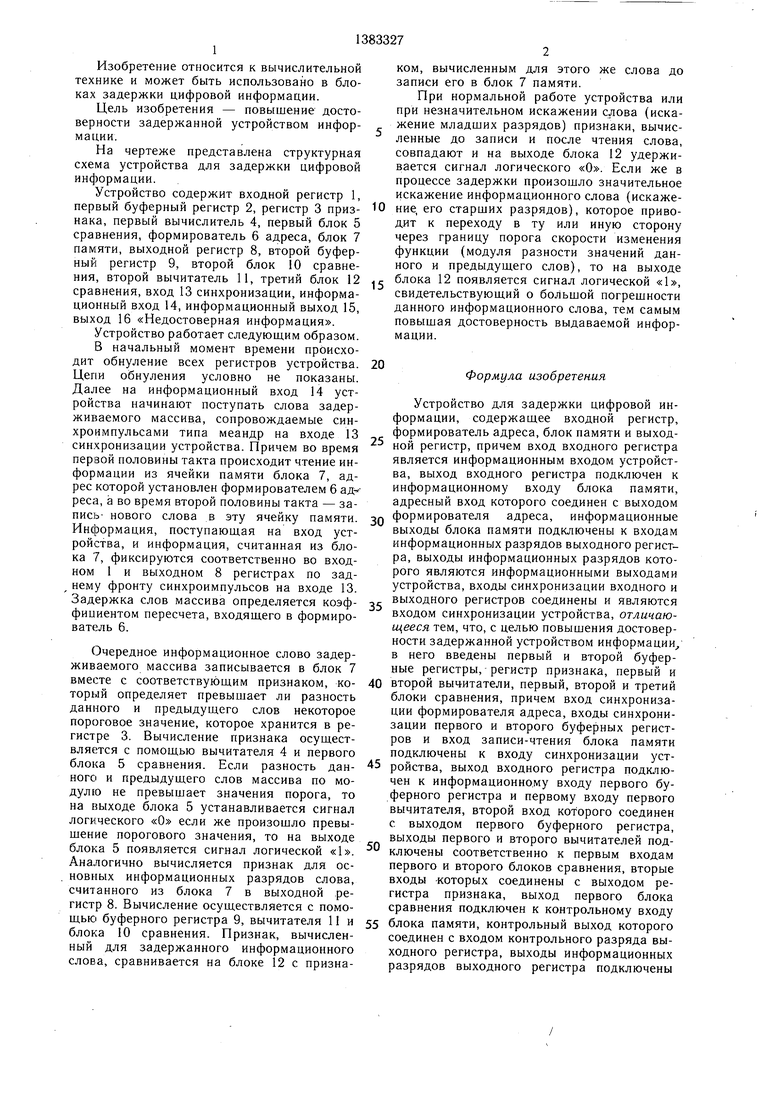

На чертеже представлена структурная схема устройства для задержки цифровой информации.

Устройство содержит входной регистр 1, первый буферный регистр 2, регистр 3 приз- Ю ние, его старших разрядов), которое приво- нака, первый вычислитель 4, первый блок 5 дит к переходу в ту или иную сторону сравнения, формирователь 6 адреса, блок 7 через границу порога скорости изменения памяти, выходной регистр 8, второй буфер-функции (модуля разности значений данный регистр 9, второй блок 10 сравне-ного и предыдущего слов), то на выходе

ния, второй вычитатель 11, третий блок 12 с блока 12 появляется сигнал логической «1, сравнения, вход 13 синхронизации, информа-свидетельствующий о большой погрешности

ционный вход 14, информационный выход 15, выход 16 «Недостоверная информация.

Устройство работает следующим образом.

В начальный момент времени происходит обнуление всех регистров устройства. 20 Цепи обнуления условно не показаны. Далее на информационный вход 14 устройства начинают поступать слова задерданного информационного слова, тем самым повышая достоверность выдаваемой информации.

Формула изобретения

Устройство для задержки цифровой информации, содержащее входной регистр, формирователь адреса, блок памяти и выходной регистр, причем вход входного регистра является информационным входом устройства, выход входного регистра подключен к информационному входу блока памяти, адресный вход которого соединен с выходом

жииаемого массива, сопровождаемые синхроимпульсами типа меандр на входе 13 синхронизации устройства. Причем во время первой половины такта происходит чтение информации из ячейки памяти блока 7, адрес которой установлен формирователем 6 реса, а во время второй половины такта - за25

Устройство для задержки цифровой информации, содержащее входной регистр, формирователь адреса, блок памяти и выходной регистр, причем вход входного регистра является информационным входом устройства, выход входного регистра подключен к информационному входу блока памяти, адресный вход которого соединен с выходом

пись- нового слова в эту ячейку памяти, зо Формирователя адреса, информационные

Информация, поступающая на вход устройства, и информация, считанная из блока 7, фиксируются соответственно во входном 1 и выходном 8 регистрах по заднему фронту синхроимпульсов на входе 13.

выходы блока памяти подключены к входам информационных разрядов выходного регистра, выходы информационных разрядов которого являются информационными выходами устройства, входы синхронизации входного и

Задержка слов ма ссива определяется коэф- 35 выходного регистров соединены и являются фиииентом пересчета, входящего в формиро-входом синхронизации устройства, отличаюкят(ль fiщееся тем, что, с целью повышения достоверности задержанной устройством информации Очередное информационное слово задерживаемого массива записывается в блок 7

вместе с соответствующим признаком, ко- 40 второй выч-итатели, первый, второй и третий торый определяет превышает ли разность блоки сравнения, причем вход синхрониза- и предыдущего слов некотороеции формирователя адреса, входы синхронизации первого и второго буферных регистров и вход записи-чтения блока памяти подключены к входу синхронизации устблока 5 сравнения. Если разность дан- 5 ройства, выход входного регистра подклю- ного и предыдущего слов массива по мо-чен к информационному входу первого буферного регистра и первому входу первого вычитателя, второй вход которого соединен

в него введены первый и второй буферные регистры,-регистр признака, первый и

данного и предыдущего слов некоторое пороговое значение, которое хранится в регистре 3. Вычисление признака осуществляется с помощью вычитателя 4 и первого

дулю не превышает значения порога, то на выходе блока 5 устанавливается сигнал логического «О если же произощло превы- щение порогового значения, то на выходе блока 5 появляется сигнал логической «1. Аналогично вычисляется признак для основных информационных разрядов слова, считанного из блока 7 в выходной регистр 8. Вычисление осуществляется с помо50

с выходом первого буферного регистра, выходы первого и второго вычитателей подключены соответственно к первым входам первого и второго блоков сравнения, вторые входы -которых соединены с выходом регистра признака, выход первого блока сравнения подключен к контрольному входу ЩЫС1 буферного регистра 9, вычитателя 11 и 55 блока памяти, контрольный выход которого блока 10 сравнения. Признак, вычислен-соединен с входом контрольного разряда выный для задержанного информационного ходного регистра, выходы информационных слова, сравнивается на блоке 12 с призна-разрядов выходного регистра подключены

ком, вычисленным для этого же слова до записи его в блок 7 памяти.

При нормальной работе устройства или при незначительном искажении слова (искажение младших разрядов) признаки, вычисленные до записи и после чтения слова, совпадают и на выходе блока 12 удерживается сигнал логического «О. Если же в процессе задержки произошло значительное искажение информационного слова (искажение, его старших разрядов), которое приво- дит к переходу в ту или иную сторону через границу порога скорости изменения функции (модуля разности значений данблока 12 появляется сигнал логической «1, свидетельствующий о большой погрешности

данного информационного слова, тем самым повышая достоверность выдаваемой информации.

Формула изобретения

20

25

Устройство для задержки цифровой информации, содержащее входной регистр, формирователь адреса, блок памяти и выходной регистр, причем вход входного регистра является информационным входом устройства, выход входного регистра подключен к информационному входу блока памяти, адресный вход которого соединен с выходом

зо Формирователя адреса, информационные

ности задержанной устройством информации

второй выч-итатели, первый, второй и третий блоки сравнения, причем вход синхрониза- ции формирователя адреса, входы синхронив него введены первый и второй буферные регистры,-регистр признака, первый и

с выходом первого буферного регистра, выходы первого и второго вычитателей подключены соответственно к первым входам первого и второго блоков сравнения, вторые входы -которых соединены с выходом регистра признака, выход первого блока сравнения подключен к контрольному входу блока памяти, контрольный выход которого соединен с входом контрольного разряда вы1383327

34

к информационным входам второго буфер-контрольного разряда выходного регистра ного регистра и первому входу второгоподключены соответственно к первому и вто- вычитателя, второй вход которого соединенрому входам третьего блока сравнения, с выходом второго буферного регистра,выход которого является выходом «Невыход второго блока сравнения и выходдостоверная информация устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки информации с контролем | 1986 |

|

SU1383323A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

Изобретение относится к вычислительной технике и может быть использовано в блоках задержки цифровой информации. Цель изобретения - повышение достоверности задержанной устройством информации. Устройство содержит входной 1 и выходной 8 регистры, первый 2 и второй 9 буферные регистры, регистр 3 признака, первый 4 и второй 11 Бычитатели, формирователь 6 адреса, блок 7 памяти, первый 5, второй 10 и третий 12 блоки сравнения. Устройство позволяет различать значительное искажение информационных слов задерживаемого массива, приводящее к изменению заранее вычисленной (до записи в блок памяти) признаковой информации, однозначно определяющей скорость изменения функции, которую представляет данный массив. Несовпадение признаков, вычисленных до и после задержки, свидетельствует о недопустимом искажении информации. 1 ил. с S (Л

| Запоминающее устройство | 1975 |

|

SU556495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программируемой задержки информации | 1984 |

|

SU1193653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-13—Подача