бмднои cutnaetf- г -4

Сиянал n/MMSMua

facffHfma о дискретизации

со со

оо г

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| СПОСОБ СОПРОВОЖДЕНИЯ ЦЕЛИ МОНОИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ | 1997 |

|

RU2117960C1 |

| ЦИФРОВОЙ МОДЕМ | 2001 |

|

RU2218666C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМНИК С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ ДЛЯ ПРИЕМА КВАДРАТУРНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПОВЫШЕННОЙ СТРУКТУРНОЙ СКРЫТНОСТИ | 2013 |

|

RU2544767C1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- ние точности дискриминации фазы. Устр-во содержит г-р 1 эталонной частоты, перемножитёли 2 и 4, фильтр 5 промежуточной частоты, фильтры 6 и 7 нижних частот, АЦП 9, комплексный перемножитель 10, ключ 11, накапливающий сумматор (НС) 12, блоки 13 и 14 постоянной памяти, цифровые фильтры 15 и 22 нижних частот. Введены сумматоры 16 и 23, НС 17, 19, 24 и 26, ключи 18,25,29 и 30, ДАЛ 20 и 27, у-ли 21 и 28, эл-т 31 задержки и делитель 32 частоты. Устр-во работает в двух режимах: режиме измерения, в к-ром выполняет функцию фазового дискриминатора, и режиме компенсации, служащем для повьшения точности работы в 1-м режиме. Устр-во переводится во 2-и режим подачей на вход сигнала управления, к-рый, поступая на управляющий вход ключа 29, закрывает его. В результате сигнал с тактовой частотой не поступает на управляющий вход ключа 11, а на вход НС 12 не поступают числа с входа кода частоты опорного сигнала. Сигнал управления с входа подается на вход сброса НС 12, в результате чего НС 12 переводится в нулевое состояние. 2 ил. м« & ел

Лж частоты ;«парною fofttafa

Изобретание относится к -радиотехнике и может быть использовано в цифровых приемниках.

Цель изобретения - повышение точности дискриминацгн фазы.

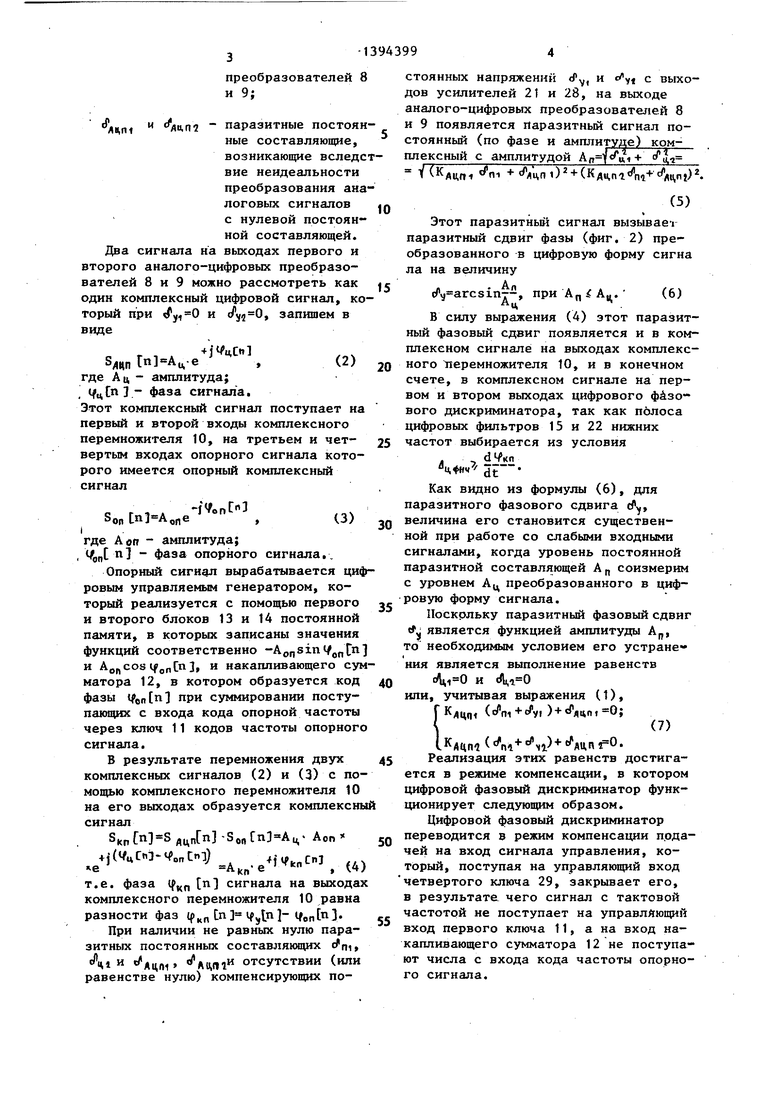

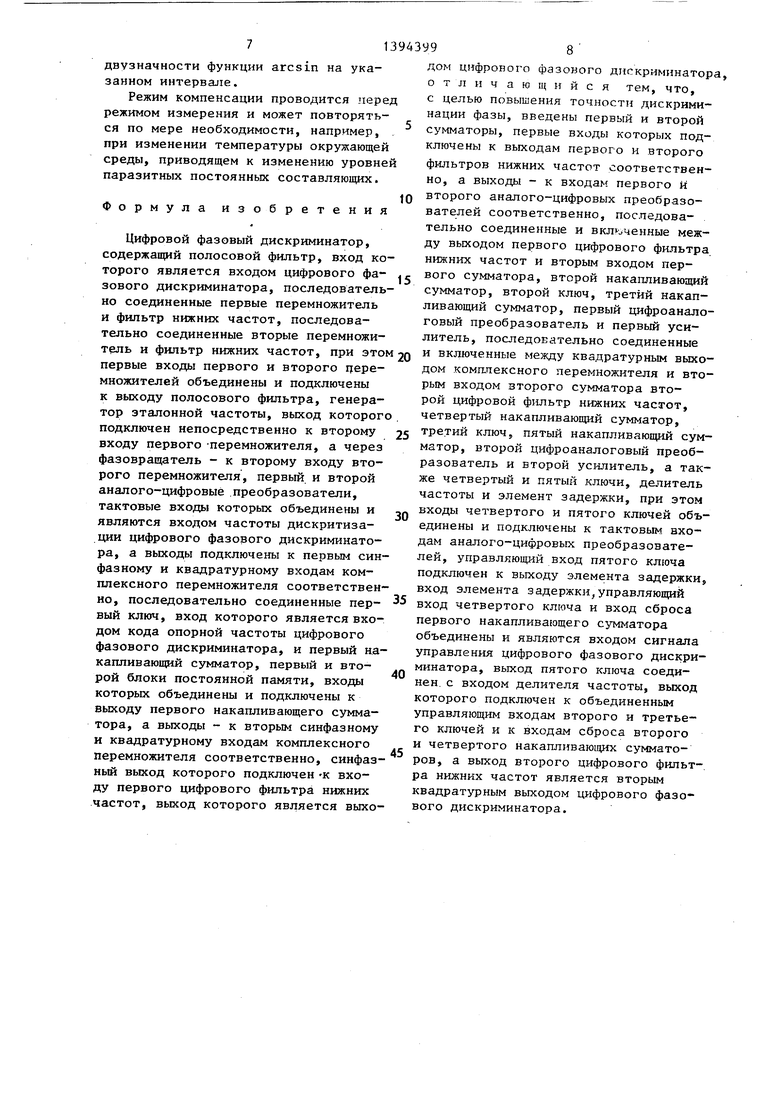

На фиг. 1 приведена структурная электрическая схема предложенного фазового дискриминатора; на фиг. 2 - векторная диаграмма, поясняющая влияние паразитных постоянных составляющих сГц, и сГц 5 на выходе первого и второго ангшого-цифрового преобразователей на фазу (рц Вектора на выходах комплексного перемножителя.

Цифровой фазовый дискриминатор содержит генератор 1 эталонной частоты, первый перемножитель 2, фазовращатель 3, второй перемножитель 4, фильтр 5 промежуточной частоты, первый фильтр 6 нижних частот, второй фильтр 7 ншкних частот, первый аналого-цифровой преобразователь 9, комплексный перемножитель 10, первый ключ 11, первый накапливающий сумматор 12, первый блок 13 постоянной памяти, второй блок 14 постоянной памяти, первый цифровой фильтр 15 нижних частот, первый сумматор 16, второй накапливающий сумматор 17, второй юпоч 18, третий накапливаюац1й сумматор 19, ие)1зый цпфроаналоговый преобразователь 20, первый усилитель 21 второй цифровой фильтр 22 }1ижних частот, второй сумматор 23, четвертый накапливающий сумматор 24, третий ключ 25, пятый накапливающий сумматор 26, второй цифроаналоговый преоб- разЪватель 27, второй усилитель 28, четвертый ключ 29, пятый ключ 30, элемент 31 задержки и делитель 32 часTOTijI,

Цифровой фазовый дискриминатор работает следующим образом.

Цифровой фазовый дискриминатор ра ботет в двух рел имах: в .режиме измерения, в KojopoM выполняет функцию фазового дискриминатора, в режиме компенсации, служащем для повышения точности работы в режиме измерения.

Цифровой фазовый дискриминатор в режиме измерения работает следующим образом.

Генератор 1 эталонной частоты генерирует синусоидальный сигнал постоянной частоты fjT поступающий непосредственно па первый вход первого перемножителя 2 и через фазовращател 3, обеспечивающий поворот фазы на 90

0

5

0

5

поступающий на вход второго перемножителя 4. На другие входы перемножителей 2 и 4 поступает сигнал с выхода фильтра 5 промежуточной частоты f , вход которого соединен с входом входного сигнала, причем .

В результате перемножения входного сигнала, прошедшего фильтр 5 промежуточной частоты, с синфазным и квадратурным сигналами эталонной частоты f ,, на вьтодах первого и второго перемножителей 2 и 4 образуются соответственно синфазный и квадратурный сигналы разностной j и суммарной fj, g частот. Через первый и второй фильтры 6 и 7 нижних частот с полосой и ф проходят только соответственно синфазный и квадратурный сигналы разностной частоты fр fgjj-f 5-rj т.е. входной сигнал переносится в область нижних частот. При этом должно выполняться.условие

.+ й.

Зт (

эт

Чнч

0

5

0

5

0

5

На выходах первого и второго фильтров 6 и 7 нижних частот могут также иметь место паразитные постоянные составляющие соответственно cff,, и t/ ni возникающие вследствие неидеальности первого и второго перемножителей 2 и 4.

Таким образом, на второй вход первого сумматора 16 поступает сумма синфазного сигнала разностной частоты f р с постоянной составляющей ni а на второй вход второго сумматора 23 поступает сумма квадратурного сигнала разностной частоты fр с постоянной составляющей сС,.

На первые входы первого и второго сумматоров 16 и 23 с выходов соответственно первого и второго усилителей 21 и 28 поступают соответственно постоянные напряжения с/ у и Л В итоге на выходах первого и второго сумматоров 16 и 23 постоянные составляю- 1цие равны соответственно с, «/|,,+ f, С1 па уг После преобразования в цифровую форму аналоговых сигналов, поступающих на вторые входы первого и второго аналого-цифровых преобразователей 8 и 9, на их выходах цифровые сигналы имеют постоянные составляющие, равные соответственно

( J ni+ ) ;

Щ Клцп2() + с дцп5 , (1)

4цп-1 коэффициейты передачи аналого-цифровых

преобразователей 8 и 9;

стоянных напряжении «f, и с выходов усилителей 21 и 28, на выходе аналого-цифровых преобразователей 8 и 9 появляется Паразитный сигнал постоянный (по фазе и амплитуде) ком- возникаю1цие вследст- плексный с амплитудой ,1

лип паразитные постоянные составляющие,

У(КАЦ„, П1 ) + (КдцпгЛа+ лцп1)2.

вне неидеальности преобразования ана логовых сигналов с нулевой постоянной составляющей. Два сигнала на выходах первого и второго аналого-цифровых преобразователей 8 и 9 можно рассмотреть как один комплексный цифровой сигнал, который при «Гу,0 и запишем в виде

/ЩП

(2)

где Ац - амплитуда; . 3 - фаза сигнала. Этот комплексный сигнал поступает на первый и второй входы комплексного перемножителя 10, на третьем и четвертым входах опорного сигнала которого имеется опорный комплексный сигнал

Son ,

(3)

где А on - амплитуда;

t/flpt 111 фаза опорного сигнала..

Опорный сигнал вырабатывается цифровым управляемым генератором, который реализуется с помощью первого и второго блоков 13 и 14 постоянной памяти, в которых записаны значения функций соответственно -AonSini/ ntJ l и AonCosif nCn, и накапливающего сумматора 12, в котором образуется код фазы при суммировании поступающих с входа кода опорной частоты через ключ 11 кодов частоты опорного сигнала.

В результате перемножения двух комплексных сигналов (2) и (3) с помощью комплексного перемножителя 10 на его выходах образуется комплексный сигнал

8кпС 8дцп п -5опСпЗ Ац- Aon

.,-Ксп о„ст},,„сп1

т.е. фаза if сигнала на выходах комплексного перемножителя 10 равна разности фаз tf п tn if,,ln -ifont }

При наличии не равных нулю паразитных постоянных составляющих е щ Л и « АЦШ .щи отсутствии (или равенстве нулю) компенсирующих по

(4)

10

а . frо

а

ифо jj й я умдыго

о0ный

ах а

и У(КАЦ„, П1 ) + (КдцпгЛа+ лцп1)2.

(5)

Этот паразитньй сигнал вызывае паразитный сдвиг фазы (фиг. 2) преобразованного в цифровую форму сигна ла на величину

(/ v(arcsin--, при . (6) Ац

В силу выражения (4) зтот паразитный фазовый сдвиг появляется и в комплексном сигнале на выходах комплекс20 ного еремножителя 10, ив конечном счете, в комплексном сигнале на первом и втором выходах цифрового фАзо- вого дискриминатора, так как полоса цифровых фильтров 15 и 22 нижних

25 частот выбирается из условия

л , °и, 5t

Как видно из формулы (6), для паразитного фазового сдвига rf,

30 величина его становится существенной при работе со слабыми входными сигналами, когда уровень постоянной паразитной составляющей А „ соизмерим с уровнем Ац преобразованного в цифровую форму сигнала.

Поскрльку паразитный фазовый сдвиг ft является функцией амплитуды А, то необходимым условием его устранения является выполнение равенств

40( и

или, учитывая выражения (1), Клцп« (« ni+cfy, ) +

Клцп

(7)

Attnivd n + n +t AUnrO.

45

50

Реализация этих равенств достигается в режиме компенсации, в котором цифровой фазовый дискриминатор функционирует следующим образом.

Цифровой фазовый дискриминатор переводится в режим компенсации п.ода- чей на вход сигнала управления, ко- 4) торый, поступая на управляющий вход четвертого ключа 29, закрывает его, в результате чего сигнал с тактовой частотой не поступает на управляющий вход первого ключа 11, а на вход накапливающего сумматора 12 не поступа ют числа с входа кода частоты опорного сигнала.

55

Сигнал управления с входа подается на вход сброса накапливающего сумматора 12,° в результате чего этот накапливаюпйй сумматор переводится в нулевое состояние.

Нулевому состоянию накапливающего сумматора 12 соответствуют значения чисел и на выходах соответственно первого и второго блоков 13 и 14 постоянной памяти.

В этом время постоянные составляющие на первых синфазном и квадратурном входах комплексного перемножителя 10 соответственно равны паразитнымjj На управляющий вход пятого ключа 30

постоянным составляю1дим на выходах соответственно первого и второго аналого-цифровых преобразователей 8 и 9:

и, а,,; и, 4.1.

Сигналы Uj,j( и на синфаз- ном и квадратурном выходах комплексного перемножителя 10 равны (по пра вилу перемножения комплексных чисел

UBM ci UtU4- u3;

,из.

В силу равенства и ,„ сигнал на синфазном выходе комплексного перемножителя, а следовательно, и на первом выходе устройства, зависит только от уровня паразитной по- СТОЯН1ГОЙ на выходе первого аналого- 1 ифрового преобразователя 8. Аналокомплексного перемножителя 10, а следовательно, и на втором выходе цифрового фазового дискриминатора только зависит от уровня паразитной постоянной составляющей на выходе второго аналого-цифрового преобразователя 9, т.е.

BVIXI А оп Ugvix di i Aon Компенсация паразитных постоянных составляющих /ц7 производится путем введения двух петель регулирования с отрицательной обратной связью Первая петля регулирования замыкает выход первого цифрового фильтра 15 нижних частот с первым входом nepieoro сумматора 16 через последовательно включенные второй накапливающий сумматор 17, второй ключ 18, третий накапливающий сумматор 19, первый,циф- роаналоговый преобразователь 20 и первый усилитель 21.

tUf

вмкСпЛ

тогда как наличие

Вторая петля регулирования замыкает выход второго цифрового фильтра 2255лишь синфазной составляющей U ,, нижних частот с первым входом второ- Ад,, sin tf jj,nj не позволяет одного сумматора 23 через последователь-значно определить фазу выходного сиг- но соединенные четвертый накапливаю-нала для углов - fgi. из-за

щий сумматор 24, третий ключ 25, пятый накапливающий сумматор 26, второй цифроанапоговый преобразователь 27 и второй усилитель 28.

Считывание с помощью ключей 18 и 25 чисел соответственно из накапли- ваю1цих сумматоров 17 и 24 и их сЬрос производится периодически с частотой регулирования fa/N, где N - коэффи- ент деления делителя 32 частоты, на вход которого поступает сигнал с входа тактовой частоты через открытый в режиме компенсации пятый ключ 30.

5

Q

5

0

5

0

сигнал управления поступает через элемент 31 задержки, с помощью которого замыкание петель регулирования производится лишь после того, как сигналы на выходе первого и второго цифровых фильтров 15 и 22 нижних частот соответствуют значениям , U4.Aon опорного сигнала в режиме компенсации.

После окончания переходных процессов в обеих петлях регулирования в накапливающих сумматорах 19 и 26 установятся значения чисел, соответствующие появлению на первых входах первого и второго сумматоров 16 и 23 компенсирующих напряжений соответственно с и c/Vt, при которых выполняются равенства (7). Числа в накапливающих сумматорах 19 и 26 и напряжения еГу и с/ . выходе усилителей 21 и 28 останутся постоянными при переходе из режима компенсации в режим измерения, так как при этом закрывается ключ 30, и через него на делитель 32 частоты не поступает сигнал частоты дискретизаций, следовательно, в режиме измерения ключи 18 и 25 также останутся в закрытом состоянии.

Наличие второго цифрового фильтра 22 нижних частот, соединеного своим входом с вторым квадратурным выходом комплексного перемножителя 10, позволяет получить квадратурную составляющую комплексного сигнала и, тем самым, однозначно определить фазу выходного комплексного сигнала S .nxfn1

tUf

вмкСпЛ

тогда как наличие

5лишь синфазной составляющей U ,, Ад,, sin tf jj,nj не позволяет однозначно определить фазу выходного сиг- нала для углов - fgi. из-за

7

двузначности функции arcsin на указанном интервале.

Режим компенсации проводится .черед режимом измерения и может повторяться по мере необходимости, например, при изменении температуры окружающей среды, приводящем к изменению уровней паразитных постоянных составляющих.

Формула изобретения

139

Цифровой фазовый дискриминатор, содержащий полосовой фильтр, вход которого является входом цифрового фа АС зового дискриминатора, последовательно соединенные первые перемножитель и фильтр нижних частот, последовательно соединенные вторые перемножитель и фильтр нижних частот, при этом 20 первые входы первого и второго ijepe- множителей объединены и подключены к выходу полосового фильтра, генератор эталонной частоты, выход которого .

подключен непосредственно к второму входу первого перемножителя, а через фазовращатель - к второму входу второго перемножителя, первый и второй аналого-цифровые .преобразователи, тактовые входы которых объединены и являются входом частоты дискритиза- ции цифрового фазового дискриминатора, а выходы подключены к первым синфазному и квадратурному входам комплексного перемножителя соответственно, последовательно соединенные пер вый ключ, вход которого является входом кода опорной частоты цифрового фазового дискриминатора, и первый накапливающий сумматор, первый и второй блоки постоянной памяти, входы которых объединены и подключены к выходу первого накапливающего сумматора, а выходы - к вторым синфазному

и квадратурному входам комплексного перемножителя соответственно, синфазный выход которого подключен К входу первого цифрового фильтра нижних частот, выход которого является выхо

10

АС20 .

9АЗУ98

дом цифрового фазового дискриминатора, отличающийся тем, что, с целью повышения точности дискриминации фазы, введены первый и второй сумматоры, первые входы которых подключены к выходам первого и второго фш1ьтров нижних частот соответственно, а выходы - к входам первого и второго аналого-цифровых преобразователей соответственно, последовательно соединенные и вкл ченные между выходом первого цифрового фильтра нижних частот и вторым входом первого сумматора, второй накапливающий сумматор, второй ключ, третий накапливающий сумматор, первый цифроанало- говый преобразователь и первый усилитель, последовательно соединенные и включенные между квадратурным выходом .комп-пексного перемножителя и вторым входом второго сумматора второй цифровой фильтр нижних частот, четвертый накапливающий сумматор, тре.тий ключ, пятый накапливающий сумматор, второй цифроаналоговый преобразователь и второй усилитель, а также четвертый и пятый ключи, делитель частоты и элемент задержки, при этом входы четвертого и пятого ключей объединены и подключены к тактовым входам аналого-цифровых преобразователей, управляющий вход пятого ключа подключен к выходу элемента задержки, вход элемента задержки,управляющий вход четвертого ключа и вход сброса первого накапливаЕощего сумматора объединены и являются входом сигнала управления цифрового фазового дискриминатора, выход пятого ключа соединен, с входом делителя частоты, выход которого подключен к объединенным управляющим входам второго и третьего ключей и к входам сброса второго и четвертого накапливающих сумматоров, а выход второго цифрового фильт-, ра нижних частот является вторым квадратурным выходом цифрового фазового дискриминатора.

25

30

35

40

45

фиъ.г

| Larimore W.E | |||

| Synthesis of digital phase - loocked loop | |||

| EASOOH Rec, Get, 1968, p | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1988-05-07—Публикация

1986-04-14—Подача