Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| УСТРОЙСТВО ДЛЯ ПОРОГОВОГО ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1993 |

|

RU2081513C1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи и обработки информации, организованной в пакеты.позволяет повысить достоверность декодирования при приеме из дискретного несимметричного канала связи. Декодер содержит коммутатор 1, регистр 2, формирователь 3 проверок, вычислитель 4 числа единиц, сумматор 9 и компаратор 10. Благодаря введению вычислителя 5 числа нулей, вычислителя 6 весовых коэффициентов, вычислителя 7 порога и корректора 8 жесткого значения проверок обеспечивается снижение вероятности ошибочного декодирования символа по сравнению с прототипом более чем вдвое. 3 ил.

VJ

Ч) СП

Изобретение относится к вычислитель- ной технике и технике связи и может быть использовано в системах передачи и обработки информации, организованной в пакеты.

Цель изобретения - повышение досто- верности декодирования при приеме из дискретного несимметричного канала связи.

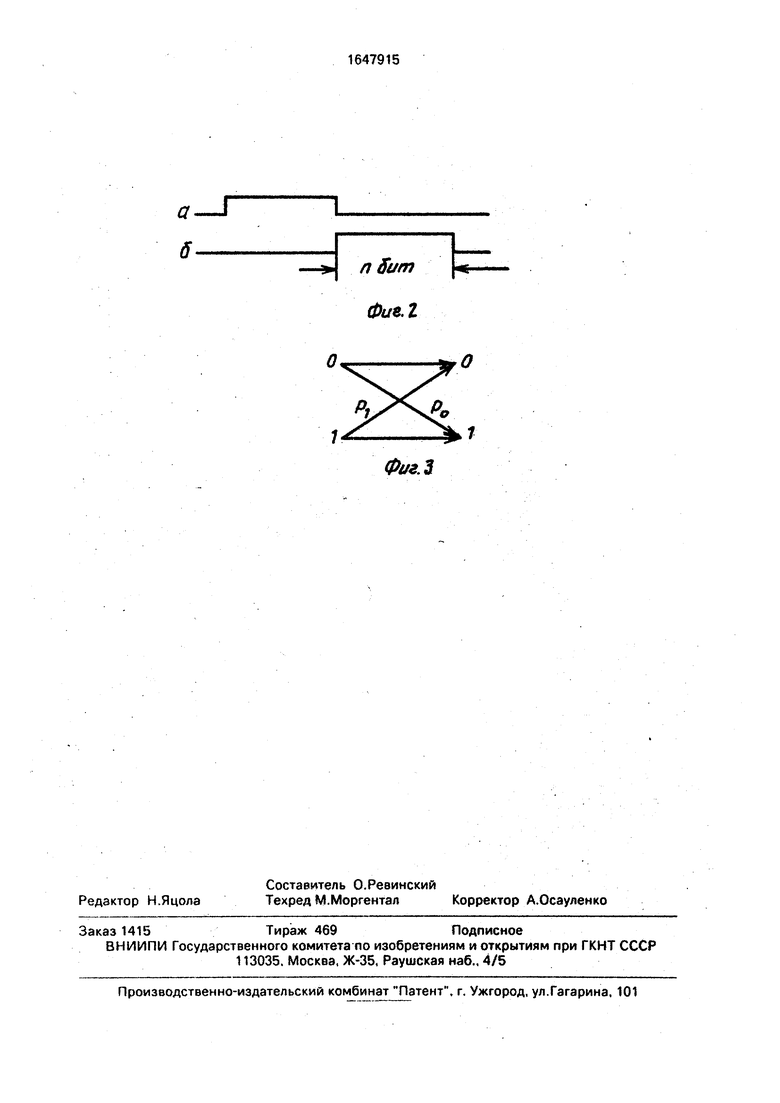

На фиг.1 приведена блок-схема декодера; на фиг.2 - временные диаграммы его работы; на фиг.З - модель несимметричного канала связи.

Вероятностный мажоритарный декодер содержит коммутатор 1, регистр 2, формирователь 3 проверок, вычислитель 4 числа единиц, вычислитель 5 числа нулей, вычислитель 6 весовых коэффициентов, вычислитель 7 порога, корректор 8 жестких значений проверок, сумматор 9 и компаратор 10. На фиг.1 обозначены информационный и управляющий входы 11 и 12 декодера. Тактовый вход регистра 2 не показан.

Вероятностный мажоритарный декодер предназначен для обработки информации, закодированной циклическим кодом (n,k,d) с параметрами: п - длина кода, k - количество информационных символов, d - число разделенных проверок (расстояние Хем- минга).

Коммутатор 1 и регистр 2 служат для ввода блока информации и его циклического сдвига в процессе декодирования, регистр 2 содержит п элементов.

Формирователь 3 проверок служит для формирования жестких значений проверок и выполнен на d ггм-входовых сумматорах по модулю два:

mi М, 1 1

где mi - число символов, входящих в i-ю разделенную проверку (на фиг.1 указаны размерности входов и выходов соответствующих блоков).

Вычислитель 4 числа единиц служит для определения числа i единиц в каждой из разделенных проверок и выполнен на d mi- входовых полных сумматорах.

Вычислитель 5 числа нулей служит для вычисления числа нулей в каждой из разделенных проверок и выполнен на d программируемых постоянных запоминающих устройствах (ППЗУ). В каждом i-м ППЗУ производится вычисление значения числа нулей в каждой из разделенных проверок:

п mi - d.

где mi - число символов, входящих в i-ю разделенную проверку, т.е. значение, вводимое в каждый 1-й ППЗУ;

li - число единиц t-й проверки, т.е. значение, получаемое на выходе 1-го полного сумматора вычислителя 4.

Вычислитель 6 весовых коэффициентов выполнен на d ППЗУ. В каждом i-м ППЗУ производится вычисление значения W; весового коэффициента, пропорционального надежности i-й проверки, который определяется как

15

Ч л./-} - 2Р,Л|1Г1 -2P1Y1 11 W, log-1- -ЈL°1 L ЈЈ12 ,

1 -(1 -2Р0)(1 -2P1)mt

где li - значение, получаемое на выходе 1-го полного сумматора вычислителя 4; п (гоНО значение, получаемое на выходе 1-го ППЗУ вычислителя 5;

РО - вероятность ошибочного приема 0;

Рт - вероятность ошибочного приема 1.

Значения Р0 и Pi определяются для дан- ного канала и вводятся в вычислитель 6 как исходные данные.

Вычислитель 7 порога представляет собой d-входовой полный сумматор, вычисляющий значение порога:

S d w.

7

i 1

где W - значение, получаемое на }-м выходе вычислителя 6 весовых коэффициентов.

Корректор 8 жесткого значения проверок выполнен на d перемножителях. В каждом I-м перемножителе производится вычисление скорректированного значения для каждой 1-й проверки, равного

Ci Bi Wi,

где Bi - значение i-й проверки, получаемого на выходе 1-го сумматора mod 2 форми- рователя 3 проверок;

Wt - значение, получаемое на i-м выходе вычислителя б весовых коэффициентов.

Сумматор 9 представляет собой d-входовой полный сумматор.

На выходе компаратора образуется значение 1, если значение 2 с выходов сумi 1

матора 9 превышает порог Z с вычислителя 7. т.е. образуются символы декодированной последовательности.

Вероятностный мажоритарный декодер работает следующим образом.

На вход 11 декодера поступает блок информации из п бит, где п - длина указанного

KOAa(n.k.d). Коммутатор 1 по команде управляющего сигнала на входе 12 (фиг.2а) переписывает эту информацию в течение п тактов (первый цикл) а регистр 2 длиной п. После чего коммутатор 1 прекращает по- ступление информационного потока и декодер переключается (фиг.26) в течение следующих п тактов на циркуляцию информации, записанной в регистре 2.

Из циркулирующих символов для каж- дого символа формирователем 3 формируется d разделенных проверок по m символов в i-й проверке, i 1,d.

На каждом такте на выходе каждого 1-го сумматора по модулю два формирователя 3 проверок образуется значение 1-й проверки BI и подается на вход 1-го neper-ножителя корректора 8 жесткого значения проверок. Одновременно с этим на выходе каждого 1-го сумматора вычислителя 4 образуется значение веса (числа единиц) i-й проверки I,, которое вместе со значением числа нулей в i-й проверке п (mHi) с выхода вычислителя

5подается на входы 1-го ППЗУ вычислителя

6весовых коэффициентов.

В качестве исходных данных вводятся: значения mi - числа символов, входящих в i-ю разделенную проверку в каждое i-e ППЗУ вычислителя 5; значения Р0 и Pi - вероятности ошибки нуля и единицы - во все ППЗУ вычислителя 6 весовых коэффициентов.

С выхода каждого i-ro ППЗУ вычислителя 6 весовых коэффициентов на каждом такте значение Wi - весового коэффициента, пропорционального надежности i-й проверки, подается на входы вычислителя 7 порога и корректора 8 жесткого значения проверок. В вычислителе 7 порога производится вычисление значения

Sdw,

i 1

которое подается с выхода вычислителя 7 на второй вход компаратора 10. На вход каждого 1-го перемножителя корректора 8 жесткого значения проверок подаются W, - значения весовых коэффициентов и Bi - жесткие значения проверок. В корректоре 8 жесткого значения проверок производятся вычисления величин Ci Bi -Wi для каждой i-й разделенной проверки. Эти значения с выхода корректора 8 подаются на входы сумматора 9. В сумматоре 9 производится

d

вычисление значения 2) С|. На компараi 1

5

10

15 0

5

0

5 0

5

-Q е

торе 10 производится потактовое сравнение этой ааличины со значением порога Z, подаваемым с выхода вычислителя 7 порога.

d

В случае, если Ci Z на выходе ком1 1

паратора 10 образуется символ 1. Выход компаратора 10 является информационным выходом, на котором образуются символы декодированной последовательности.

Моделирование для циклического кода (73, 45, 10) при обьеме переданной информации 10000 кодовых слов и вероятности искажения нулевого символа Р0 0,001 показало, что при вероятности искажения единичного символа Pi 0,25 вероятность ошибки символа на выходе предлагаемого декодера по сравнению с известным уменьшается более чем вдвое, а при Pi 0,05 - более чем в пять раз.

Формула изобретения

Вероятностный мажоритарный декодер, содержащий коммутатор, первый информационный и управляющий входы которого являются соответственно информационным и управляющим входами декодера, выход коммутатора соединен с входом регистра, параллельные и последовательный выходы которого подключены соответственно к входам формирователя проверок и второму информационному входу коммутатора, вычислитель числа единиц, сумматор, выходы которого соединены с первыми входами компаратора, отличающийся тем, что, с целью повышения достоверности декодирования при приеме из дискретного несимметричного канала связи, в декодер введены вычислитель числа нулей, вычислитель весовых коэффициентов, вычислитель порога и корректор жесткого значения проверок, входы вычислителя числа единиц подключены к параллельным выходам регистра, выходы формирователя проверок соединены с первыми входами корректора жесткого значения проверок, выходы вычислителя числа единиц подключены к первым входам вычислителя весовых коэффициентов и входам вычислителя числа нулей, выходы которого соединены с вторыми входами вычислителя весовых коэффициентов, выходы которого подключены к входам вычислителя порога и вторым входам корректора жесткого значения проверок, выходы которых соединены соответственно с вторыми входами компаратора и входами сумматора, выход компаратора является выходом декодера.

а 6

/7 Sum

Фие.1

Фиг.Ъ

| Колесник В.Д., Мирончиков Е.Т | |||

| Декодирование циклических кодов | |||

| - М.: Связь, 1968, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-15—Подача