(21 ) 408А887/24-2А

(22) 03.06.86

(46) 23.05.88. Бюл. N 19

(72) В.Л.Кошкин, Э.Т.Горбенко,

Ю.А.Симецкий и А.И.Лапаиди}

(53) 621.503.55(088.8)

(56) Авторское свидетельство СССР

№ 408276, кл. , 05 В 19/18, 1973.

Приводы и системы управления для автоматизации ста1гков. - Фирма Сименс. Спец. вьт, 1976.

(34 УСТРОЙСТВО ДЛЯ ПРОГРАМг НОГО УПРАВЛЕНИЯ

(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками. Цель изобретения - расширение функциональных возможностей устройства и сокращение объема оборудования. При этом достигается также упрощение програмг-шрования при

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Устройство для задания циклов в системах цифрового программного управления | 1985 |

|

SU1280575A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство контроля по модулю 9 для программного управления | 1987 |

|

SU1483431A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

(Л

со со 00

00

токарной обработке, при резьбонаре- эании или снятии припуска при работе на станках с ЧПУ. Введение счетчика адреса 4, счетчика числа циклов 5, триггеров 6-8, сумматоров 9, 10, сдвиговых регистров 11, 12, формирователей импульсов 21, 22, 26, эле1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками.

Целью изобретения является расширение функциональных возможностей устройства при одновременном сокращении объема электронного оборудования.

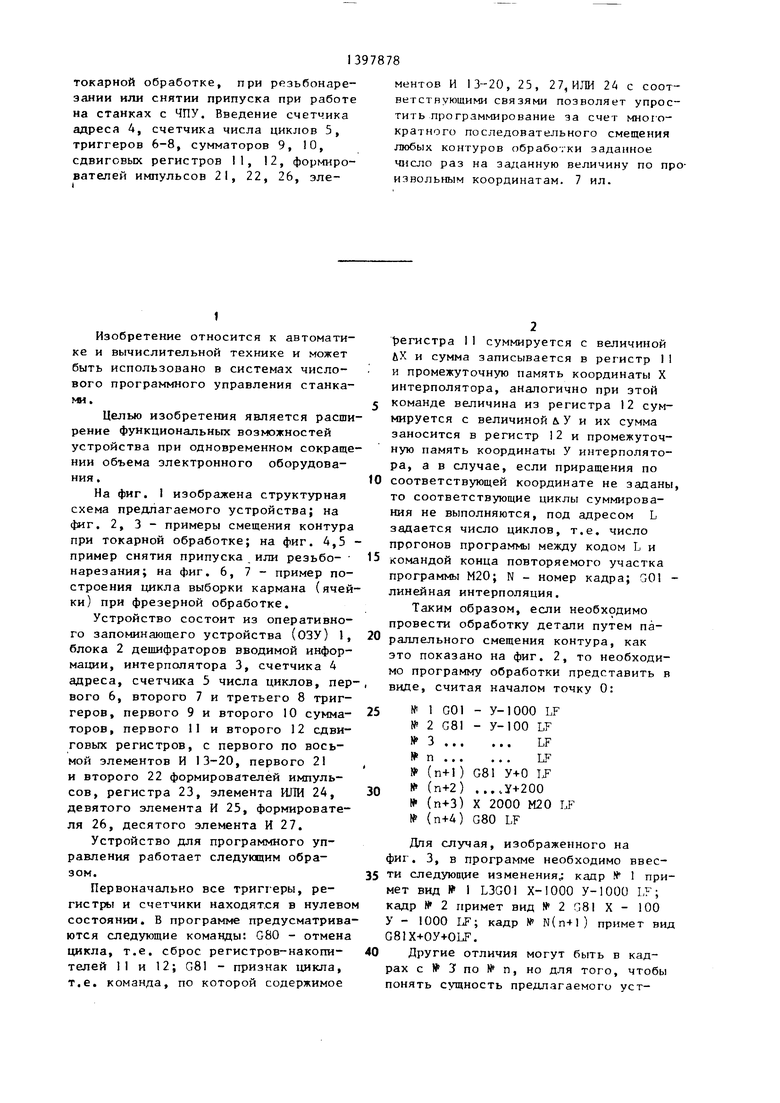

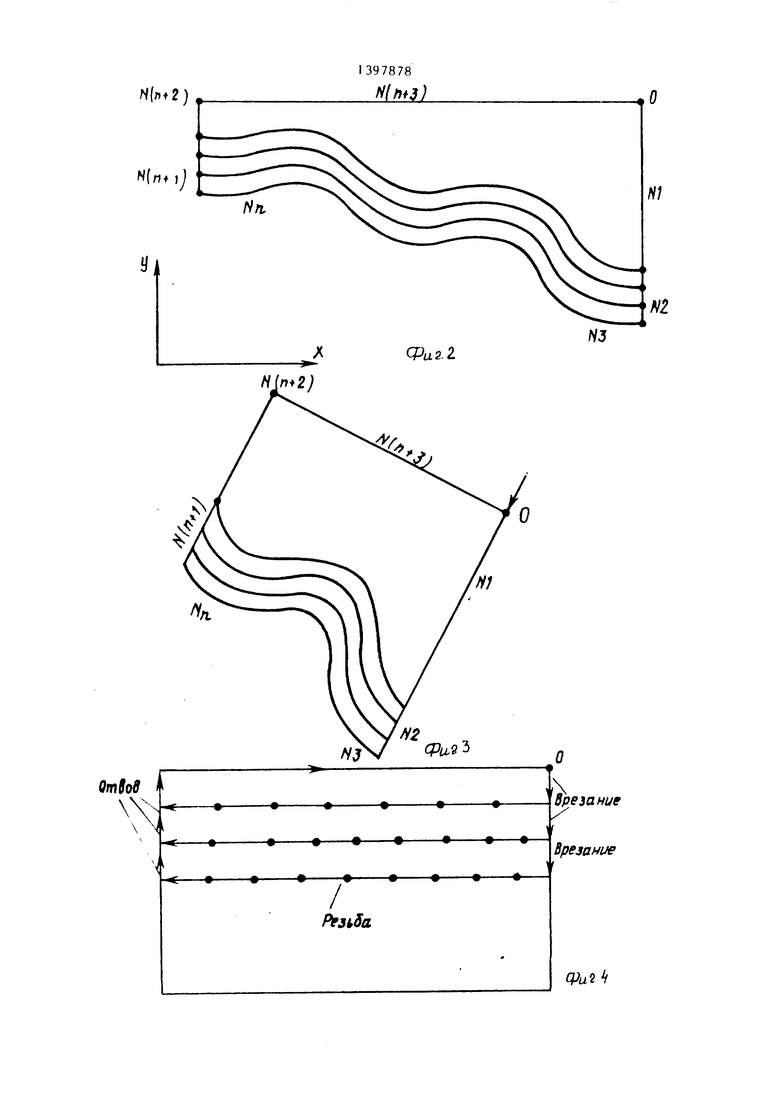

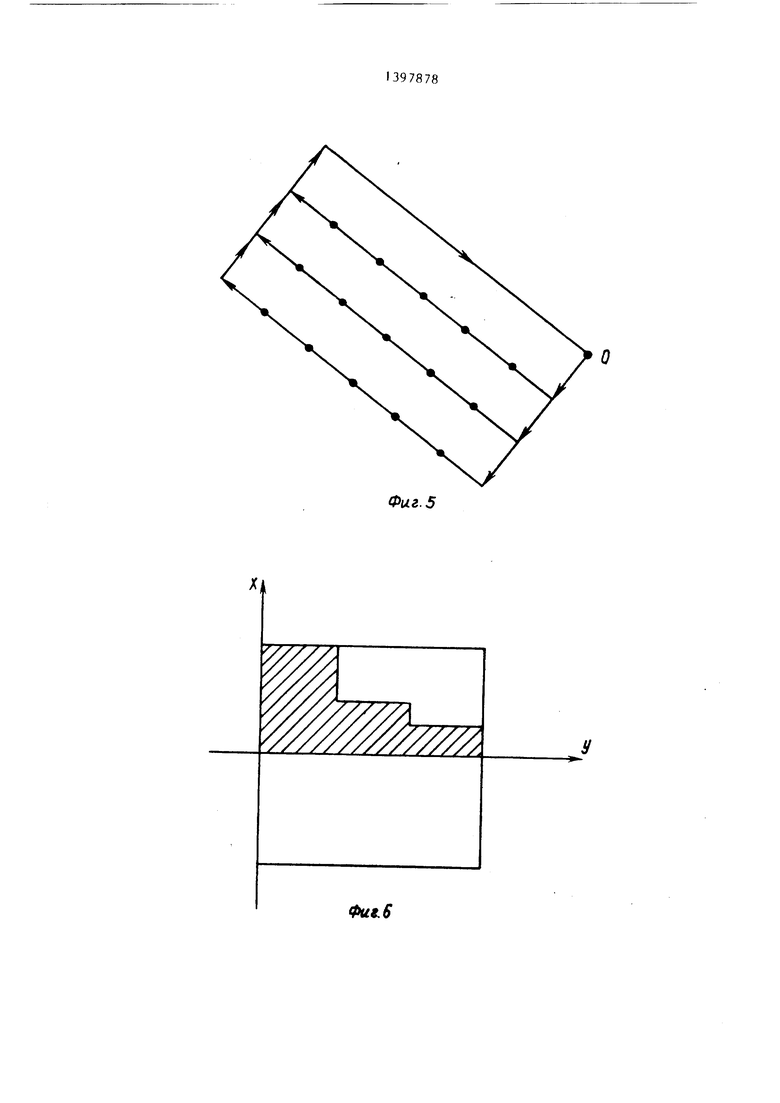

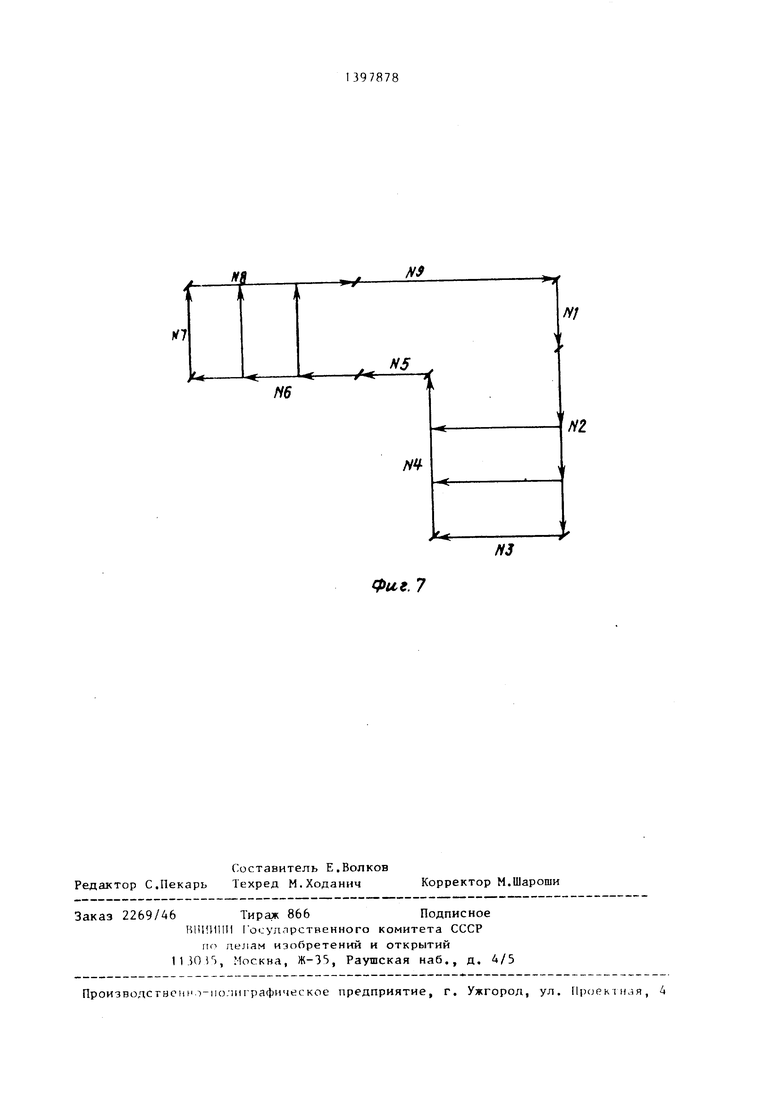

На фиг. I изображена структурная схема предлагаемого устройства; на фиг. 2, 3 - примеры смещения контура при токарной обработке; на фиг. А,5 - пример снятия припуска или резьбо- нарезания; на фиг. 6, 7 - пример построения цикла выборки кармана (ячейки) при фрезерной обработке.

Устройство состоит из оперативного запоминающего устройства (ОЗУ) 1, блока 2 дешифраторов вводимой информации, интерполятора 3, счетчика 4 адреса, счетчика 5 числа циклов, первого 6, второго 7 и третьего 8 триггеров, первого 9 и второго 10 сумма- торов, первого 11 и второго 12 сдвиговых регистров, с первого по восьмой элементов И 13-20, первого 21 и второго 22 формирователей импульсов, регистра 23, элемента ИЛИ 24, девятого элемента И 25, формирователя 26, десятого элемента И 27.

Устройство для программного управления работает следующим образом.

Первоначально все триггеры, регистры и счетчики находятся в нулевом состоянии. В программе предусматриваются следующие команды: G80 - отмена цикла, т.е. сброс регистров-накопи- телей II и 12; G8 - признак цикла, т.е. команда, по которой содержимое

ментов И 13-20, 25, 27, ИЛИ 21 с соответствующими связями позволяет упростить программирование за счет мног о- кратного последовательного смещения любых контуров обработки заданное число раз на заданную величину по произвольным координатам. 7 ил.

регистра 11 суммируется с величиной йХ и сумма записывается в регистр I и промежуточную память координаты X интерполятора, аналогично при этой команде величина из регистра 12 суммируется с величиной л У и их сумма заносится в регистр 12 и промежуточную память координаты У интерполятора, а в случае, если приращения по соответствующей координате не заданы то соответствующие циклы суммирования не выполняются, под адресом L задается число циклов, т.е. число прргонов программы между кодом L и командой конца повторяемого участка программы М20; N - номер кадра; G01 линейная интерполяция.

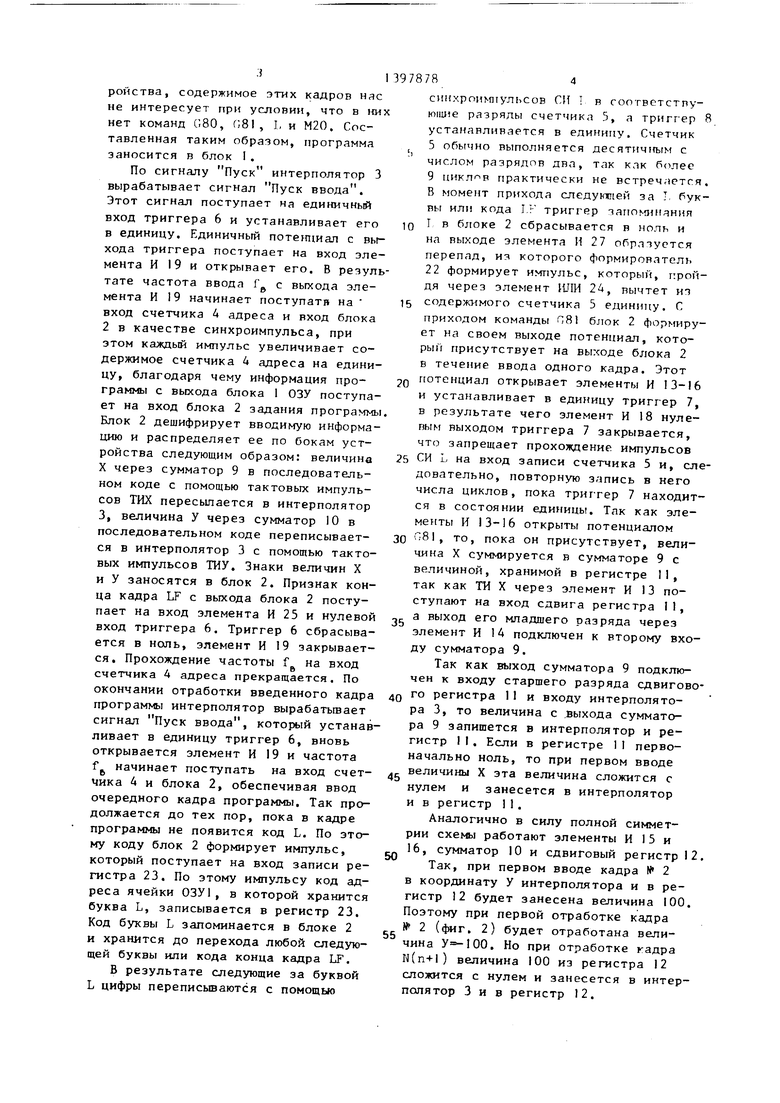

Таким образом, если необходимо провести обработку детали путем параллельного смещения контура, как это показано на фиг. 2, то необходимо программу обработки представить в виде, считая началом точку 0:

№ 1 001 - У-1000 LF № 2 081 - У-100 LF

ЬГ

№ п LF

№ (п+1) 081 У+0 IF (п+2) ....У+200 № (п+3) X 2000 М20 TJ № (п+4) G80 LF

Для случая, изображенного на фиг. 3, в программе необходимо ввести следуюв1ие изменения; кадр № 1 примет вид 1 L3G01 Х-1000 У-1000 LF; кадр № 2 примет вид № 2 G81 X - 100 У - 1000 LF; кадр № N(n4l) примет ви 081X+Oy-t-OLF.

Другие отличия могут быть в кадрах с № 3 по № п, но для того, чтобы понять сущность предлагаемого устронства, содержимое этих кадров нас не интересует при условии, что в ни нет команд G80, 081, I, и М20. Составленная таким образом, программа заносится в блок I.

По сигналу Пуск интерполятор 3 вырабатывает сигнал Пуск ввода. Этот сигнал поступает на единичньй вход триггера 6 и устанавливает его в единицу. Единичный потешшал с выхода триггера поступает на вход элемента И 19 и открывает его. В результате частота ввода Г. с выхода элео

мента И 19 начинает поступатн на вход счетчика А адреса и вход блока 2 в качестве синхроимпульса, при этом каждый импульс увеличивает содержимое счетчика 4 адреса на единицу, благодаря чему информация программы с выхода блока 1 ОЗУ поступает на вход блока 2 задания программы Блок 2 дешифрирует вводимую информацию и распределяет ее по бокам устройства следующим образом: величина X через сумматор 9 в последовательном коде с помощью тактовых импульсов ТИХ пересылается в интерполятор 3, величина У через сумматор 10 в последовательном коде переписывается в интерполятор 3 с помощью тактовых импульсов ТИУ. Знаки величин X и У заносятся в блок 2. Признак конца кадра LF с выхода блока 2 поступает на вход элемента И 25 и нулевой вход триггера 6. Триггер 6 сбрасывается в ноль, элемент И 19 закрывается. Прохождение частоты f на вход счетчика 4 адреса прекращается. По окончании отработки введенного кадра программы интерполятор вырабатьшает сигнал Пуск ввода, который устанавливает в единицу триггер 6, вновь открывается элемент И 19 и частота f- начинает поступать на вход счетD

чика 4 и блока 2, обеспечивая ввод очередного кадра программы. Так продолжается до тех пор, пока в кадре программы не появится код L. По этому коду блок 2 формирует импульс, который поступает на вход записи регистра 23. По этому импульсу код адреса ячейки ОЗУ1, в которой хранится буква L, записывается в регистр 23. Код буквы L запоминается в блоке 2 и хранится до перехода любой следующей буквы или кода конца кадра LF.

В результате следующие за буквой L цифры переписьшаются с помощью

10

978784

синхроим 1ул1- сов СИ в гоответстпу- юпше разряды счетчика 5, а триггер В устанавливается в единицу. Счетчик 5 обычно выполняется десятичным с числом разрядов два, так клк более 9 цикл1- в практически не встречается. В момент прихода следуютей за L буквы или кода 1Л триггер тапомлнання I в блоке 2 сбрасывается в ноль и на выходе элемента И 27 образуется перепад, из которого формирователь 22 формирует импульс, который, пройдя через элемент ИЛИ 24, вычтет из содержимого счетчика 5 единицу. С приходом команды ПВ блок 2 формирует на своем выходе потенциал, который присутствует на выходе блока 2 в течение ввода одного кадра. Этот потенциал открывает элементр И 13-16 и устанавливает в единицу триггер 7, в результате чего элемент И 18 нулевым выходом триггера 7 закрывается, что запрещает прохождение импульсов 25 СИ L на вход записи счетчика 5 и, следовательно, повторную запись в него числа циклов, пока триггер 7 находится в состоянии единицы. Так как элементы И 13-16 открыты потенциалом

15

20

30

И, то, пока он присутствует, величина X суммируется в сумматоре 9 с величиной, хранимой в регистре 11, так как ТИ X через элемент И 13 поступают на вход сдвига регистра II, а выход его мпадшего разряда через элемент И 14 подключен к второму входу сумматора 9.

Так как вь(ход сумматора 9 подключен к входу старшего разряда сдвигово- д го регистра 11 и входу интерполятора 3, то величина с .выхода сумматора 9 запишется в интерполятор и регистр II. Если в регистре 1I первоначально ноль, то при первом вводе величины X эта величина сложится с нулем и заиесется в интерполятор и в регистр 11.

Аналогично в силу полной симметрии схемы работают элементы И 15 и 16, сумматор 10 и сдвиговый регистр 12.

Так, при первом вводе кадра № 2 в координату У интерполятора и в регистр 12 будет занесена величина 100. Поэтому при первой отработке кадра № 2 (фиг. 2) будет отработана величина . Но при отработке кадра N(n-H ) величина 100 из регистра 12 сложится с нулем и занесется в интер- попятор 3 и в регистр 12.

5

5

10

Поэтому при первой отработке кадра N(n+l) будет отработана величина .

При вводе кадра N(n+3) расшифровывается команда М20. Потенциал этой команды поступает на вход элемента И 20, на втором входе которого присутствует единичный потенциал с выхода триггера 8. В реэультате на выходе элемента И 20 является положительный потенциал, который поступает на вход элемента И 25 и формирователя 22, на его выходе появляется импульс, который, пройдя через элемент ИЛИ 24, 15 поступает на вычитающий вход счетчика 5 и вычитает единицу. С приходом с выхода блока 2 импульсп LF он сбрасывает в ноль триггер 6 и, пройдя

му перепада на его выходе не будет). После первой отработки участка коман да М20 вычитает единицу и в счетчике g 5 остается единица, после второй отработки - ноль. После третьей отработки счетчик 5 переполняется и сигналом переполнения сбрасывает триггер 8 в ноль. В результате с приходом импульса LF он не проходит череэ элемент И 25, так как этот элемент закрыт нулевым сигналом с выхода эле мента И 20, на входе которого нуль с выхода триггера 8. В результате код ячейки ОЗУ, где хранится буква L, пе реписан в счетчик 4 не будет и вводи ся кадр N(n+4) и т.д. В кадре N(n+4 помимо любой другой информации необходимо задавать команду G80, коточерез элемент И 25, поступает на вход 20 рая, пройдя через формирователь 21,

параллельной записи счетчика 4, при этом код ячейки ОЗУ1, в которой хранится буква L, из регистра 23 переписывается в счетчик 4. В результате по сигналу Пуск ввода вновь будет вводиться информация кадра ff 1, начиная с символа L. I

Но на этот раз в кадре № 2 будет

отработана величина , т.е. 100 иэ накопительного регистра 12 и 100 из информации кадра, причем величина 200 занесется в регистр 12, поэтому в кадре N{n+l) будет отработана величина и код 200 сохранится в ре- гистре 12. Поэтому деталь будет отрабатываться с параллельным смещением образующей на I00 импульсов по координате У, как это показано на фиг.2.

Кадрами № 3 - N может быть задана любая программа, в том числе

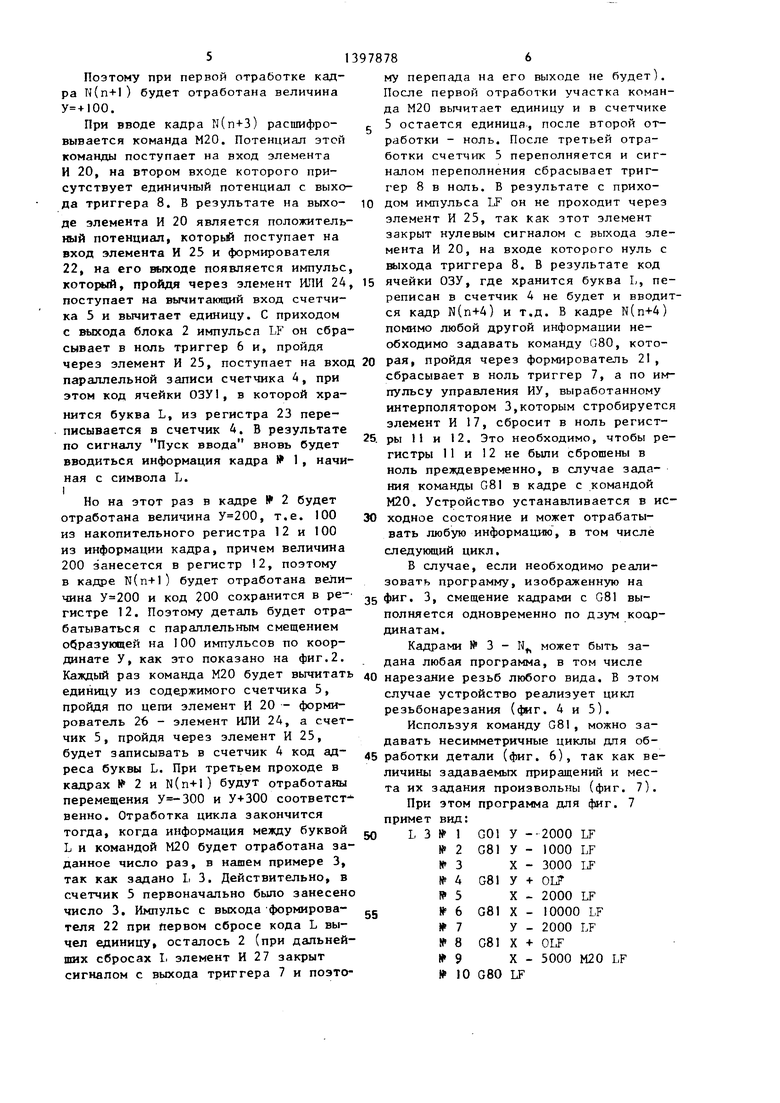

Каждый раз команда М20 будет вычитать 40 нарезание резьб любого вида. В этом единицу из содержимого счетчика 5, случае устройство реализует цикл

и

пройдя по цепи элемент И 20 - формирователь 26 - элемент ИЛИ 24, а счетчик 5, пройдя через элемент И 25, будет записывать в счетчик 4 код адреса буквы L. При третьем проходе в кадрах № 2 и N(n+l) будут отработаны перемещения и У+300 соответст- венно. Отработка цикла закончится тогда, когда информация между буквой L и командой М20 будет отработана заданное число раз, в нашем примере 3, так как задано L 3. Действительно, в счетчик 5 первоначально было занесено число 3. Импульс с выхода формирователя 22 при первом сбросе кода L вычел единицу, осталось 2 (при дальнейших сбросах I, элемент И 27 закрыт сигналом с выхода триггера 7 и поэторезьбонарезания (фиг. 4 и 5).

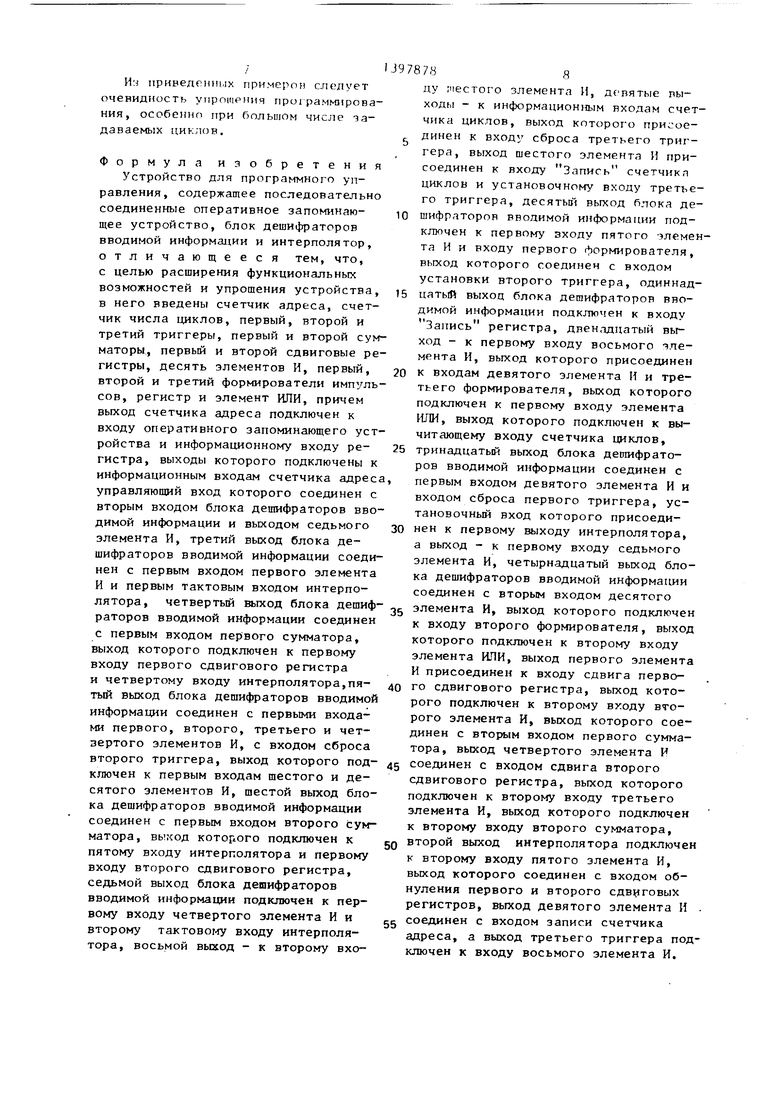

Используя команду G81, можно задавать несимметричные циклы для об- 45 работки детали (фиг. 6), так как величины задаваемых приращений и места их задания произвольны (фиг. 7).

При этом программа для фиг. 7 примет вид: 50

55

10 G80 LF

му перепада на его выходе не будет). После первой отработки участка команда М20 вычитает единицу и в счетчике 5 остается единица, после второй отработки - ноль. После третьей отработки счетчик 5 переполняется и сигналом переполнения сбрасывает триггер 8 в ноль. В результате с приходом импульса LF он не проходит череэ элемент И 25, так как этот элемент закрыт нулевым сигналом с выхода элемента И 20, на входе которого нуль с выхода триггера 8. В результате код ячейки ОЗУ, где хранится буква L, переписан в счетчик 4 не будет и вводится кадр N(n+4) и т.д. В кадре N(n+4) помимо любой другой информации необходимо задавать команду G80, котосбрасывает в ноль триггер 7, а по импульсу управления ИУ, выработанному интерполятором 3,которым стробируется элемент И 17, сбросит в ноль регист25. ры 11 и 12. Это необходимо, чтобы регистры 11 и 12 не были сброшены в ноль преждевременно, в случае задания команды G81 в кадре с командой М20. Устройство устанавливается в ис30 ходное состояние и может отрабатывать любую информацию, в том числе

следующий цикл,

В случае, если необходимо реализовать программу, изображенную на 35 фиг. 3, смещение кадрами с G81 выполняется одновременно по дзум коар- динатам.

Кадрами № 3 - N может быть задана любая программа, в том числе

40 нарезание резьб любого вида. В этом случае устройство реализует цикл

и

резьбонарезания (фиг. 4 и 5).

Используя команду G81, можно задавать несимметричные циклы для об- 45 работки детали (фиг. 6), так как величины задаваемых приращений и места их задания произвольны (фиг. 7).

При этом программа для фиг. 7 примет вид: 50

10 G80 LF

Иа приведенных примеров следует очевидр{ость VTipomfnnH программирования, особенно гтри большом числе задаваемых циклов.

Формула изобретения

Устройство для программного управления, содержашее последовательно соединенные оперативное запоминаю- щее устройство, блок дешифраторов вводимой информации и интерполятор, отличающееся тем, что, с целью расширения функциональных возможностей и упрощения устройства, в него введены счетчик адреса, счетчик числа циклов, первый, второй и третий триггеры, первый и второй сумматоры, первый и второй сдвиговые регистры, десять элементов И, первый, второй и третий формирователи импульсов, регистр и элемент ИЛИ, причем выход счетчика адреса подключен к входу оперативного запоминающего устройства и информационному входу ре- гистра, выходы которого подключены к информационным входам счетчика адрес управляющий вход которого соединен с вторым входом блока дешифраторов вводимой информации и выходом седьмого элемента И, третий выход блока дешифраторов вводимой информации соединен с первьтм входом первого элемента И и первым тактовым входом интерполятора, четвертый выход блока дешиф раторов вводимой информации соединен с первым входом первого сумматора, выход которого подключен к первому входу первого сдвигового регистра и четвертому входу интерполятора,пя- тый выход блока дешифраторов вводимой информации соединен с первыми входами первого, второго, третьего и четвертого элементов И, с входом сброса второго триггера, выход которого под- ключей к первым входам шестого и десятого элементов И, шестой выход блока дешифраторов вводимой информации соединен с первым входом второго сумматора, выход котог ого подключен к пятому входу интерполятора и первому входу второго сдвигового регистра, седьмой выход блока дешифраторов вводимой информации подключен к первому входу четвертого элемента И и второму тактовог у входу интерполятора, восьмой выход - к второму входу ;пестого элемента И, девятые пы- ходы - к информационным входам счетчика циклов, выход которого присоединен к входу сброса третьего трнг- гера, выход шестого элемента Н присоединен к входу Запись счетчикп циклов и установочному входу третьего триггера, десятый выход блока дешифраторов вводимой информации подключен к первому входу пятого элемента И и входу первого формирователя, выход которого соединен с входом установки второго триггера, одиннад- цать1й выход блока дешифраторов вводимой информации подключен к входу Запись регистра, двенадцатый выход - к первому входу восьмого элемента И, выход которого присоединен к входам девятого элемента И и третьего формирователя, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к вычитающему входу счетчика циклов, тринадцатый выход блока деошфрато- ров вводимой информации соединен с первым входом девятого элемента И и входом сброса первого триггера, установочный вход которого присоединен к первому выходу интерполятора, а выход - к первому входу седьмого элемента И, четырнадцатый выход блока дешифраторов вводимой информации соединен с вторым входом десятого элемента И, выход которого подключен к входу второго формирователя, выход которого подключен к второму входу элемента Ш1И, выход первого элемента И присоединен к входу сдвига первого сдвигового регистра, выход которого подключен к второму входу второго элемента И, выход которого соединен с вторым входом первого сумматора, выход четвертого элемента И соединен с входом сдвига второго сдвигового регистра, выход которого подключен к второму входу третьего элемента И, выход которого подключен к второму входу второго сумматора, второй выход интерполятора подключе к второму входу пятого элемента И, вькод которого соединен с входом обнуления первого и второго сдвиговых регистров, выход девятого элемента И соединен с входом записи счетчика адреса, а выход третьего триггера подключен к входу восьмого элемента И.

N(ftt2}

NfrtMJ

n

1397878

)

N2

Фиг. 6

Фиг. 5

ftS

V7

/v

Л /

. V5

e. 7

Авторы

Даты

1988-05-23—Публикация

1986-06-03—Подача