Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками.

Целью изобретения является упрощение программирования, уменьшение объема запоминающего.устройства и расширение функциональных возможностей устройства программного управления.

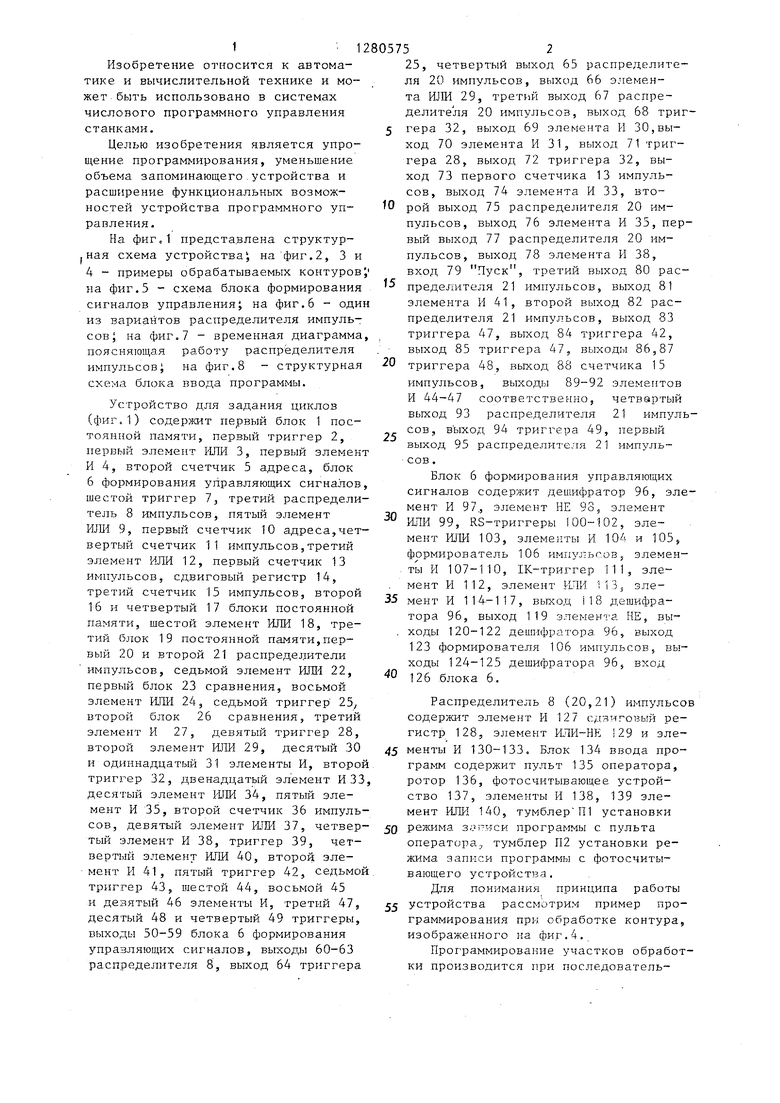

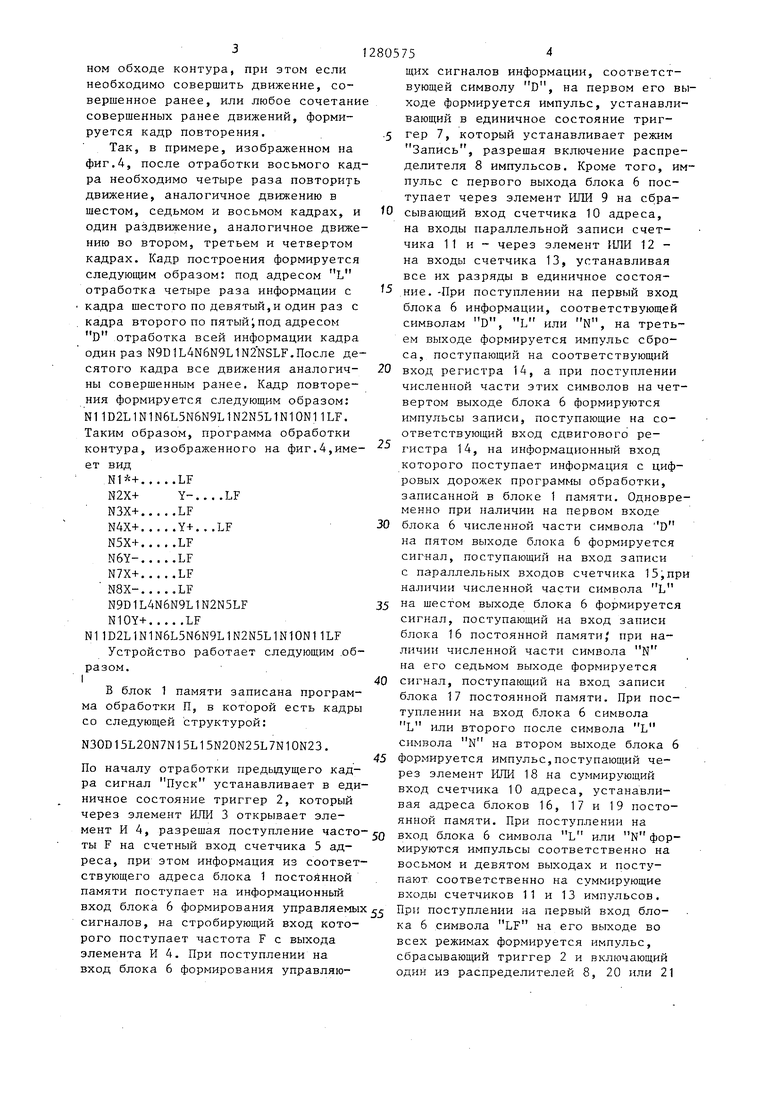

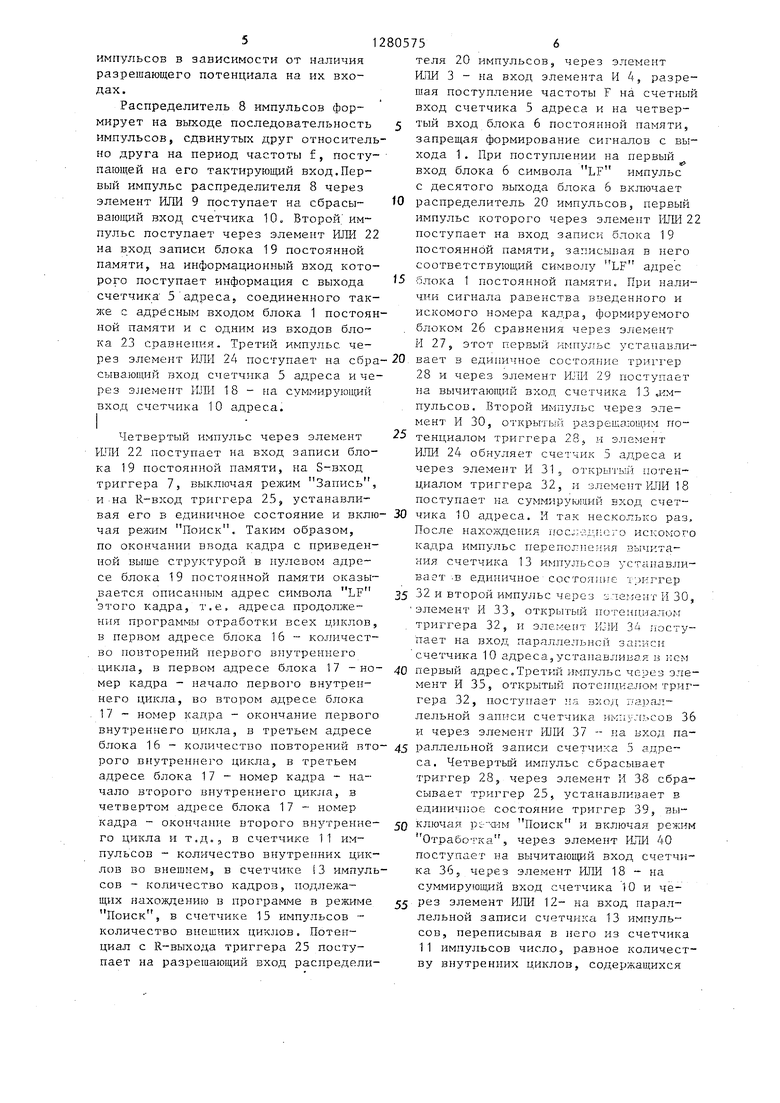

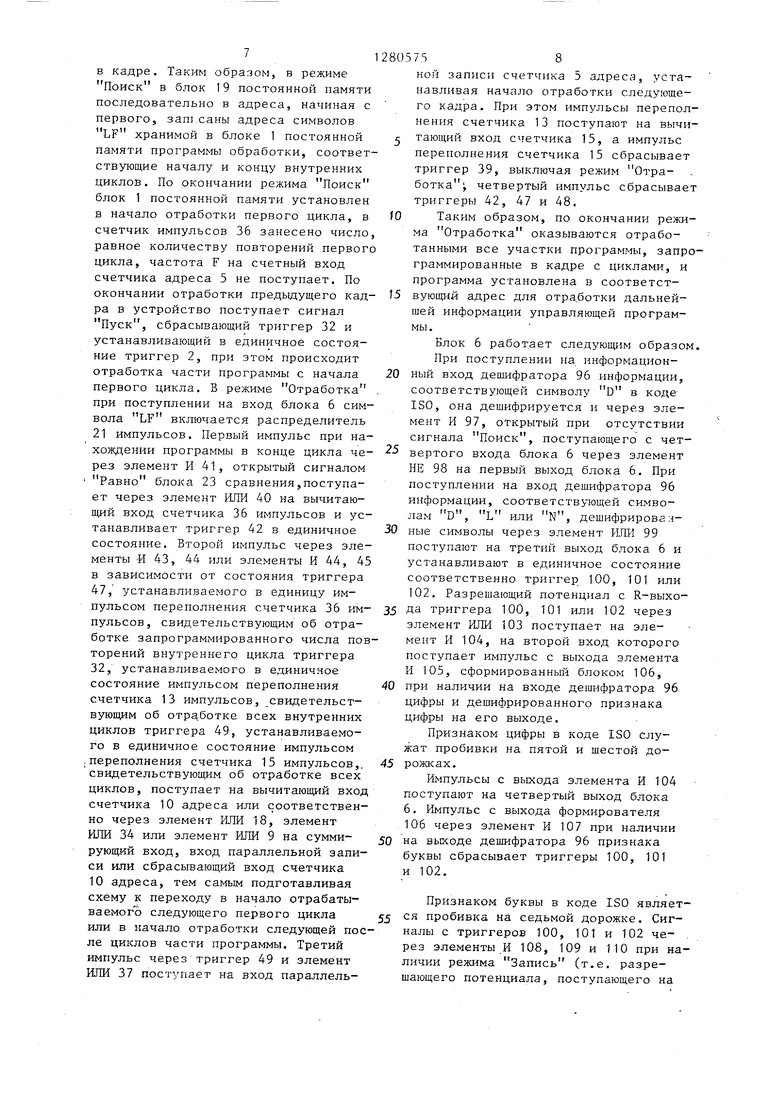

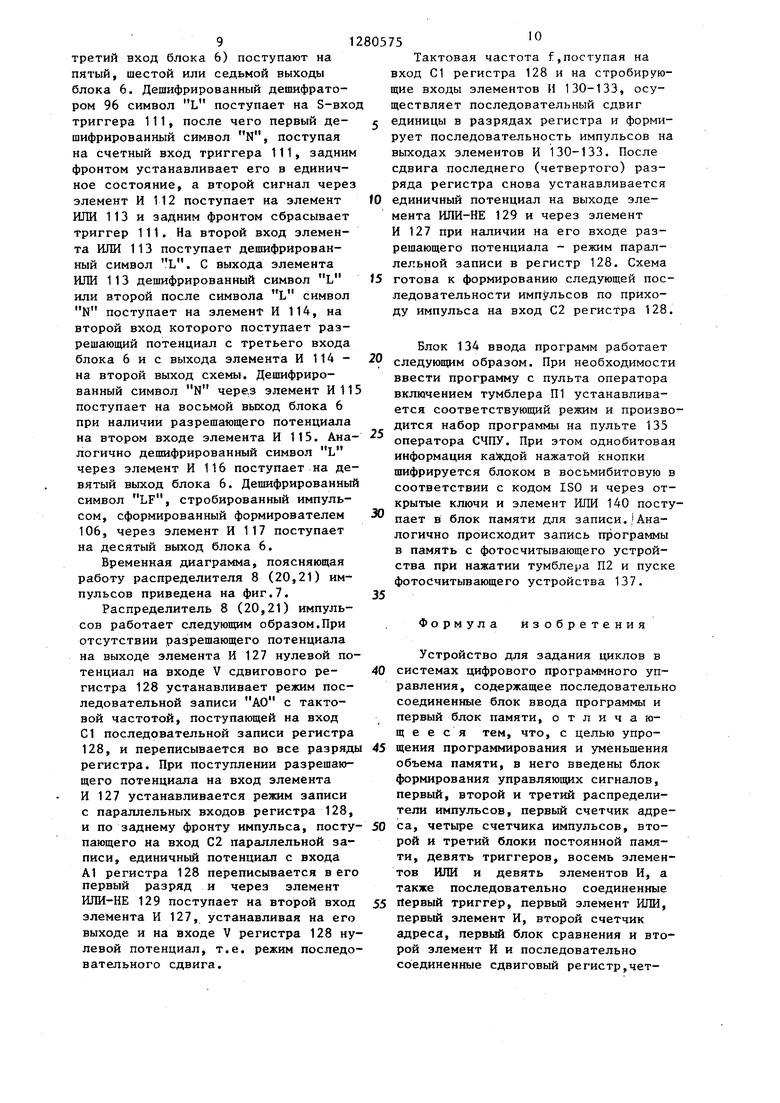

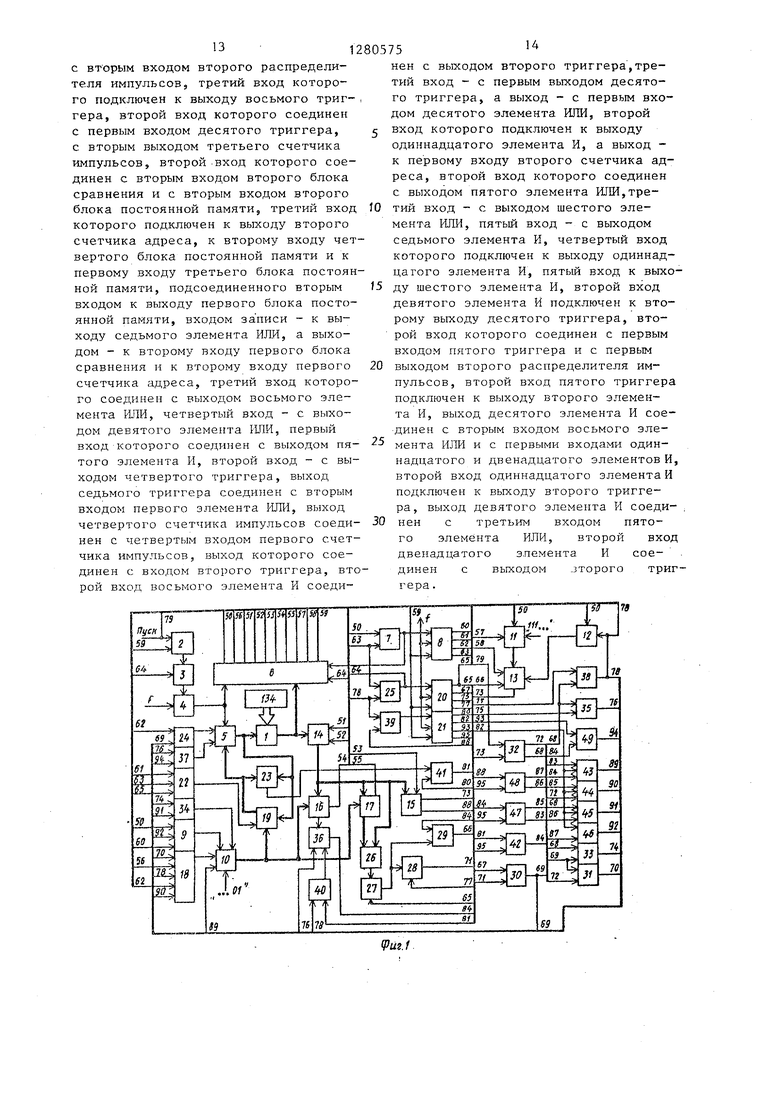

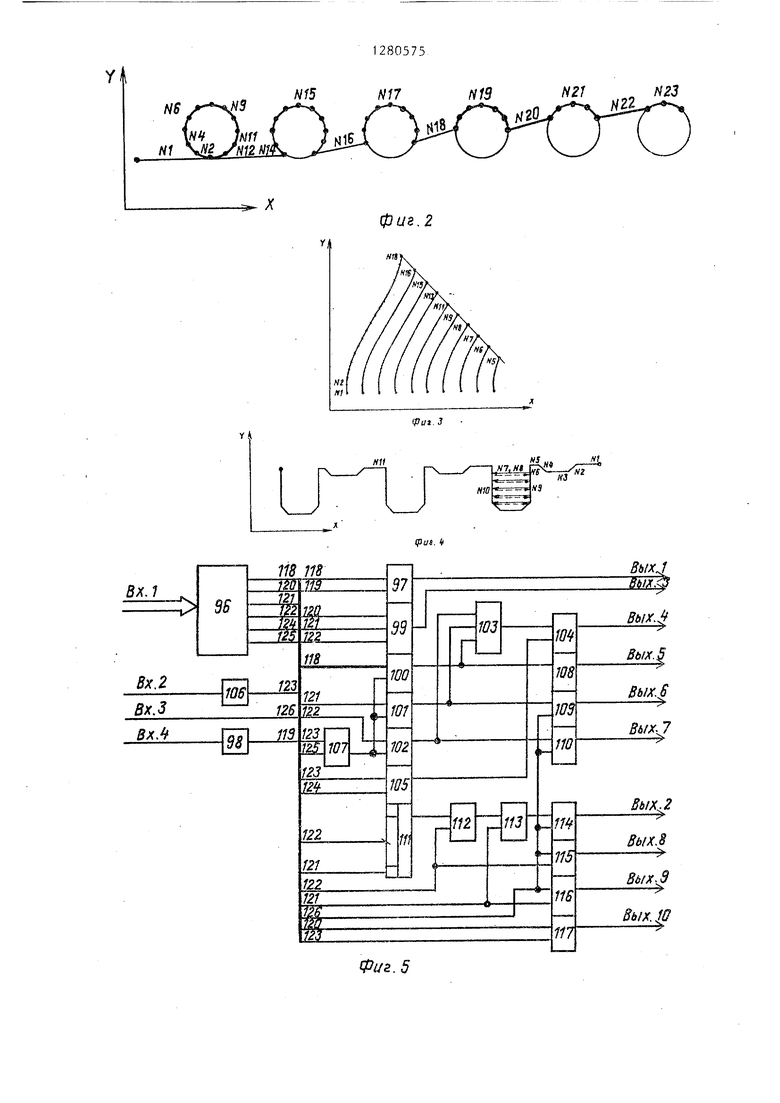

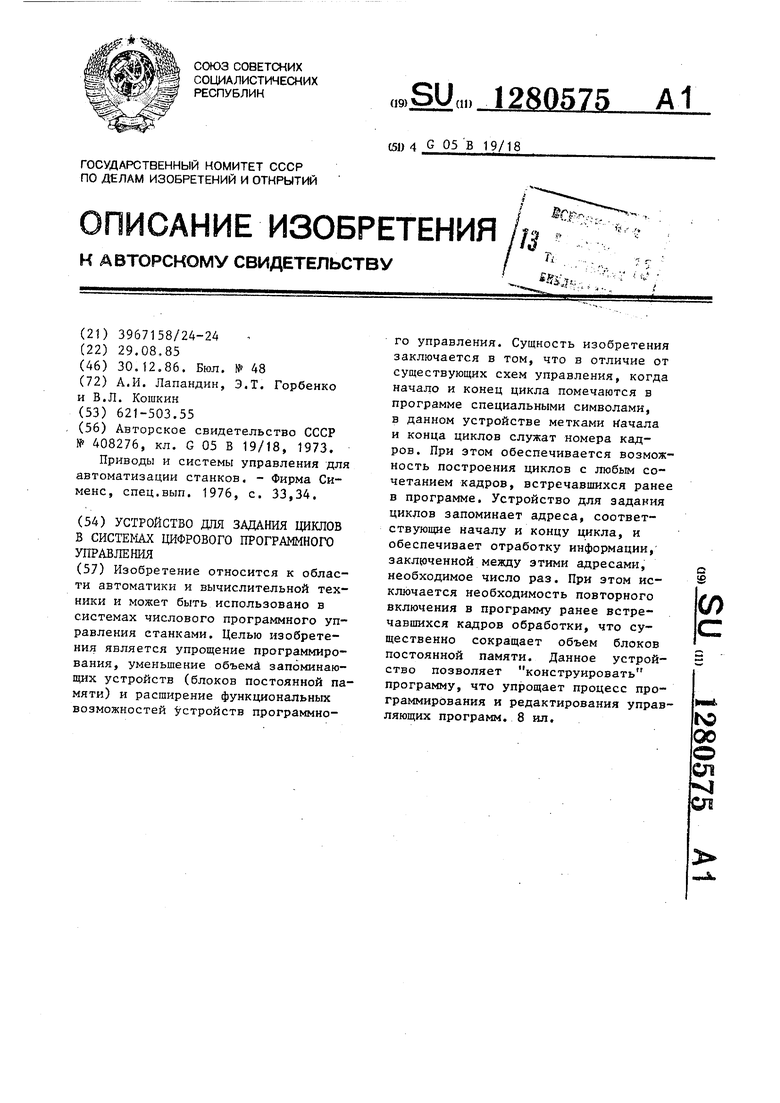

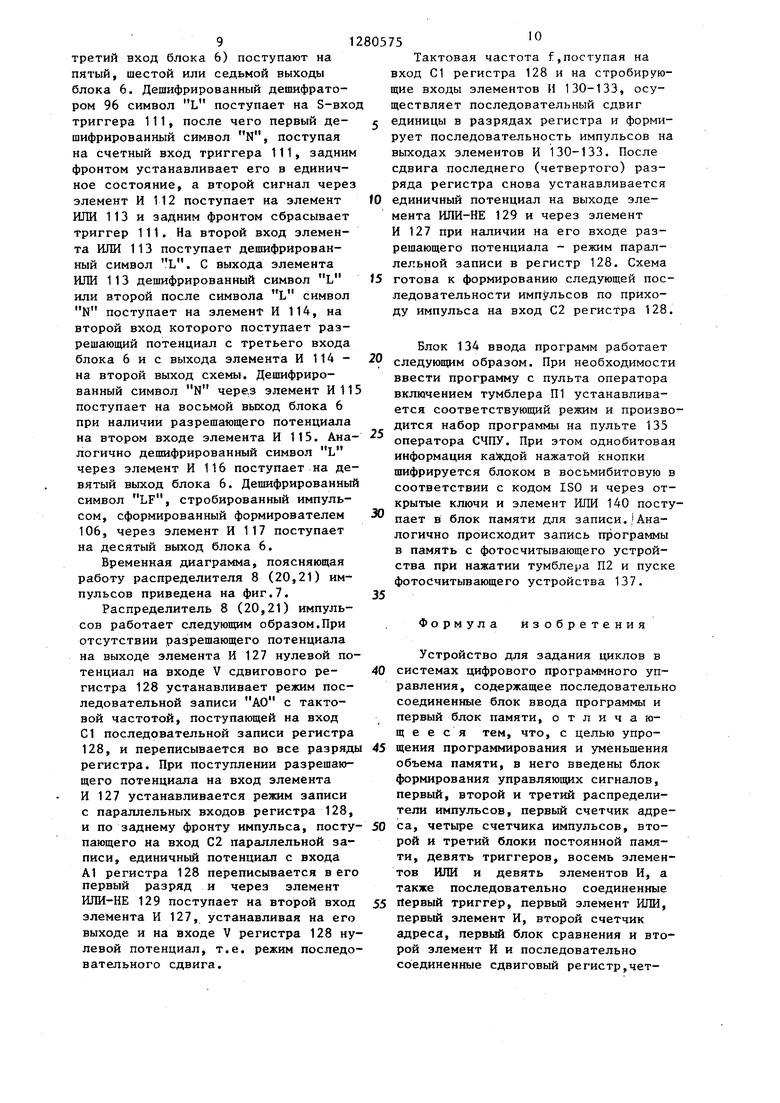

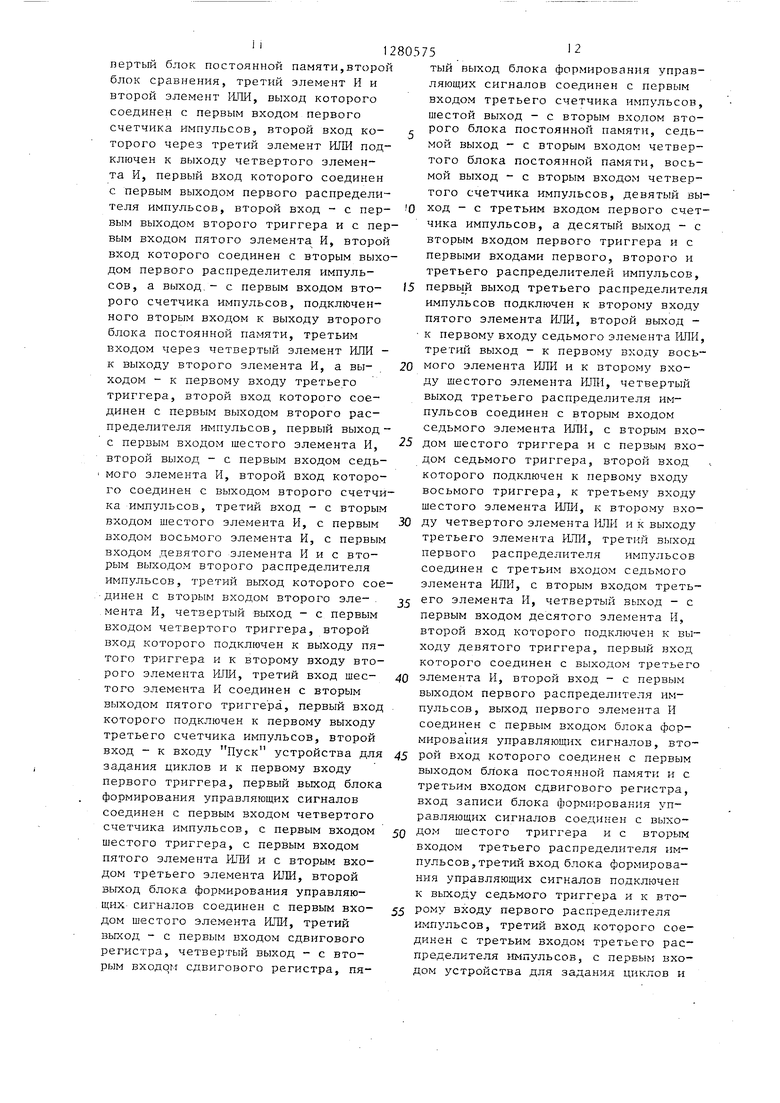

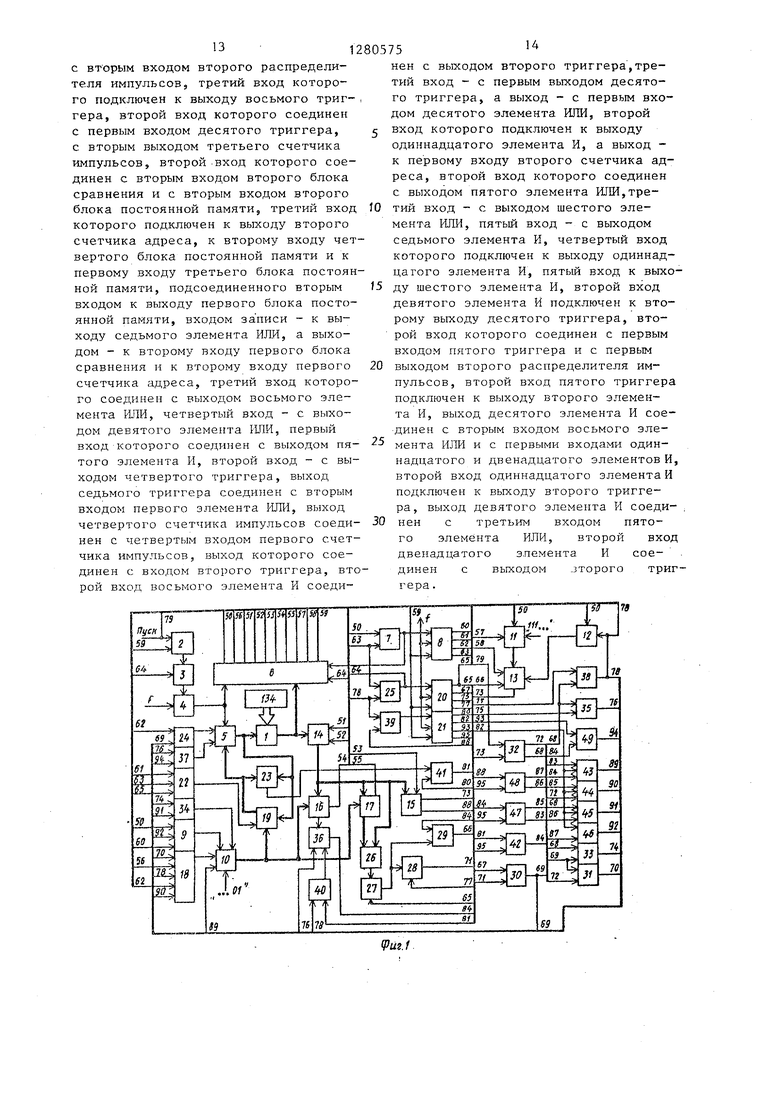

На фиг,1 представлена структур- I нал схема устройства на фиг.2, 3 и 4 - примеры обрабатываемых контуров на фиг.5 - схема блока формирования сигналов управленияJ на фиг.6 - один из вариантов распределителя импульсов; на фиг.7 - временная диаграмма поясняющая работу распределителя импульсов; на фиг.8 - структурная схема блока ввода программы.

Устройство для задания циклов (фиг.1) содержит первый блок 1 постоянной памяти, первый триггер 2, первый элемент ИЛИ 3, первый элемент И 4, второй счетчик 5 адреса, блок 6 формирования управляющих сигналов шестой триггер 1, третий распределитель 8 импульсов, пятый элемент ИJBi 9, первый счетчик 10 адреса,четвертый счетчик 11 импульсов,третий элемент ИЛИ 12, первый счетчик 13 импульсов, сдвиговый регистр 14, третий счетчик 15 импульсов, второй 16 и четвертый 17 блоки постоянной памяти, шестой элемент ИЛИ 18, третий блок 19 постоянной памяти,первый 20 и второй 21 распределители импульсов, седьмой элемент ШП 22, первый блок 23 сравнения, восьмой элемент ИЛИ 24, седьмой триггер 25 второй блок 26 сравнения, третий элемент И 27, девятый триггер 28, второй элемент ИЛИ 29, десятый 30 и одиннадцатый 31 элементы И, второй триггер 32, двенадцатый элемент И 33 десятый элемент ШШ 34, пятый элемент И 35, второй счетчик 36 импульсов, девятый элемент ИЛИ 37, четвертый элемент И 38, триггер 39, четвертый элемент ИЛИ 40, второй элемент И 41, пятый триггер 42, седьмой триггер 43, шестой 44, восьмой 45 и девятый 46 элементы И, третий 47, десятый 48 и четвертый 49 триггеры, выходы 50-59 блока 6 формирования управляющих сигналов, выходы 60-63 распределителя 8, выход 64 триггера

25, четвертый выход 65 распределителя 20 импульсов, выход 66 элемента ШЖ 29, третий выход 67 распределителя 20 импульсов, выход 68 триггера 32, выход 69 элемента И 30,выход 70 элемента И 31, выход 71 триггера 28, выход 72 триггера 32, выход 73 первого счетчика 13 импульсов, выход 74 элемента И 33, второй выход 75 распределителя 20 импульсов, выход 76 элемента И 35, первый выход 77 распределителя 20 импульсов, выход 78 элемента И 38, вход 79 Пуск, третий выход 80 распределителя 21 импульсов, выход 81 элемента И 41, второй выход 82 распределителя 21 импульсов, выход 83 триггера 47, выход 84 триггера 42, выход 85 триггера 47, выходы 86,87

триггера 48, выход 88 счетчика 15 импульсов, выходы 89-92 элементов И 44-47 соответственно, четвертый выход 93 распределителя 21 импульсов, выход 94 триггера 49, первый выход 95 распределителя 21 импульсов .

Блок 6 формирования управляющих сигналов содержит дешифратор 96, элемент И 97., элемент НЕ 98, элемент ИЛИ 99, RS-триггеры 100-102, элемент ИЛИ 103, элементы И 10Л и 105, формирователь 106 импульсов, элементы И 107-Г10, 1К-триггер 111, элемент И 112, элемент ИЛИ ИЗ,, элемент И 114--117, выход 118 дешифратора 96, выход 119 элемен1 а НЕ, вы- ходы 120-122 дешифратора 96, выход 123 формирователя 106 импульсов, выходы 124-125 дешифратора 96, вход

126 блока 6.

Распределитель 8 (20,21) импульсов содержит элемент И 127 сд: иговый регистр 128, элемент ИЛИ-Н 129 и элементы И 130-133. Блок 134 ввода программ содержит пульт 135 оператора, ротор 136, фотосчитывающее устройство 137, элементы И 138, 139 элемент ИЛИ 140, тумблер П1 установки

режима з;.1писи программы с пульта оператора, тумблер 112 установки режима записи программы с фотосчиты- вающего устройства.

Для понимания принципа работы

устройства рассмотрим пример программирования при обработке контура, изображенного на фиг.А.

Программирование участков обработки производится при последователь

ном обходе контура, при этом если необходимо совершить движение, совершенное ранее, или любое сочетани совершенных ранее движений, формируется кадр повторения.

Так, в примере, изображенном на фиг.4, после отработки восьмого кадра необходимо четыре раза повторить движение, аналогичное движению в шестом, седьмом и восьмом кадрах, и один раздвижение, аналогичное движению во втором, третьем и четвертом кадрах. Кадр построения формируется

следующим образом: под адресом L отработка четыре раза информации с кадра шестого по девятый,и один раз с кадра второго по пятый; под адресом D отработка всей информации кадра один раз N9D1L4N6N9L1N2 NSLF.После десятого кадра все движения аналогичны совершенным ранее. Кадр повторения формируется следуюш;им образом: N11D2L1N1N6L5N6N9L1N2N5L1N10N11LF. Таким образом, программа обработки контура, изображенного на фиг.4,имеет вид

N2X+ Y-LF

N3X+LF

N4X+Y+...LF

N5X+LF

N6Y-LF

N7X+LF

N8X-LF

N9D1L4N6N9L1N2N5LF

N10Y-(-LF

N11D2L1N1N6L5N6N9L1N2N5L1N10N11LF

Устройство работает следуюшим .образом. I

В блок 1 памяти записана программа обработки П, в которой есть кадры со следующей структурой:

N30D15L20N7N15L15N20N25L7N10N23.

По началу отработки предьщущего кадра сигнал Пуск устанавливает в единичное состояние триггер 2, который через элемент ИЛИ 3 открывает элемент И 4, разрешая поступление часто ты F на счетный вход счетчика 5 адреса, при этом информация из соответствующего адреса блока 1 постоянной памяти поступает на информационный

вход блока 6 формирования управляемых При поступлении на первый вход блосигналов, на стробирующий вход которого поступает частота F с выхода элемента И 4. При поступлении на вход блока 6 формирования управляюка 6 символа LF на его выходе во всех режимах формируется импульс, сбрасывающий триггер 2 и включающий один из распределителей 8, 20 или 21

ш;их сигналов информации, соответст- D

0

0

вующеи символу U , на первом его выходе формируется импульс, устанавливающий в единичное состояние триггер 7, который устанавливает режим Запись, разрешая включение распределителя 8 импульсов. Кроме того, импульс с первого выхода блока 6 поступает через элемент РШИ 9 на сбрасывающий вход счетчика 10 адреса, на входы параллельной записи счетчика 11 и - через элемент МЛИ 12 - на входы счетчика 13, устанавливая все их разряды в единичное состоя5 ние. -При поступлении на первый вход блока 6 информации, соответствующей символам D, L или N, на третьем выходе формируется импульс сброса, поступающий на соответствующий вход регистра 14, а при поступлении численной части этих символов на четвертом выходе блока 6 формируются импульсы записи, поступающие на соответствующий вход сдвигового ре5 ристра 14, на информационный вход которого поступает информация с цифровых дорожек программы обработки, записанной в блоке 1 памяти. Одновременно при наличии на первом входе

0 блока 6 численной части символа D на пятом выходе блока 6 формируется сигнал, поступающий на вход записи с параллельных входов счетчика 15,при наличии численной части символа L

5 на шестом выходе блока 6 формируется сигнал, поступающий на вход записи блока 16 постоянной памяти при наличии численной части символа N на его седьмом выходе формируется

0 сигнал, поступающий на вход записи блока 17 постоянной памяти. При поступлении на вход блока 6 символа L или второго после символа L символа N на втором выходе блока 6

5 формируется импульс,поступающий через элемент ИЛИ 18 на суммирующий вход счетчика 10 адреса, устанавливая адреса блоков 16, 17 и 19 постоянной памяти. При поступлении на вход блока 6 символа L или N формируются импульсы соответственно на восьмом и девятом выходах и поступают соответственно на суммирующие входы счетчиков 11 и 13 импульсов.

При поступлении на первый вход блока 6 символа LF на его выходе во всех режимах формируется импульс, сбрасывающий триггер 2 и включающий один из распределителей 8, 20 или 21

импульсов в зависимости от наличия разрешающего потенциала на их входах.

Распределитель 8 импульсов формирует на выходе последовательность импульсов, сдвинутых друг относительно друга на период частоты f, поступающей на его тактирующий вход.Первый импульс распределителя 8 через элемент ИЛИ 9 поступает на сбрасы- ваюцщй вход счетчика 10. Второй импульс поступает через элемент ИЛИ 22 на вход записи блока 19 постоянной памяти, на информационный вход которого поступает информация с выхода счетчика 5 адреса, соединенного также с адресным входом блока 1 постоянной памяти и с одним из входов бло15 блока 1 постоянной памяти. При наличии сигнала равенства введенного и искомого номера кадра, формируемого блоком 26 сравнения через элемент И 27, этот первый импульс устапавлика 23 сравнения. Третий импульс через элемент ИЛИ 24 поступает на сбра- 20вает в единичное состояние триггер сывающий вход счетчика 5 адреса и че-28 и через элемент ИЛИ 29 поступает рез элеметгг ИЛИ 18 - на суммирующийна вычитающий вход счетчика 13,кмвход счетчика 10 адреса.

Четвертый импульс через элемент ШШ 22 поступает на вход записи блока 19 постоянной памяти, на S-вход триггера 7, выключая режим Запись, и на R-вход триггера 25, устанавливая его в единичное состояние и 30 чика 10 адреса. И так несколько раз.

чая реядам Поиск. Таким образом, по окончании ввода кадра с приведенной выше структурой в нулевом адресе блока 19 постоянной памяти оказывается описанным адрес символа LF этого кадра, т.е. адреса продолжения программы отработки всех циклов, в первом адресе блока 16 - количество повторений первого внутреннего

После нахолодепия nocj;e;.-,iicro искомого кадра импульс переполг1еиия вь чита- ния счетчика 13 импульсов устанавливает -в единичное состояние ivjiirrep 35 32 и второй импульс через ;;лемент И 30, элемент И 33, открытый потенциалом . триггера 32, и элемент ЮИ 34 поступает на вход параллельной записи

счетчика 10 адреса,устанавливая в нем цикла, в первом адресе блока 17 -но- 40 первый адрес .Третий импульс через эле- мер кадра - начало первого внутрен- мент И 35, открытый поте1п калом триггера 32, поступает на вхо.п; г/арал- лельной зап1-5си счетчика HM:iv:(bCOB 36 и через элемент ИЛИ 37 - на вход панего цикла, во втором адресе олока 17 - номер кадра - окончание первого внутреннего цикла, в третьем адресе

блока 16 - количество повторений вто- 45 раллельной записи счетчика 5 адрерого внутреннего цикла, в третьем адресе блока 17 номер кадра - начало второго внутреннего цикла, в четвертом адресе блока 17 - номер

кадра - окончание второго внутренне- 50 ключая Поиск и включая режим го цикла и т.д., в счетчике 11 им- Отработка, через элемент Р-ШИ 40 пульсов - количество внутренних цик- поступает на вычитающий вход счетчг-;- лов во внешнем, в счетчике 13 импуль- ка 36, через элемент ИЛИ 18 - на сов количество кадров, подлежащих нахождению в программе в режиме Поиск, в счет-чике 15 импульсов суммирующий вход счетчика 10 и че- 55 рез элемент ИЛИ 12- на вход параллельной записи счетчика 13 импульсов, переписывая в него из счетчика 11 импульсов число, равное количеству внутренних циклов, содержащихся

количество внешних циклов. Потенциал с R-выхода триггера 25 поступает на разрешающий вход распределителя 20 импульсов, через элемент ИЛИ 3 - на вход элемента И 4, разрешая поступление частоты F на счетный вход счетчика 5 адреса и на четвертый вход блока 6 постоянной памяти, запрещая формирование сигналов с выхода 1. При поступлении на первый вход блока 6 символа LF импульс с десятого выхода блока 6 включает

распределитель 20 импульсов, первый импульс которого через элемент 1-ШИ 22 поступает на вход записи блока 19 постоянной памяти, записывая в него соответствующий символу LF адрес

блока 1 постоянной памяти. При наличии сигнала равенства введенного и искомого номера кадра, формируемого блоком 26 сравнения через элемент И 27, этот первый импульс устапавливает в единичное состояние триггер 28 и через элемент ИЛИ 29 поступает на вычитающий вход счетчика 13,кмпульсов. Второй импульс через элемент И 30, открытый разрешающим гго- тенциалом триггера 28, и элемент ИЛИ 24 обнуляет счетчик 5 адреса и через элемент И 31 , открьп ый потенциалом триггера 32, и элемент ИЛИ 18 поступает на. суммирующий вход счетПосле нахолодепия nocj;e;.-,iicro искомого кадра импульс переполг1еиия вь чита- ния счетчика 13 импульсов устанавливает -в единичное состояние ivjiirrep 35 32 и второй импульс через ;;лемент И 30, элемент И 33, открытый потенциалом . триггера 32, и элемент ЮИ 34 поступает на вход параллельной записи

са. Четвертый импульс сбрасывает триггер 28, через элемент И 38 сбрасывает триггер 25, устанавливает в единичное состояние триггер 39, вы50 ключая Поиск и включая режим Отработка, через элемент Р-ШИ 40 поступает на вычитающий вход счетчг-;- ка 36, через элемент ИЛИ 18 - на

суммирующий вход счетчика 10 и че- 55 рез элемент ИЛИ 12- на вход параллельной записи счетчика 13 импульсов, переписывая в него из счетчика 11 импульсов число, равное количеству внутренних циклов, содержащихся

7

в кадре. Таким образом, в режиме Поиск в блок 19 постоянной памяти последовательно в адреса, начиная с первого, зап1-саны адреса символов LF хранимой в блоке 1 постоянной памяти программы обработки, соответствующие началу и концу внутренних циклов. По окончании режима Поиск блок 1 постоянной памяти установлен в начало отработки первого цикла, в счетчик импульсов 36 занесено число равное количеству повторений первого цикла, частота F на счетный вход счетчика адреса 5 не поступает. По окончании отработки предыдущего кадра в устройство поступает сигнал Пуск, сбрасывающий триггер 32 и устанавливающий в единичное состояние триггер 2, при этом происходит отработка части программы с начала первого цикла. В режиме Отработка при поступлении на вход блока 6 символа LF включается распределитель 21 импульсов. Первый импульс при нахождении программы в конце цикла через элемент И 41, открытый сигналом Равно блока 23 сравнения,поступает через элемент ИЛИ 40 на вычитающий в.ход счетчика 36 импульсов и устанавливает триггер 42 в единичное состояние. Второй импульс через элементы -И 43, 44 или элементы И 44, 45 в зависимости от состояния триггера 47, устанавливаемого в единицу импульсом переполнения счетчика 36 импульсов, свидетельствующим об отработке запрограммированного числа повторений внутреннего цикла триггера 32, устанавливаемого в единичное состояние импульсом переполнения счетчика 13 импульсов, свидетельствующим об отра.ботке всех внутренних циклов триггера 49, устанавливаемого в единичное состояние импульсом .переполнения счетчика 15 импульсов,, свидетельствующим об отработке всех циклов, поступает на вычитающий вход счетчика 10 адреса или соответственно через элемент ИЛИ 18, элемент ИЛИ 34 или элемент ИЛИ 9 на суммирующий вход, вход параллельной записи или сбрасывающий вход счетчика 10 адреса, тем самым подготавливая схему к переходу в начало отрабаты- ваемогЬ следующего первого цикла или в начало отработки следующей после циклов части программы. Третий импульс через триггер 49 и элемент ИЛИ 37 поступает на вход параллель805738

ной записи счетчика 5 адреса, устанавливая начало отработки следующего кадра. При этом импульсы переполнения счетчика 13 поступают на вычи- тающий вход счетчика 15, а импульс переполнения счетчика 15 сбрасывает триггер 39, выключая режим Отработка четвертый импульс сбрасывает триггеры 42, 47 и 48.

Ю Таким образом, по окончании режима Отработка оказываются отработанными все участки программы, запрограммированные в кадре с циклами, и программа установлена в соответст15 вующий адрес для отра.ботки дальнейшей информации управляющей программы .

Блок 6 работает следующим образом. При поступлении на информацион20 ный вход депшфратора 96 информации, соответствующей символу D в коде ISO, она дешифрируется и через элемент И 97, открытый при отсутствии сигнала Поиск, поступающего с вертого входа блока 6 через элемент ПЕ 98 на первый выход блока 6. При поступлении на вход дешифратора 96 информации, соответствующей символам D, L или N, дешифрирова: 30 ные символы через элемент I fflM 99 поступают на третий выход блока 6 и устанавливают в единичное состояние соответственно триггер 100, 101 или 102. Разрешающий потенциал с R-выхо35 да триггера 100, 101 или 102 через элемент ИЛИ 103 поступает на элемент И 104, на второй вход которого поступает импульс с выхода элемента И 105, сформированный блоком 106,

40 при наличии на входе дешифратора 96 цифры и дешифрированного признака цифры на его выходе.

Признаком цифры в коде ISO служат пробивки на пятой и шестой до5 рожках.

Импульсы с выхода элемента И 104 поступают на четвертый выход блока 6. Импульс с выхода формирователя 106 через элемент И 107 при наличии

0 на выходе дешифратора 96 признака буквы сбрасывает триггеры 100, 101 и 102.

Признаком буквы в коде ISO являет- 5 ся пробивка на седьмой дорожке. Сигналы с триггеров 100, 101 и 102 через элементы И 108, 109 и 110 при наличии режима Запись (т.е. разрешающего потенциала, поступающего на

третий вход блока 6) поступают на пятый, шестой или седьмой выходы блока 6. Дешифрированный дешифратором 96 символ L поступает на S-вхо триггера 111, после чего первый дешифрированный символ N, поступая на счетный вход триггера 111, задним фронтом устанавливает его в единичное состояние, а второй сигнал через элемент И 112 поступает на элемент ИЛИ 113 и задним фронтом сбрасывает триггер 111, На второй вход элемента ИЛИ 113 поступает дешифрированный символ L. С выхода элемента ИЛИ 113 дешифрированный символ L или второй после символа L символ N поступает на элемент И 114, на второй вход которого поступает разрешающий потенциал с третьего входа блока бис выхода элемента И 114 - на второй выход схемы. Дешифрированный символ N через элемент И 115 поступает на восьмой выход блока 6 при наличии разрешающего потенциала на втором входе элемента И 115. Аналогично дешифрированный символ L через элемент И 116 поступает на девятый выход блока 6. Дешифрированный символ LF, стробированный импульсом, сформированный формирователем 106, через элемент И 117 поступает на десятый выход блока 6.

Временная диаграмма, поясняющая работу распределителя 8 (20,21) импульсов приведена на фиг.7.

Распределитель 8 (20,21) импульсов работает следующим обраэом.При отсутствии разрешающего потенциала на выходе элемента И 127 нулевой потенциал на входе V сдвигового регистра 128 устанавливает режим последовательной записи АО с тактовой частотой, поступающей на вход С1 последовательной записи регистра 128, и переписывается во все разряды регистра. При поступлении разрешающего потенциала на вход элемента И 127 устанавливается режим записи с параллельных входов регистра 128, и по заднему фронту импульса, поступающего на вход С2 параллельной записи, единичный потенциал с входа А1 регистра 128 переписывается в его первый разряд и через элемент ИЛИ-НЕ 129 поступает на второй вход элемента И 127, устанавливая на его выходе и на входе V регистра 128 нулевой потенциал, т.е. режим последовательного сдвига.

5

0

5

0

5

Тактовая частота f,поступая на вход С1 регистра 128 и на стробирую- щие входы элементов Н 130-133, осуществляет последовательный сдвиг единицы в разрядах регистра и формирует последовательность импульсов на выходах элементов И 130-133. После сдвига последнего (четвертого) разряда регистра снова устанавливается единичный потенциал на выходе элемента ИЛИ-НЕ 129 и через элемент И 127 при наличии на его входе разрешающего потенциала - режим параллельной записи в регистр 128. Схема готова к формированию следующей последовательности импульсов по приходу импульса на вход С2 регистра 128.

Блок 134 ввода программ работает следующим образом. При необходимости ввести программу с пульта оператора включением тумблера П1 устанавливается соответствующий режим и производится набор программы на пульте 135 оператора СЧПУ. При этом однобитовая информация каждой нажатой кнопки шифрируется блоком в восьмибитовую в соответствии с кодом ISO и через открытые ключи и элемент ИЛИ 140 поступает в блок памяти для записи.)Аналогично происходит запись программы в память с фотосчитывающего устройства при нажатии тумблера П2 и пуске фотосчитывающего устройства 137.

Формула изобретения

Устройство для задания циклов в

системах цифрового программного управления, содержащее последовательно соединенные блок ввода программы и первый блок памяти, отличающееся тем, что, с целью упрощения программирования и уменьшения объема памяти, в него введены блок формирования управляющих сигналов, первый, второй и третий распределители импульсов, первый счетчик адреса, четыре счетчика импульсов, второй и третий блоки постоянной памяти, девять триггеров, восемь элементов ИЛИ и девять элементов И, а также последовательно соединенные

первый триггер, первый элемент ИЛИ, первый элемент И, второй счетчик адреса, первый блок сравнения и второй элемент И и последовательно соединенные сдвиговый регистр,чет

пертьш блок постоянной памяти,второ блок сравнения, третий элемент И и второй элемент liJffl, выход которого соединен с первым входом первого счетчика импульсов, второй вход ко- торого через третий элемент ИЛИ подключен к выходу четвертого элемента И, первый вход которого соединен с первым выходом первого распределителя импульсов, второй вход - с пер вым выходом второго триггера и с певым входом пятого элемента И, второ вход которого соединен с вторым выхдом первого распределителя импульсов, а выход,- с первым входом вто- рого счетчика импульсов, подключенного вторым входом к выходу второго блока постоянной памяти, третьим входом через четвертый элемент ИЛИ к выходу второго элемента И, а вы- ходом - к первому входу третьего триггера, второй вход которого соединен с первым выходом второго распределителя импульсов, первый выход с первым входом шестого элемента И, второй выход - с первым входом седьмого элемента И, второй вход которого соединен с выходом второго счетчка импульсов, третий вход - с вторы входом шестого элемента И, с первым входом восьмого элемента И, с первы входом девятого элемента И и с вторым выходом второго распределителя импульсов, третий выход которого со

динен с вторым входом второго эле- . мента И, четвертый выход - с первым входом четвертого триггера, второй вход которого подключен к выходу пятого триггера и к второму входу второго элемента ИЛИ, третий вход шее- того элемента И соединен с вторым выходом пятого триггера, первый вход которого подключен к первому выходу третьего счетчика импульсов, второй вход - к входу Пуск устройства для задания циклов и к первому входу первого триггера, первый выход блока формирования управляющих сигналов соединен с первым входом четвертого счетчика импульсов, с первым входом шестого триггера, с первым входом пятого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, второй выход блока формирования управляющих сигналов соединен с первым вхо- дом шестого элемента ИЛИ, третий выход - с первым входом сдвигового регистра, четвертый выход - с вторым входом сдвигового регистра, пя2

О 5 0 0

5

0 5 0 5

тый выход блока формирования управляющих сигналов соединен с первым входом третьего счетчика импульсов, шестой выход - с вторым входом второго блока постоянной памяти, седьмой выход - с вторым входом четвертого блока постоянной памяти, восьмой выход - с вторым входом четвертого счетчика импульсов, девятый выход - с третьим входом первого счетчика импульсов, а десятый выход - с вторым входом первого триггера и с первыми входами первого, второго и третьего распределителей импульсов, первый выход третьего распределителя импульсов подключен к второму входу пятого элемента ИЛИ, второй выход - к первому входу седьмого элемента ИЛИ, третий выход - к первому входу восьмого элемента ИЛИ и к второму входу шестого элемента ИЛИ, четвертый выход третьего распределителя импульсов соединен с вторым входом седьмого элемента ИЛИ, с вторым входом шестого триггера и с первым входом седьмого триггера, второй вход которого подключен к первому входу восьмого триггера, к третьему входу шестого элемента ИЛИ, к второму входу четвертого элемента ИЛИ и к выходу третьего элемента РШИ, третий выход первого распределителя импульсов соединен с третьим входом седьмого элемента ИЛИ, с вторым входом третьего элемента И, четвертый выход - с первым входом десятого элемента И, второй вход которого подключен к выходу девятого триггера, первый вход которого соединен с выходом третьего элемента И, второй вход - с первым выходом первого распределителя импульсов, выход первого элемента И соединен с первым входом блока формирования управляющих сигналов, второй вход которого соединен с первым выходом бл:ока постоянной памяти и с третьим входом сдвигового регистра, вход записи блока формирован 1я управляющих сигналов соединен с выходом шестого триггера и с вторым входом третьего распределителя импульсов, третий вход блока формирования управляющих сигналов подключен к выходу седьмого триггера и к второму входу первого распределителя импульсов, третий вход которого соединен с третьим входом третьего распределителя импульсов, с первым входом устройства для задания циклов и

с вторым входом второго распределителя имлульсов, третий вход которого подключен к выходу восьмого триггера, второй вход которого соединен с первым входом десятого триггера, с вторым выходом третьего счетчика импульсов, второй ВХОД которого соединен с вторым входом второго блока сравнения и с вторым входом второго блока постоянной памяти, третий вход которого подключен к выходу второго счетчика адреса, к второму входу четвертого блока постоянной памяти и к первому входу третьего блока постоянной памяти, подсоединенного вторым входом к выходу первого блока постоянной памяти, входом за писи - к выходу седьмого элемента ИЛИ, а выходом - к второму входу первого блока сравнения и к второму входу первого счетчика адреса, третий вход которого соединен с выходом восьмого элемента ИЛИ, четвертый вход - с выходом девятого элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, второй вход - с выходом четвертого триггера, выход седьмого триггера соединен с вторым входом первого элемента ИЛИ, четвертого счетчика импульсов соединен с четвертым входом первого счетчика импульсов, выход которого соединен с входом второго триггера, второй вход восьмого элемента И соединен с выходом второго триггера,третий вход - с первым выходом десятого триггера, а выход - с первым входом десятого элемента ШТИ, второй

вход которого подключен к выходу одиннадцатого элемента И, а выход - к первому входу второго счетчика адреса, второй вход которого соединен с выходом пятого элемента ШШ,третий вход - с выходом шестого элемента ИЖ, пятый вход - с выходом седьмого элемента И, четвертый вход которого подключен к выходу одиннадцатого элемента И, пятый вход к выходу шестого элемента И, второй вход девятого элемента И подключен к второму выходу десятого триггера, второй вход которого соединен с первым входом пятого триггера и с первым

выходом второго распределителя импульсов, второй вход пятого триггера подключен к выходу второго элемента И, выход десятого элемента И соединен с вторым входом восьмого элемента ИЛИ и с первыми входами одиннадцатого и двенадцатого элементов И, второй вход одиннадцатого элемента И подключен к выходу второго триггера, выход девятого элемента И соединен с третьим входом пятого элемента ИЛИ, второй вход двенадцатого элемента И соединен с выходом jToporo триггера .

N15

N17

N21 nz3 N22

| название | год | авторы | номер документа |

|---|---|---|---|

| Система числового программного управления | 1986 |

|

SU1397879A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Устройство для контроля систем программного управления станком | 1988 |

|

SU1580320A1 |

| Устройство для программного управления | 1986 |

|

SU1397878A1 |

| Устройство для программного управления позиционного типа | 1983 |

|

SU1158976A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для программного управления | 1984 |

|

SU1255993A1 |

| Система программного управления | 1984 |

|

SU1200245A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах числового программного управления станками. Целью изобретения является упрощение программирования, уменьшение объемй запоминающих устройств (блоков постоянной памяти) и расширение функциональных возможностей устройств программного управления. Сущность изобретения заключается в том, что в отличие от существующих схем управления, когда начало и конец цикла помечаются в программе специальными символами, в данном устройстве метками Начала и конца циклов служат номера кадров. При этом обеспечивается возможность построения циклов с любым сочетанием кадров, встречавшихся ранее в программе. Устройство для задания циклов запоминает адреса, соответствующие началу и концу цикла, и обеспечивает отработку информации, заключенной между этими адресами, необходимое число раз. При этом исключается необходимость повторного включения в программу ранее встречавшихся кадров обработки, что существенно сокращает объем блоков постоянной памяти. Данное устройство позволяет конструировать программу, что упрощает процесс программирования и редактирования управляющих программ. 8 ил. 1 (Л оэ 00 о ел Ч ста

.2

Фив. 5

fJys;

.j.,,.Jl,™.Jl...Л.,.™Гг.

-- ™--.. -

l-..-J,,,„„....,

f..T

- -- ----- - - b..v-.

..,,r .,.„.-...,„..,„,...™..J

.-.,,,-, .„,„„.„™ ...,„.™.,„.™™,.

...,,„.„„..., ,„.,„„.

. ,„.,....„

. ,„.„.„J L-,-. „„™™-J l™,Г I i-i In

Ш

K.:r bс о с т а в и т е л ь И, Шве ц Редактор И. Рыбпенко Техред ИЛ1опопичКорректор И. Муска

Зак.с1з 7065/52Тираж 836Подписное

ВПИШта Государстзенного комитета СССР

1Ю делам изобретений и открытий Г1 Ш35„ MocKHoi. Ж-35, Раушская иаб., д, 4/5

Прпизводствеии(г-ао.11игр. ;ц)ичаское предприятие, . З жгород, ул. Проектная,4

. ,„.„.„J L-,-. „„™™-J l™,Ш

..„,,.,j.| f3

r -- -Я Ш

| ВПТБ | 0 |

|

SU408276A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приводы и системы управления для автоматизации станков | |||

| - Фирма Сименс, спец.вып | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1986-12-30—Публикация

1985-08-29—Подача