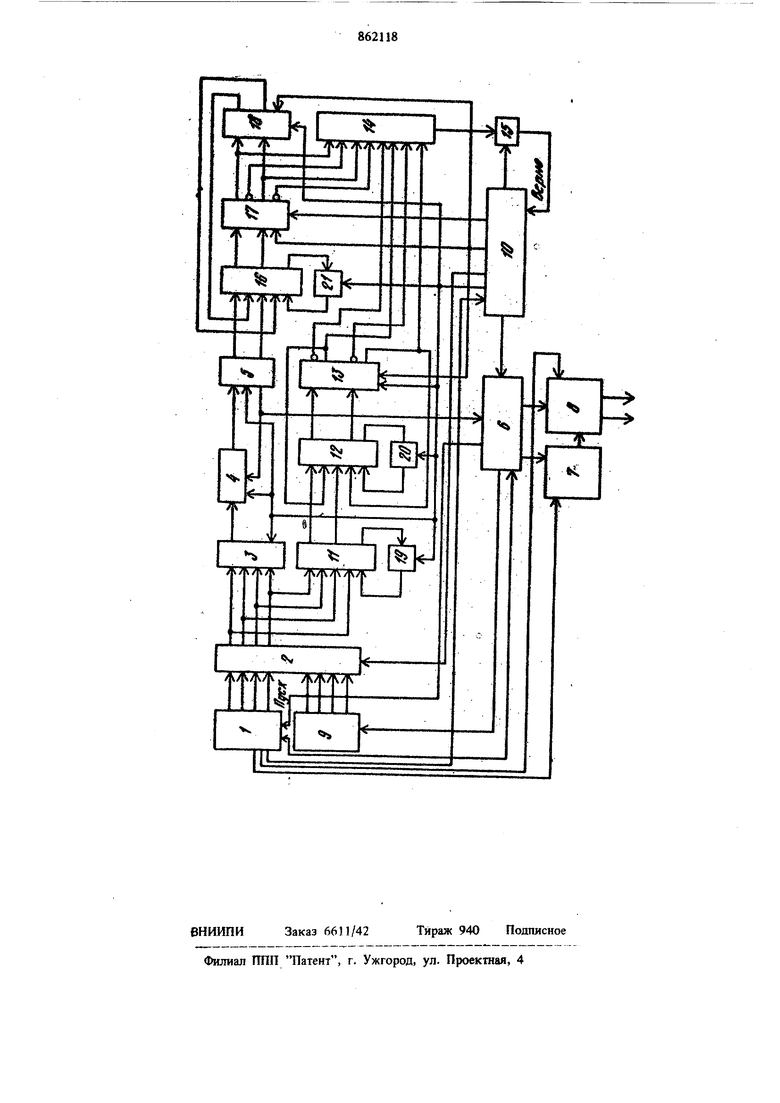

Изобретение относится к области автоматики и вычислительной техшжи и может быть использовано в системах шслового программного управлешш сгшвсами.. (Ьвестио устройство для программного управления, содержащее блок ввода программы, выход которого соеданен j с входами счетчика строк, прео азователя кода и блока памяти, соединенного со входами блока обработки коорюшатных перемещений и котрольиого счетчика но mod 9, причем выход блока отработки координатных перемещений соединен с входом коитро)Ш1ого счетиоса, входы элемента И соединены с выходами счетчика строк и . преобразсюателя кода, я дополнительньй счетчи по mod 9, вход которого соединеи с выходсмм элемента И, а выход - с блоке памяти 1. Недостатком этого устройства является то, что оно моясет обеспечивать контроль преобразования и отработки информации только от входд к выходу устройства и только в том случае, если код вводимой информации и. система исчисления блока от работки координат ных перемещений совпадают/Это условие огршшчивает функциональные возможностн устройства. Известно устройство для программного управлешш, содержащее блок формирования команд и последовательно соединенные блок ввода информации, дешифратор , регистры памяти технологических команд, блок сравнения, подключенный через регистр числа к блоку ввода информации, блок сум1«гарования, блок задания скорости, блок интертоляции, связанный с &IOKOM суммирования и блоifOM ПШ4ЯТИ и блсж управления приводом, Злок формирования команд соединен с блоком ввода информации и блоксим суммирования, устройство содержит также блок цифровой индика(ии, элемент сборки, блок коммутации, первый счеггак 1Шпульсов, последовательно соединенные блок выбега режима, блсж управления счет шками, второй счетчик импульг сов и преобразователь кода, выход которого подключен ко входу блока суммирования, а выхофл - к выходу блока формирования команд н входам регастра памяти технологических команд и блока цифровой индикации, другой ВХОД которого связан со входом блока сравнения и через первый счетчик импульсов с выходом блока управления счетчиками, входы Ko-oporo подключены к выходам дешифратора адреса, блока суммирования и блока ввода информадии, другой выход которого через блок выбора режима подсоединен к входу блока формирования команд, а вход - к выходу эле мента сборки, причем входы блока коммутации связаны с выходами блока задания скорости, блока памяти и блока формирования команд, а выход - с входами блока суммирования 2 Это устройство позволяет работать с преобразованной информацией. Однако способ перевода информации из десятичной гастемы в двоичную сложен, требует больших аппаратурных затрат. В устройстве трудно осуществлять непрерьшный контроль, поэтому в. нем применен тестовый контроль методом обратного преобразования двоичной информации в десятичн)ао с выводом результата на индикацию. Это не позволяет осуществлять контроль преобразования десятичной информации в двоичную в рабочих режимах, и следовательно, не обеспечивает должной глубины контроля. Кроме того, это требует больших затрат электронного оборудования, что повышает стоимость устройства. Наиболее близким техническим решением к изобретению является устройство для програ много управления, состоящее из последовательно соединенных фотосчитывающего устройства, устройства ввода информации со схемой перевода десять в два, генератора задания скорости интерполятора и блока управления приводом, а также устройства управления и блока буферной памяти, вход которого подключен к выходу устройства ввода, а выход - к интерполятору, другой вход которого также связан с устройством ввода, выходы устройства управления присоединены к входам всех блоков 3. Преимуществом этого устройства является возможность работать с информацией, заданной в разных системах кодарования, относительная простота перевода информации из десятичной системы счисления в двоичную. Недостатком устройства является отсутствие контроля преобразования информации из десятичной системы счисления в двоичную, что снижает надежность устройства, усложняет эксплуатацию, ocotJeHHo при большом количестве внешних источников информации. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в устройство для задания программы, содержащее последовательно соединенные блок управления, согласующий блок, блок коррекции, коммутатор, первый сдвигающий регистр, блок преобразователей кода и второй сдвигающий регистр, первый выход которого подключен к вторым входам блока преобразователей кода и согласующего блока, соединенного вторым, третьим и четвертым выходами с первыми входами соответственно блока задания скорости, интерполятора и блока ввода информации, первые выходы которого подключены к вторым входам коммутатора, а вторые выходы - к вторым входам согласующего блока, блока заданияскорости и интерполятора, соединенного третьим входом с выходом блока задания скорости, введены блок сравнение, первый, второй, третий и четвертый элементы И, последовательно соединенные первьга двухразрядный комбинационный сумматор, второй двухразряд1П11Й комбинационный сумматор и первый двухразрядный регистр и последовательно соединенные третий двухразрядный комбинационный сумматор, второй двухразрядный регистр и третий двухразрядный регистр, выходы которого соединены с первыми входами третьего двухразрядного комбинационного сумматора, второй вход с вторыми входами первого и второго двухразрядных регистров и с вторым выходом блока управления, а третий вход - с первыми входа,ми второго, третьего и четвертого элементов И, с третьим входом первого двухразрядного регистра, с вторыми входами блока преобразователей кода и первого и второго сдвигающих регистров и с третьим выходом блока управления, четвертый, пятый и шестой выходы которого подключены соответственно к третьему входу коммутатора, к третьему входу второго двухразрядного регистра и к первому входу первого элемента И, соединенного выходом со вторым входом блока управления, а вторым входом - с выходом блока сравнения, входы которого подключены к выходам первого и второго двухразрядных регистров, вторые входы второго двухразрядного комбинационного сумматора соединены с соответствующими выходами первого двухразрядного регистра, а третий вход и второй выход - соответстве1шо с выходом и вторым входом третьего элемента И, первые входы первого двухразрядного комбинационного- сумматора подключены к выходам коммзтатора, а вторые вход и выход - соответственно к выходу и второму входу второго элемента И, причем вторые входы третьего двухразрядного комбинационного сумматора соединены с выходами второго сдвигового регистра, а третий вход и второй выход - соответственно с выходом и вторым входом червертого элемента И. Структурная схема предлагаемого устройства изображена на чертеже, оно содержит блок 1 ввода информации, коммутатор 2, первый сдвигающий регистр 3, блок 4 преобразователей кода, второй сдвигающий регистр 5, согласующий блок 6, блок 7 задания скорости, интерполятор 8, блок 9 коррекции, блок 10 управления, первый 11 и второй 12 двухразряд ные комбинационные сумматоры, первый двухразрядный регистр 13, построенный на 7 К-триг герах, блок 14 сравнения, первый элемент 15 И третий двухразрядный комбинационный суммато 16, второй 17 и третий 18 двухразрядные регис ры, второй 19, третий 20 и четвертый 21 элементы И. Работает устройство следующим образом. Информация программы с некоторого внешнего устройства, например цифрового ма-китофона, дисплея, оперативной памяти, фотосчитывателя, внешнего канала связи с ЭВМ или другого источника поступает на вход блока I, где происходит ее дешифрирование и распределение следующим образом: информация, дальнейшая отработка которой должна вьшолняться в двоичной форме, поступает на вход коммутатора 2 (информация о величинах перемещений и численных значениях скоростей подач), инфор мация о режимах работы блока 7 поступает на вход этого блока (информация о способах кодирования подачи мм/об, мм/мм, масштабирование, признак торможения и т. д.), инфсфмация о режимах работы интерполятс 8 (тип интерполяции или резьбы) поступает на вход интерполятора 8, подготовительные функции, определяющие алгоритмы преобразования вводимой информации, поступают в блок б, синхроимпульсы и вспомогательные сигналы, типа Конец кадра, Условный остаяоь, и т. д. поступают в блок 10. При вводе десятичной информаюш через блок 1 сигнал с выхода блока 10 устанавливает такое состояние коммутатора 2, что выходы блока9 отключены от регистра 3 и сумматора 11, а выходы блока 1 подключены. Благодаря этому десятичная информация поразрядно эгаш;сывается в регистр 3, в котором сдвигается младшими разрядами вперед и поступает в блок 4 для перевода десятичной информации в двоичную, откуда переписывается уже в двоичном виде в регистр 5 также младшими Двоично-десятичная 800 400 200 1000 80

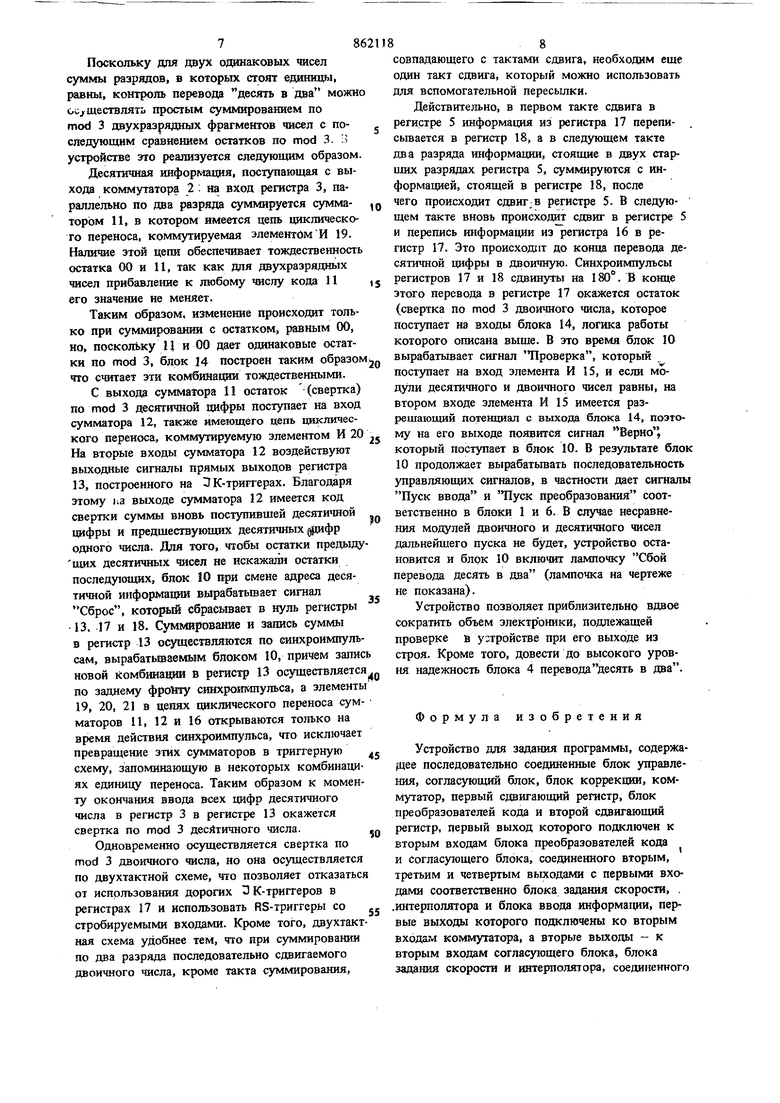

запись

1 21 21 nrod 3 разрядами вперед. Из регистра 5 информаийгг в процессе перевода всех десятичных чисел циркулирует по цепи; регистр 5, блок 4 регистр 5, а по окончании перевода поступает в блок 6, где и преобразуется согласно заданному из блока 1 в блок 6 алгоритму. Если в процессе пр образования вводимой информации необходима ее коррекция на некоторую величину, хранимую в блоке 9, то благодаря переключению коммутатора она аналогично пересылается в блок 6 и при этом переводится в двоичную форму. С выхода блока 6 информацня, необходимым образом преобразованная и подготовленная, пересылается в блок.7 и интерполятор 8. Блок 7 вырабатывает частоту подачи, которая поступает в интерполятор 8 и зпправляет скоростью его работы. Интерполятор 8 отрабатывает заданный кадр, и его выходные сигналы, поступая на вход приводов станка (на чертеже не показаны), обеспечивают обработку детали. Устройство состоит из двух приблизительно равных по объему электронного оборудования частей, которые отличаются способом представления информации. Действительно информация в блоке 1 с его сложными внешними устройствами (фотосчитывающим устройством, цифровым магнитофоном, дисплеем, ЗУ и т. д.), а .также в блоке 9 представлена в коде 3 SO и двоично-десятичном виде, в то время как в остальных блоках системы, куда она пересылается через блок 4, она используется в двоичном коде. В случае возникновения сбоя или неисправности, их локализация и ремонт крайне затруднены из-за различия одинаковой информации, заданной в разных кодах в различных блоках системы. Локализация и исправление неисправностей и сбоев значительно упрощаются, если известно, что сбой произошел в каналах десятичной или двоичной информации, т. е. до шш после преобразования деся1 в два. Для выяснения этого служит тракт контроля перевода двоичной информацни в десятичную, работа которого основана на свойстве совпадения остатков по модулю 3 однонменных разрядов двоичных и двоично-десятичных чисел, что видно из таблицы. 40 20 10 84 21 Остаток

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

2048 1024 512

Двоичная запись

64 32 16 84 21

256 128

Остаток

1 21 21 mod 3 Посксшьку для двух одинаковых чисел суммы разрядов, в которых стоят единицы, равны, контроль перевода десять в два можн о/ществлятй простым суммированием по mod 3 двухразрядных фрагментов чисел с последующим сравнением остатков по mod 3. ; устройстве это реализуется следующим образом Десятичная информация, поступающая с выхода коммутатора 2 на вход регистра 3, параллельно по два разряда суммируется сумматором 11, в котором имеется цепь циклического переноса, коммутируемая элементомИ 19. Наличие этой цепи обеспечивает тождественность остатка 00 и 11, так как для двухразрядных чисел прибавление к любому числу кода 11 его значение не меняет. Таким образом, изменение происходит только при суммировании с остатком, равным 00, но, поскольку U и 00 дает одинаковые остатки по mod 3, блок 14 построен таким образом что считает эти комбинащш тождественными. С выхода сумматора 11 остаток (свертка) по mod 3 десятичной цифры поступает на вход сумматора 12, также имеющего цепь циклического переноса, коммутируемую элементом И 20 На вторые входы сумматора 12 воздействуют выходные сигналы прямых выходов регистра 13, построенного на 3 К-триггерах. Благодаря этому ha выходе сумматора 12 имеется код свертки суммы вновь поступившей десятичной цифры и предшествующих десятичных фр одного числа. Для того, чтобы остатки предыду щих десятичных чисел не искажали остатки последующих, блок 10 при смене адреса десятичной информации вырабатьшает сигнал Сброс, который сбрасывает в нуль регистры 13, 17 и 18. Суммирование и запись суммы в регистр 13 осуществляются по синхроимпульсам, вырабатьшаемым блоком 10, причем запис новой Комбинации в регистр 13 осуществляется по заднему фройту синхро11мпульса, а элементы 19, 20, 21 в цепях циклического переноса сумматоров 11, 12 и 16 открываются только на время действия синхроимпульса, что исключает превращение этих сумматоров в триггерную схему, запоминающую в некоторых комбинациях единицу переноса. Таким образом к моменту окончания ввода всех цифр десятичного числа Б регистр 3 в регистре 13 окажется свертка по mod 3 десйтичного числа. Одновременно осуществляется свертка по mod 3 двоичного числа, но она осуществляется по двухтактной схеме, что позволяет отказаться от использования дорогих 3 К-триггеров в регистрах 17 и использовать RS-триггеры со стробируемыми входами. Кроме того, двухтакт ная схема удобнее тем, что при суммировании по два разряда последовательно сдвигаемого двоичного числа, кроме такта суммирования. совпадающего с тактами сдвига, необходим еще один такт сдвига, который можно использовать для вспомогательной пересылки. Действительно, в первом такте сдвига в регистре 5 информация из регистра 17 переписывается в регистр 18, а в следующем такте два разряда информации, стоящие в двух старших разрядах регистра 5, суммируются с информацией, стоящей в регистре 18, после чего происходит сдвиг; в регистре 5. В следующем такте вновь происходит сдвиг в регистре 5 и перепись информации из регистра 16 в регистр 17. Это происходит до конца перевода десятичной цифры в двоичную. Синхроимпульсы регистров 17 и 18 сдвинзггы на 180°. В конце этого перевода в регистре 17 окажется остаток (свертка по mod 3 двоичного числа, которое поступает на входы блока 14, логика работы которого описана выше. В это время блок 10 вырабатывает сигнал Проверка, который поступает на вход элемента И 15, и если модули десятичного и двоичного чисел равны, на втором входе элемента И 15 имеется разрешающий потенциал с выхода блока 14, поэтому на его выходе появится сигнал Верно который поступает в блок 10. В результате блок 10 продолжает вырабатьгеать последовательность управляющих сигналов, в частности дает сигналы Пуск ввода и Пуск преобразования соответственно в блоки 1 и 6. В случае несравнения модулей двоичного и десятичного чисел дальнейшего пуска не будет, устройство остановится и блок 10 включит лампочку Сбой перевода десять в два (лампочка на чертеже не показана). Устройство позволяет приблизительно вдвое сократить объем электроники, подлежащей проверке в устройстве при его выходе из строя. Кроме того, довести до высокого уровня надежность блока 4 перевода десять в два. Формула изобретения Устройство для задания программы, содержащее последовательно соединенные блок управления, согласующий блок, блок коррекции, коммутатор, первый сдвигающий регистр, блок преобразователей кода и второй сдвигающий регистр, первый выход которого подключен к вторым входам блока преобразователей кода и согласующего блока, соединенного вторым, третьим и четвертым выходами с первыми входами соответственно блока задания скорости, . интерполятора и блока ввода информа1щи, первые выходы которого подключены ко вторым входагг коммутатора, а вторые выходы - к вторым входам согласующего блока, блока задания скорости и интерполятора, соединенного 98 третьим входом с выходом блока задания скорости, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок сравнения, первый, второй, третий и четвертый элементы И, последсжательно соединенные первый двухразрядный комбина ционный сумматор, второй двухразрядный комбинационный сумматор л первый двухразрядный регистр и последсюательно соединенные третий двухразрядный комбинацисягаый сумматор, второй двухразрядный регистр и тетий даухраз{Н даый регастр, выходал косорото соединены е первыми входами третьего двухраэ| 1пного ком&1наииснгаого сумматора, второй вход - с вторыми входами пертого и даухразрядшах, регистров и с выходом блока управлешш, а третий вход - с трвымя входакв второто, третьего и четвертого х меятов И, с третьим входом пертого даухраэрядкого регистра, с вторыми входами блока преобразователи кода и первого и второго сдвигающих регастров я с третьим выходом блока управления, 1етверт й, пятый и шестой выходы которого подключены соответственно к третьему входу коммутатора, к третьему входу второго двухразрядного регистра и к первому входу первого элемента И, соединешюго выходе с вторым входом блока уяравлеюи, а вторым входом - с выходом ка сравнения, входы которою подключены к выходам первого и второго двухразрядных регистров, вторые входы второго двухраэрядного комбинационного сумматора соединены с соответствующими выходами первого двухразрядного регистра, а третий вход и второй ,выход - соответственно с выходом и вторым входом третьего элемента И, первые входы iie{moro двухразрядного комбинационного сумматора подключены к выходам коммутатора, а вторые вход и выход - соответственно к выходу и второму входу второго элемента И, причем вторые входы третьего двухразрядного комбинационного сумматора соединены с выходами второго сдвигового регистра, а третий вход и второй выход - соответственно с выходом и вторым входом четвертого элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР И 397891, кл. G 05 В 19/14, 1971. 2.Авторское свидетельство СССР № 517004, кл. G 05 В 19/18, 1974. 3.Сб. Электроавто№ тика станков, способы подготовки программ и интерполяторы для, контурных систем «елового управления станками. М., Машиностроетю, 1970, с. 43-47 (проготяп).

Авторы

Даты

1981-09-07—Публикация

1979-12-29—Подача