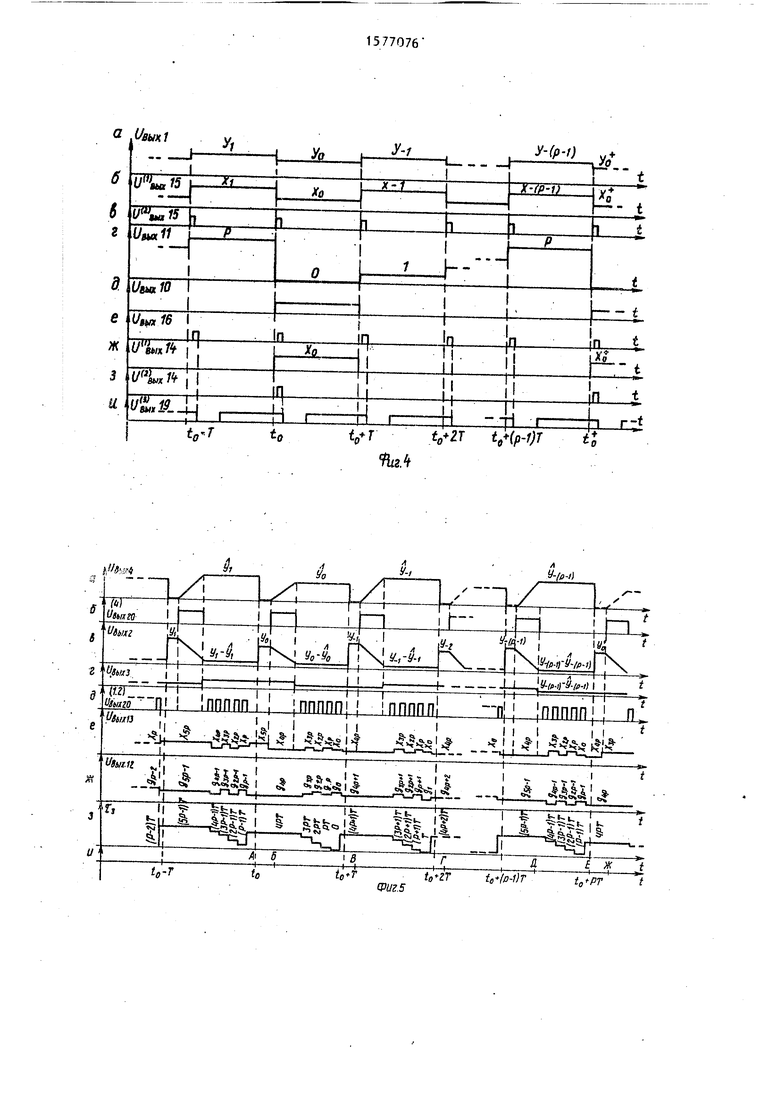

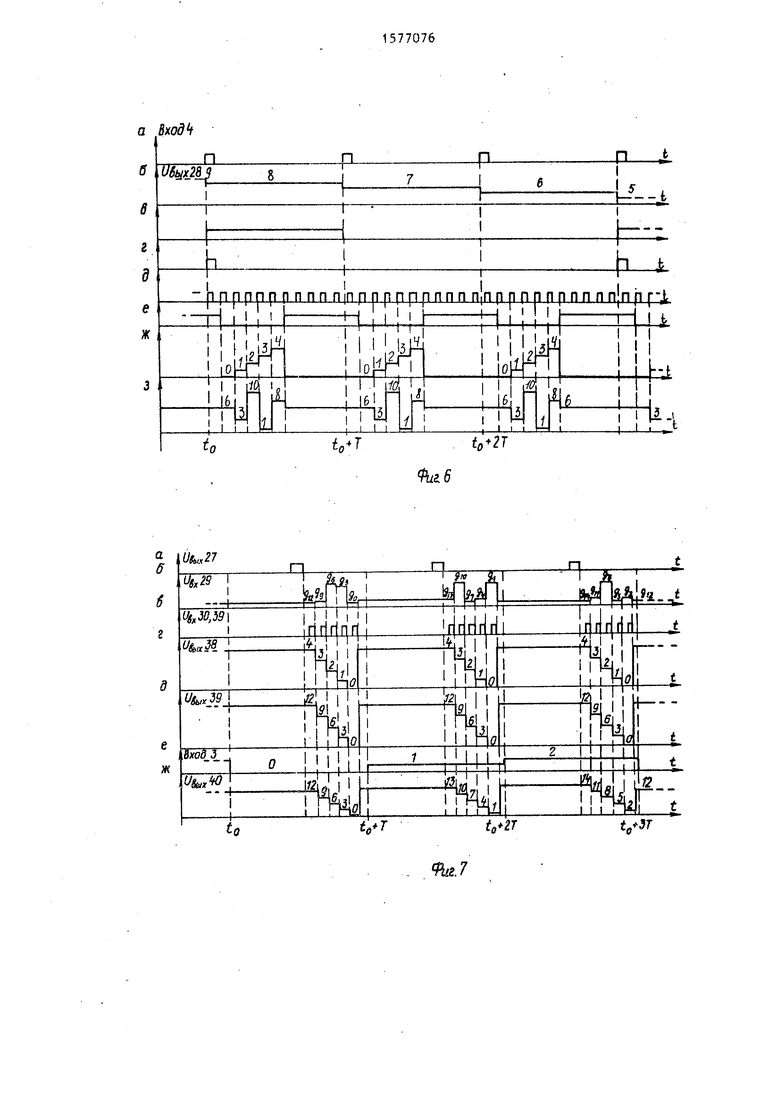

Т1, при этом выходной сигнал D-триг- случае равном шести), значение которогера 25 устанавливает в нулевое состояние первый счетчик 26 и определяет режим работы первого, второго и третьего коммутаторов 32,34,41, при которых сигналы проходят на их выходы с третьих входов. Третий счетчик 31 в указанный момент времени находится в одном из разрешенных состояний, например девятом, т.е. сигнал на его выходе образует двоичный код числа девять.

В начальный момент времени с перво го выхода второго аналого-цифрового преобразователя 15 на вход блока 19

50

55

го превышает пороговое.

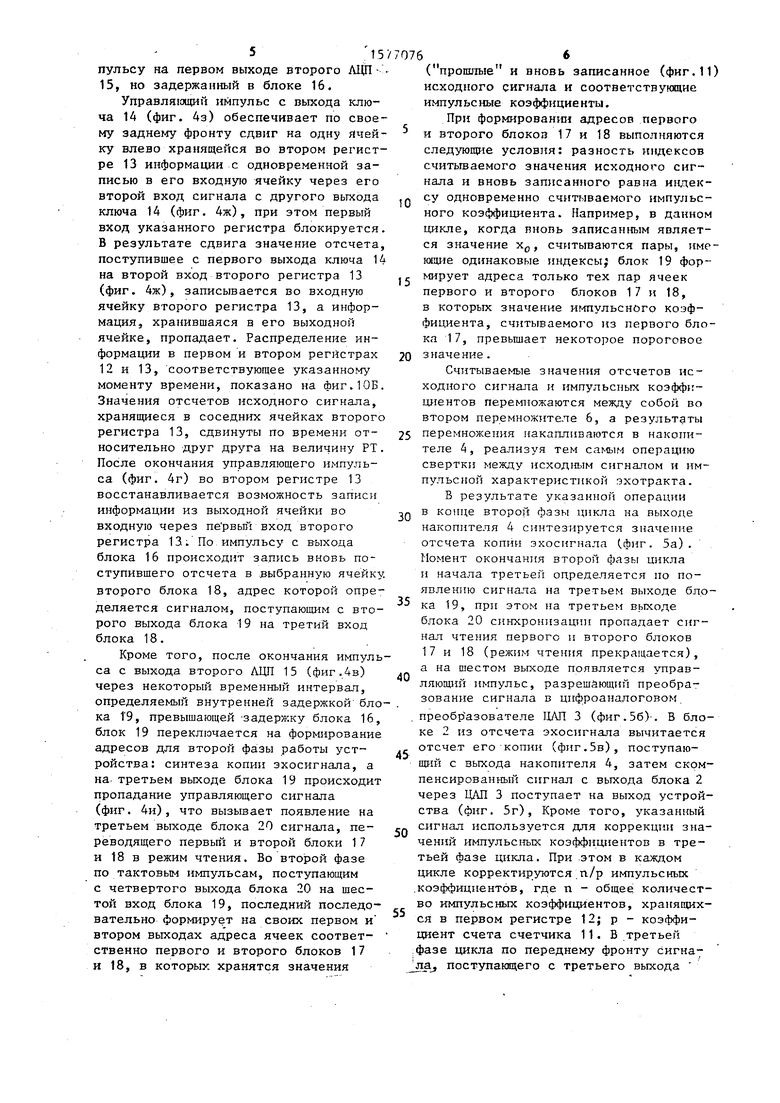

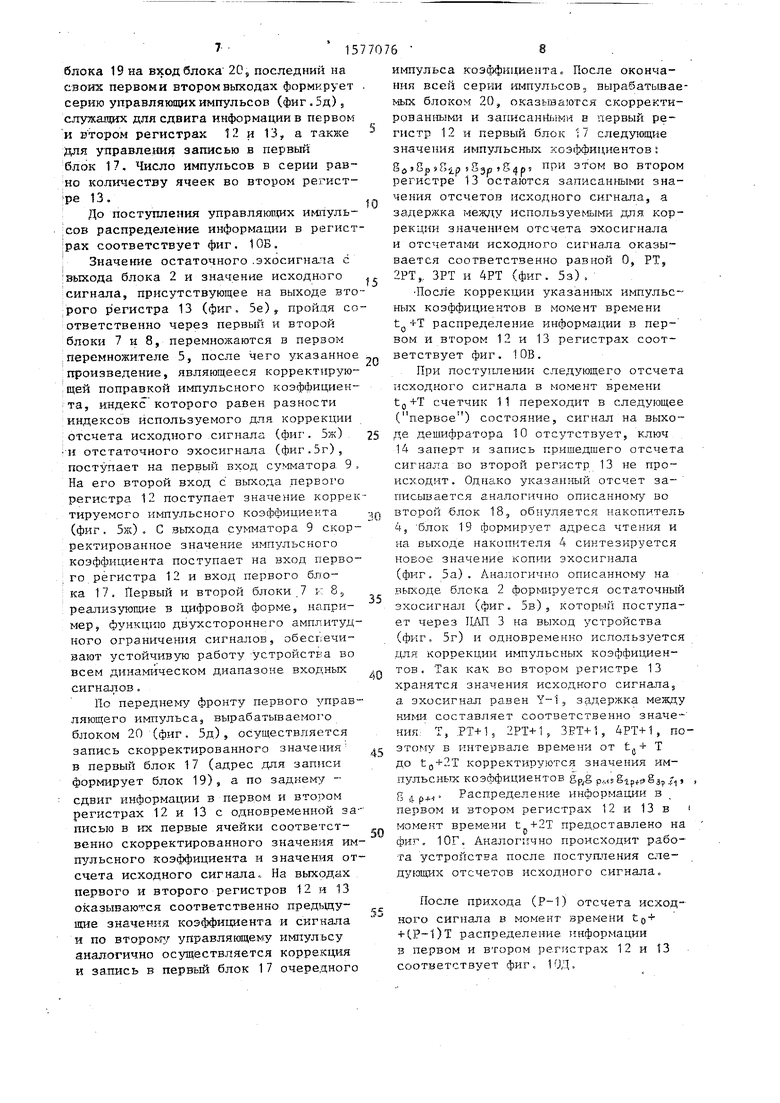

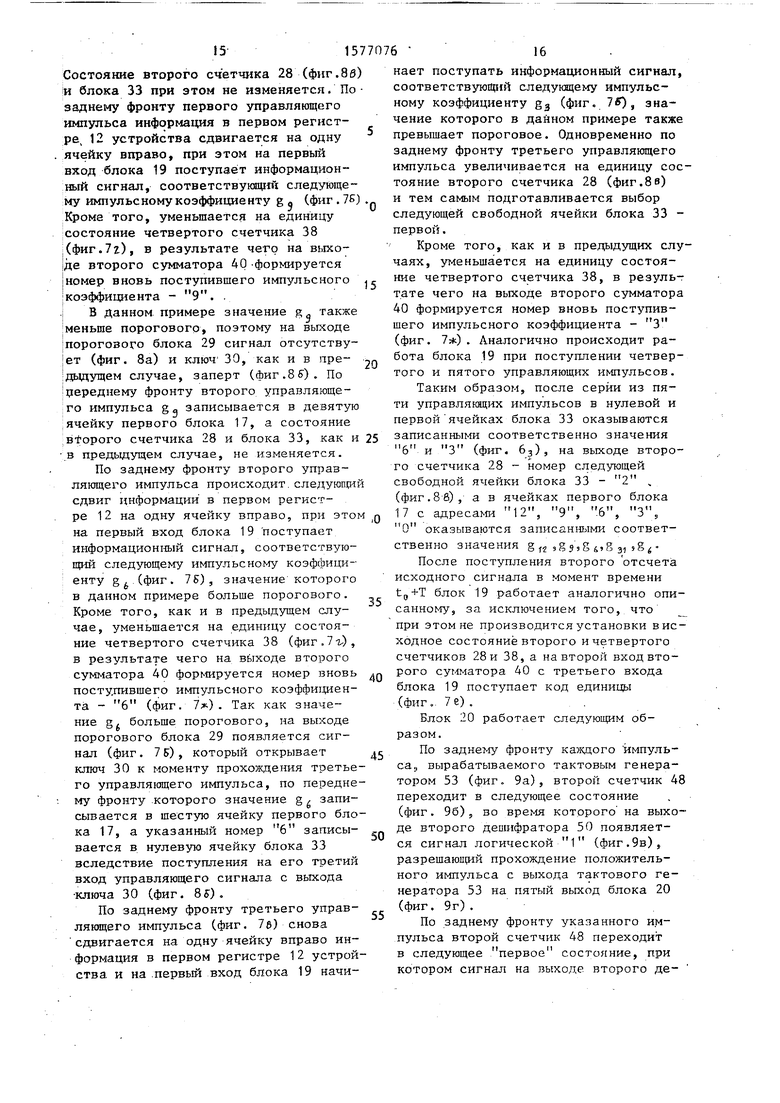

Далее информация о номере импульсного коэффициента поступает через тре тий коммутатор 41 на первый выход блока 19, образуя адрес ячейки первого блока 17 (фиг. 8), а также через второй коммутатор 34 на второй вход первого сумматора 35, выступая в данном случае в роли относительного номера выбираемой ячейки второго блока 18. В первом сумматоре 35 указанный номер складывается с номером начальной ячейки, поступающим с выхода третьего счетчика 31 (фиг. 66), при этом на

0

5

го превышает пороговое.

Далее информация о номере импульсного коэффициента поступает через тре тий коммутатор 41 на первый выход блока 19, образуя адрес ячейки первого блока 17 (фиг. 8), а также через второй коммутатор 34 на второй вход первого сумматора 35, выступая в данном случае в роли относительного номера выбираемой ячейки второго блока 18. В первом сумматоре 35 указанный номер складывается с номером начальной ячейки, поступающим с выхода третьего счетчика 31 (фиг. 66), при этом на

выходе первого сумматора 35 и соответственно на втором выходе блока 19 (см. фиг. 8i) формируется адрес выбираемой ячейки второго блока 18.

После прохождения следующего тактового импульса первый счетчик 26 переходит в состояние 1 (фиг. бж), считывается содержимое первой ячейки блока 33 (фиг. 6з), несущее информацию о следующем номере импульсного коэффициента, значение которого превышает пороговое (в данном примере 3) и формируются следующие адреса первого и второго блоков 17 и 18, в данном примере соответственно равные (см. фиг. 8) и 11 (фиг.8,).

Аналогично из блока 33 считываются остальные номера импульсных коэффициентов, значение которых превышает пороговое, в данном примере - 10,1, 8 (фиг. 6з) , а на первом и втором выходах блока 19 формируются соответствующие им адреса соответственно второго (фиг. 8i) и первого (фиг. 8 Э) блоков 18 и 17, в данном примере соответственно 3, 9, 1 и 10, 1, 8.

Блок 19 программируется на определенное максимальное количество импульсных коэффициентов, значение которых больше порогового. Это количество определяет код числа на выходе первого счетчика 26, при котором на выходе дешифратора 27 появляется сигнал, опрокидывающий RS-триггер 22.

В данном примере указанное количество импульсных коэффициентов рав- но пяти. Поэтому появление сигнала на выходе дешифратора 27 (фиг.7о() и опрокидывает RS-триггера 22 происходит при переходе первого счетчика 26 в четвертое состояние (фиг.бж). После указанного события логическая 1 с выхода RS-триггера 22 через элемент ИЛИ 23 и блок 24 поступает на первый вход D-триггера 25, который переходит в состояние 1 после прихода следующего тактового импульса (фиг. бе), при этом обнуляется первый счетчик 26, переключаются первый, второй и третий коммутаторы 32,34 и 41, а на третьем выходе блока .19 появляется положительный перепад уровня, по которому запускается блок 29, вырабатывающий серию управляющих импульсов, по которым осуществляется сдвиг информации в первом и втором регистрах 12 и 13, запись информации

5

0

5

в первый блок 17, а также синхронизация работы1блока 19.

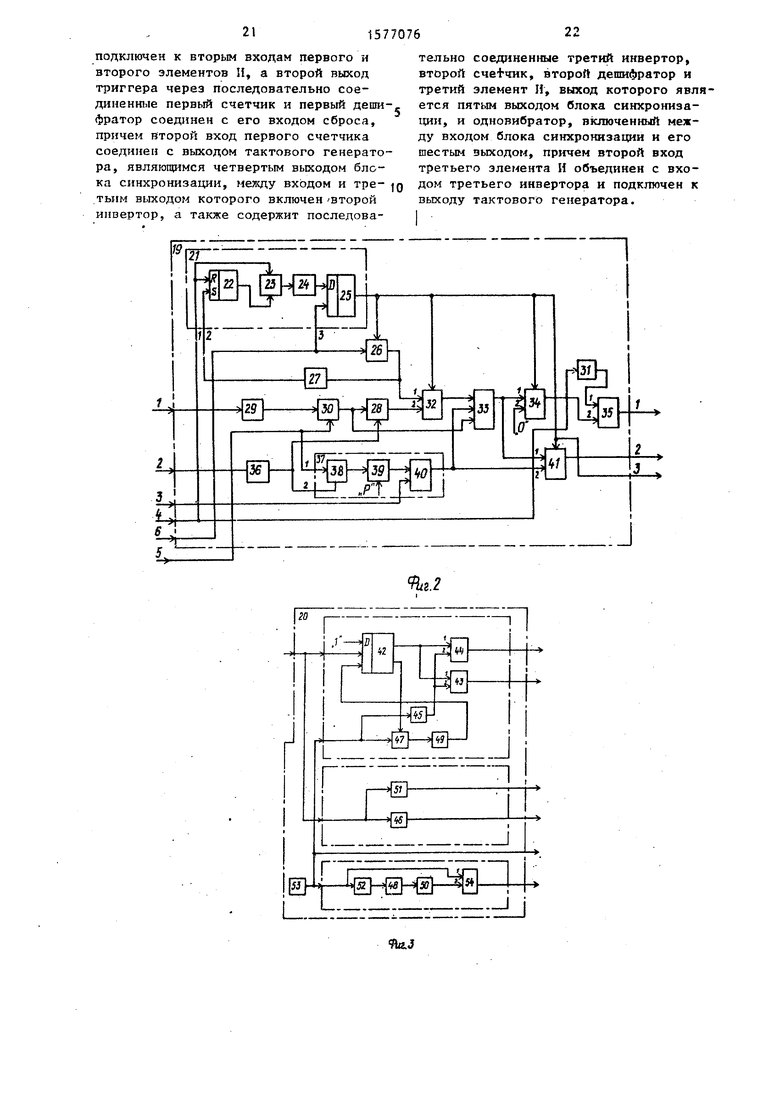

Число управляющих импульсов в серии равно количеству ячеек во втором регистре 13, в данном примере - пяти. Информационный сигнал с входа первого регистра 12 поступает на первый вход блока 19, и далее на вход порогового блока 29 (фиг. 75), а управляющий - с второго выхода блока 20 на пятый вход блока 19 и далее на один из входов ключа 30 и на вход четвертого счетчика 38 (фиг. 76). В данном примере непосредственно до поступления первого управляющего импульса информационный сигнал на выходе порогового блока 29 соответствует значению импульсного коэффициента g (фиг. 75), сигнал на выходе второго счетчика 28 соответствует коду нуля (фиг. 8 б), что определяет выбор нулевой ячейки блока 33, сигнал на выходе четвертого счетчика 38 равен коду числа 4 (фиг. 7г), на выходе перемножн- теля 39 - коду числа 12 (фиг. 73), сигнал, поступающий с третьего входа блока 19 на второй вход второго сумматора 40, равен коду нуля (фиг.7е) и сигнал на выходе второго сумматора 40 равен коду числа 12, что соответствует номеру поступающего на первый вход блока 19 импульсного коэффициента.

С выхода второго сумматора 40 код числа 12 поступает на второй вход (вход данных) блока 33, подготавливая запись числа 12 в нулевую ячейку указанного элемента в том случае, ес- Q ли значение g превышает пороговое (если значение g ниже порогового, указанная запись не производится), а также через третий коммутатор 41 на первый выход блока 19, осуществляя 5 в первом блоке 17 выбор двенадцатой ячейки (фиг. 89).

Б пороговом блоке 29 происходит сравнение значения импульсного коэффициента с пороговым и в зависимости от результата сравнения - управление ключом 30 (фиг. ) В данном примере значение gK меньше порогового, поэтому ключ 30 заперт (фиг. 8г).

По переднему фронту первого управляющего импульса (фиг. 7в) информация о значении импульсного коэффициента g 1t записывается в ячейку первого блока 17, адрес которой определяется сигналом на первом выходе блока 19.

0

5

0

5

151577076

Состояние второго счетчика 28 (фиг.80) и блока 33 при этом не изменяется. По - заднему фронту первого управляющего импульса информация в первом регистре, 12 устройства сдвигается на одну ячейку вправо, при этом на первый вход блока 19 поступает информационный сигнал, соответствующий следующему импульсному коэффициенту g « (фиг . IS) Кроме того, уменьшается на единицу состояние четвертого счетчика 38 (фиг.7г), в результате чего на выходе второго сумматора 40 -формируется номер вновь поступившего импульсного коэффициента - 9. .

15

20

В Данном примере значение g,. также еньше порогового, поэтому на выходе орогового блока 29 сигнал отсутствут (фиг. 8а) и ключ1 30, как и в преыдущем случае, заперт (фиг.8Ј). По ереднему фронту второго управляющео импульса gg записывается в девятую чейку первого блока 17, а состояние торого счетчика 28 и блока 33, как и 25 в предыдущем случае, не изменяется.

По заднему фронту второго управляющего импульса происходит следующий сдвиг информации в первом регистре 12 на одну ячейку вправо, при этом PQ на первый вход блока 19 поступает информационный сигнал, соответствующий следующему импульсному коэффициенту g (фиг. 75), значение которого в данном примере больше порогового. Кроме того, как и в предыдущем случае, уменьшается на единицу состояние четвертого счетчика 38 (фиг.7г-), в результате чего на выходе второго сумматора 40 формируется номер вновь поступившего импульсного коэффициента - 6 (фиг. 7). Так как значение g, больше порогового, на выходе порогового блока 29 появляется CHI- нал (фиг. 7 Ј) , который открывает ключ 30 к моменту прохождения третьего управляющего импульса, по переднему фронту которого значение g записывается в шестую ячейку первого блока 17, а указанный номер 6 записывается в нулевую ячейку блока 33 вследствие поступления на его третий вход управляющего сигнала с выхода ключа 30 (фиг. 85).

По заднему фронту третьего управляющего импульса (фиг. 76) снова сдвигается на одну ячейку вправо информация в первом регистре 12 устройства и на первый вход блока 19 начи35

40

45

50

55

16

5

0

5

PQ

5

40

45

50

55

нает поступать информационный сигнал, соответствующий следующему импульсному коэффициенту ga (фиг. 76) значение которого в данном примере также превышает пороговое. Одновременно по заднему фронту третьего управляющего импульса увеличивается на единицу состояние второго счетчика 28 (фиг.8в) и тем самым подготавливается выбор следующей свободной ячейки блока 33 - первой.

Кроме того, как и в предыдущих случаях, уменьшается на единицу состояние четвертого счетчика 38, в результате чего на выходе второго сумматора 40 формируется номер вновь поступившего импульсного коэффициента - 3 (фиг. 7). Аналогично происходит работа блока 19 при поступлении четвертого и пятого управляющих импульсов.

Таким образом, после серии из пяти управляющих импульсов в нулевой и первой ячейках блока 33 оказываются записанными соответственно значения 6 и 3 (фиг. 63), на выходе второго счетчика 28 - номер следующей свободной ячейки блока 33 - 2 , (фиг. 8 6), а в ячейках первого блока 17 с адресами 12м, 9, 6, 3, О оказываются записанными соответственно значения g ,f ,gs,g &,g 3 ,gt.

После поступления второго отсчета исходного сигнала в момент времени t0+T блок 19 работает аналогично описанному, за исключением того, что при этом не производится установки в исходное состояние второго и четвертого счетчиков 28 и 38, а на второй вход второго сумматора 40 с третьего входа блока 19 поступает код единицы (фиг. 7 е) .

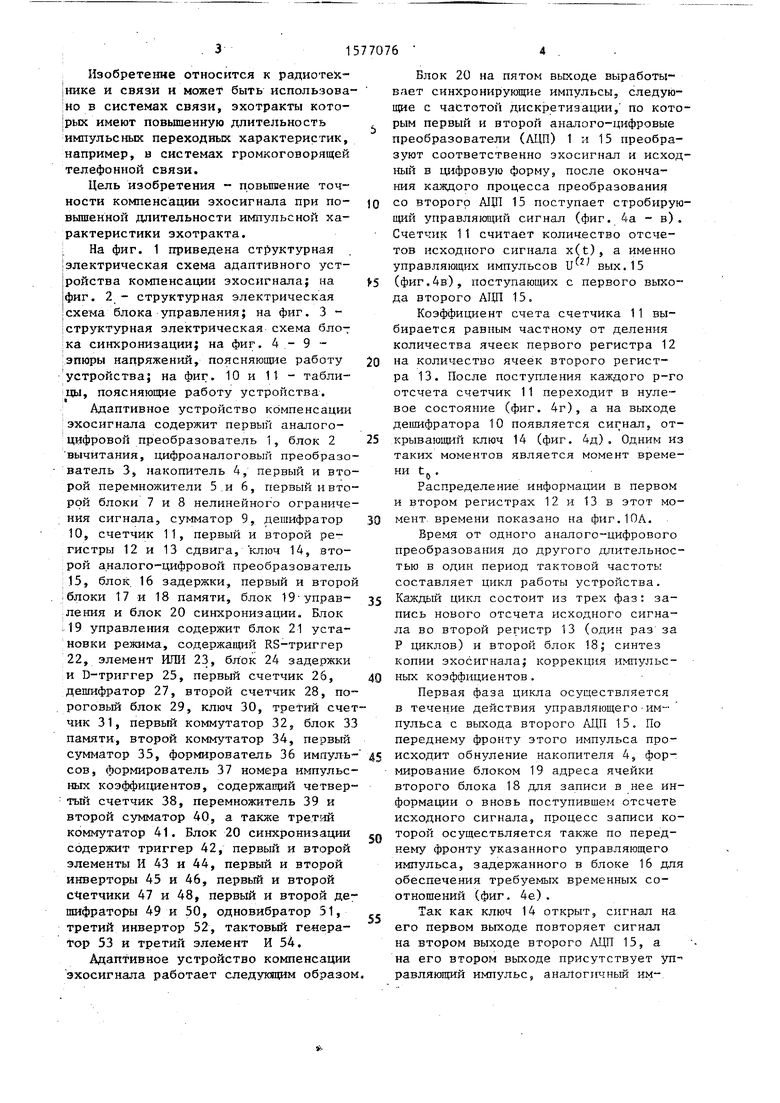

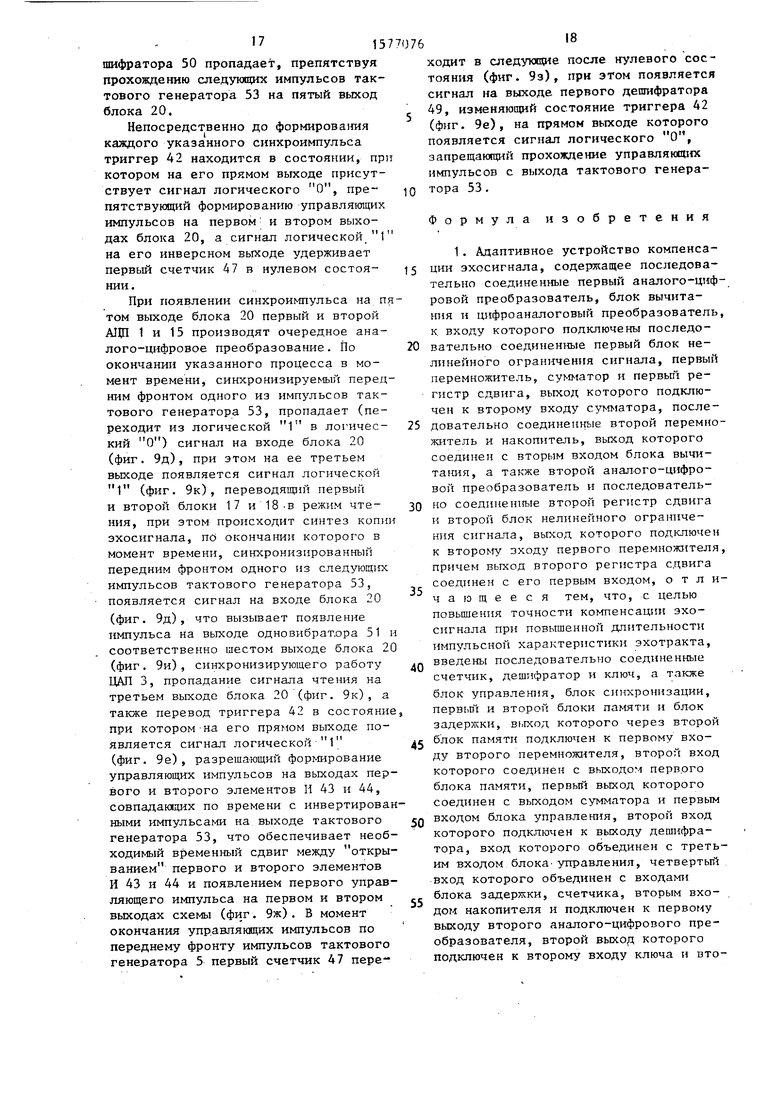

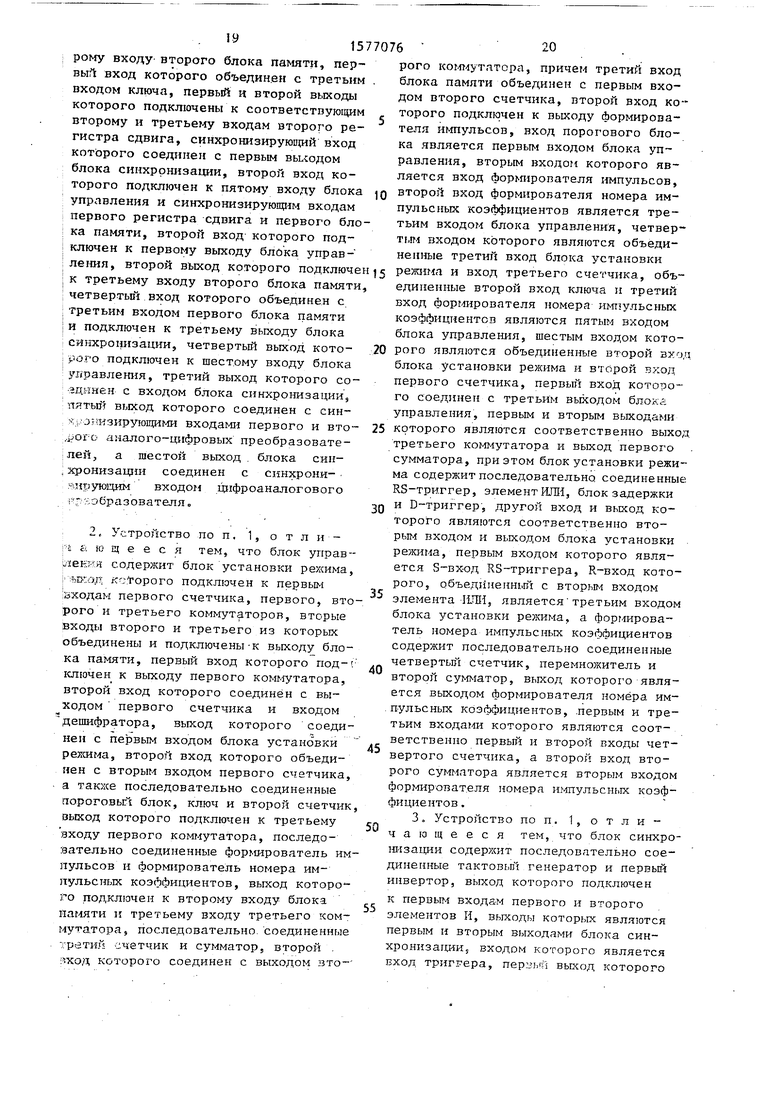

Блок 20 работает следующим образом.

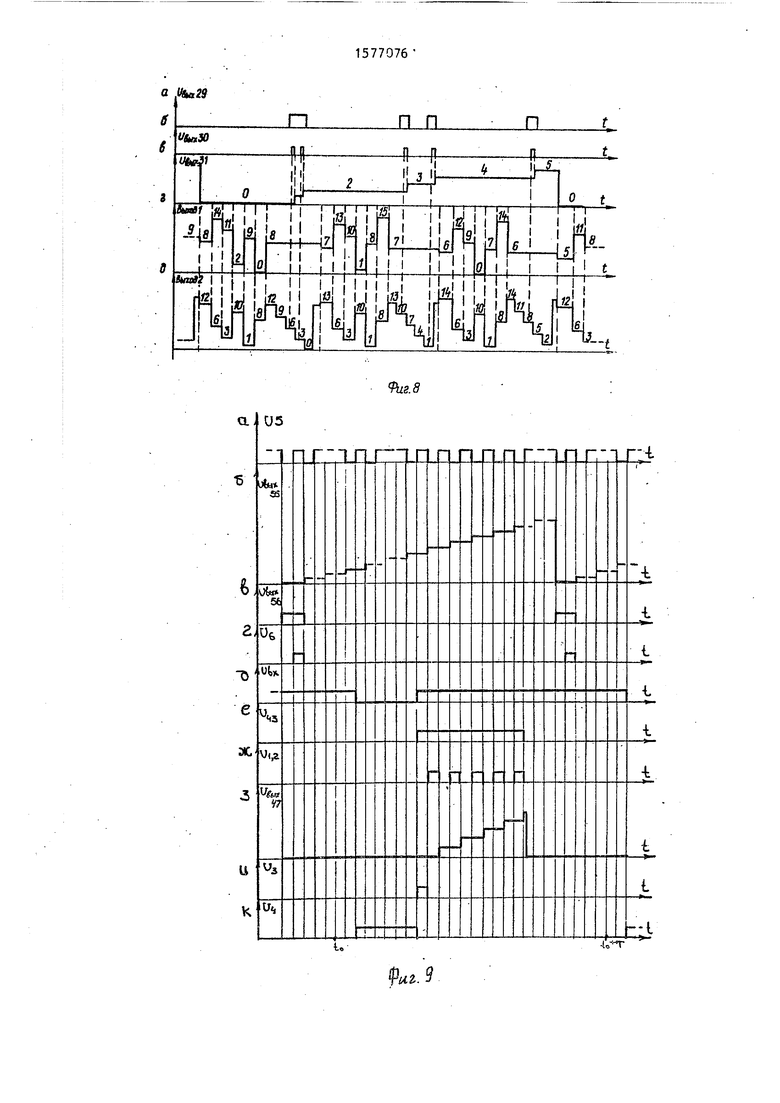

По заднему фронту каждого импульса, вырабатываемого тактовым генератором 53 (фиг. 9а), второй счетчик 48 переходит в следующее состояние (фиг. 96), во время которого на выходе второго дешифратора 50 появляется сигнал логической 1 (фиг.9в), разрешающий прохождение положительного импульса с выхода тактового генератора 53 на пятый выход блока 20 (фиг. 9г).

По заднему фронту указанного импульса второй счетчик 48 переходит в следующее первое состояние, при котором сигнал на выходе второго де

17157

шифратора 50 пропадает, препятствуя прохождению следующих импульсов тактового генератора 53 на пятый выход блока 20.

Непосредственно до формирования каждого указанного синхроимпульса триггер 42 находится в состоянии, при котором на его прямом выходе присутствует сигнал логического О, пре- пятствукщий формированию управляющих импульсов на первом и втором выходах блока 20, а сигнал логической,1 на его инверсном выходе удерживает первый счетчик 47 в нулевом состоянии.

При появлении синхроимпульса на пятом выходе блока 20 первый и второй АЦП 1 и 15 производят очередное аналого-цифровое преобразование. По окончании указанного процесса в момент времени, синхронизируемый передним фронтом одного из импульсов тактового генератора 53, пропадает (переходит из логической 1 в логический О) сигнал на входе блока 20 (фиг. 9д), при этом на ее третьем выходе появляется сигнал логической 1 (фиг. 9к), переводящий первый и второй блоки 17 и 18 в режим чтения, при этом происходит синтез копии эхосигнала, по окончании которого в момент времени, синхронизированный передним фронтом одного из следуюппгх импульсов тактового генератора 53, появляется сигнал на входе блока 20 (фиг. 9д), что вызывает появление импульса на выходе одновибрат.ора 51 и соответственно шестом выходе блока 20 (фиг. 9и), синхронизирующего работу ДАЛ 3, пропадание сигнала чтения на третьем выходе блока 20 (фиг. 9к), а также перевод триггера 42 в состояние при котором на его прямом выходе появляется сигнал логической 1 (фиг. 9е), разрешающий формирование управляющих импульсов на выходах первого и второго элементов И 43 и 44, совпадающих по времени с инвертированными импульсами на выходе тактового генератора 53, что обеспечивает необходимый временный сдвиг между открыванием первого и второго элементов И 43 и 44 и появлением первого управляющего импульса на первом и втором выходах схемы (фиг. 9ж). В момент окончания управляющих импульсов по переднему фронту импульсов тактового генератора 5 первый счетчик 47 пере

5

0

5

76

0

5

0

5

0

5

18

ходит в следующие после нулевого состояния (фиг. 9з), при этом появляется сигнал на выходе первого дешифратора 49, изменяющий состояние триггера 42 (фиг. 9е), на прямом выходе которого появляется сигнал логического О, запрещающий прохождение управляющих импульсов с выхода тактового генератора 53.

Формула изобретения

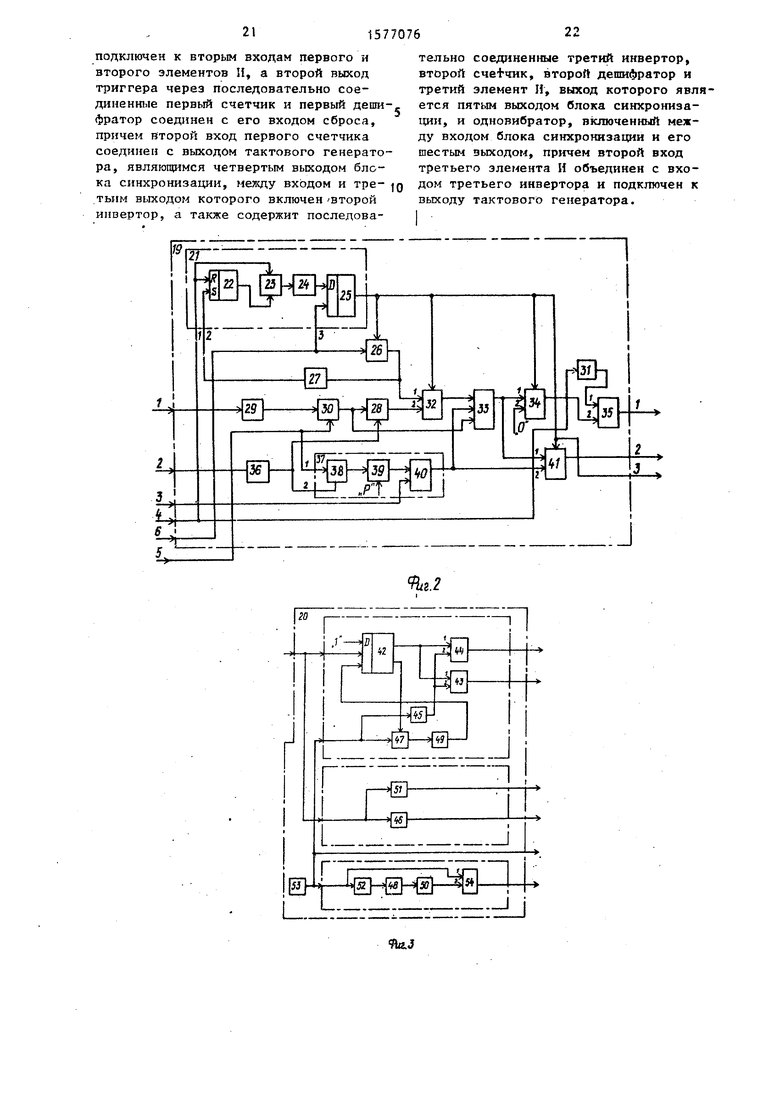

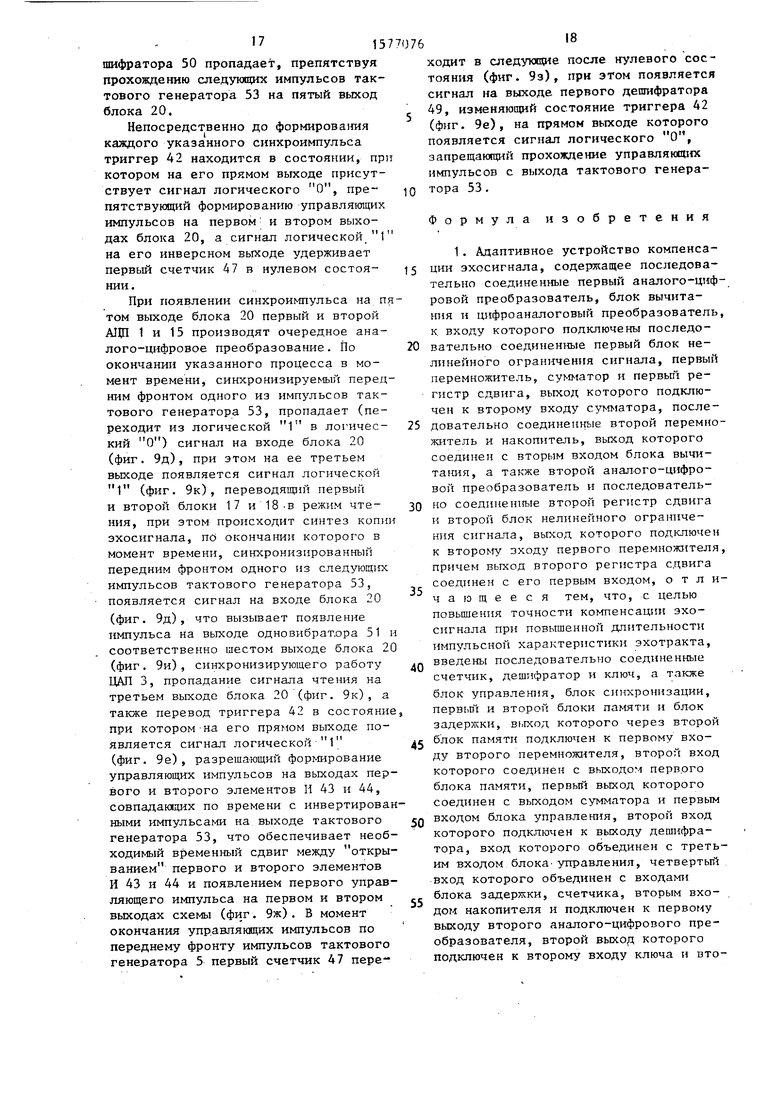

1. Адаптивное устройство компенсации эхосигнала, содержащее последовательно соединенные первый аналого-цифровой преобразователь, блок вычитания и цифроаналоговый преобразователь, к входу которого подключены последовательно соединенные первый блок нелинейного ограничения сигнала, первый перемножитель, сумматор и первый регистр сдвига, выход которого подключен к второму входу сумматора, последовательно соединенные второй перемножитель и накопитель, выход которого соединен с вторым входом блока вычитания, а также второй аналого-цифровой преобразователь и последовательно соединенные второй регистр сдвига и второй блок нелинейного ограничения сигнала, выход которого подключен к второму зходу первого перемножителя, причем выход второго регистра сдвига соединен с его первым входом, отличающееся тем, что, с целью повышения точности компенсации эхо- сигнала при повышенной длительности импульсной характеристики эхотракта, введены последовательно соединенные счетчик, дешифратор и ключ, а также блок управления, блок синхронизации, первый и второй блоки памяти и блок задержки, выход которого через второй блок памяти подключен к первому входу второго перемножителя, второй вход которого соединен с выходом первого блока памяти, первый выход которого соединен с выходом сумматора и первым входом блока управления, второй вход которого подключен к выходу дешифратора, вход которого объединен с третьим входом блока- управления, четвертый вход которого объединен с входами блока задержки, счетчика, вторым входом накопителя и подключен к первому выходу второго аналого-цифрового преобразователя, второй выход которого подключен к второму входу ключа и второму входу второго блока памяти, первый вход которого объединен с третьим входом ключа, первый и второй выходы которого подключены к соответствующим второму и третьему входам второго регистра сдвига, синхронизирующий вход которого соединен с первым выходом блока синхронизации, второй вход которого подключен к пятому входу блока управления и синхронизирующим входам первого регистра сдвига и первого блока памяти, второй вход которого подключен к первому выходу блока управ

рого коммутатора, причем третий вход блока памяти объединен с первым входом второго счетчика, второй вход которого подключен к выходу формирователя импульсов, вход порогового блока является первым входом блока управления, вторым входом которого является вход формирователя импульсов, второй вход формирователя номера импульсных коэффициентов является третьим входом блока управления, четвертым входом которого являются объединенные третий вход блока установки

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Цифровой фильтр | 1990 |

|

SU1730718A1 |

| Устройство для вычисления полиномов | 1989 |

|

SU1674112A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

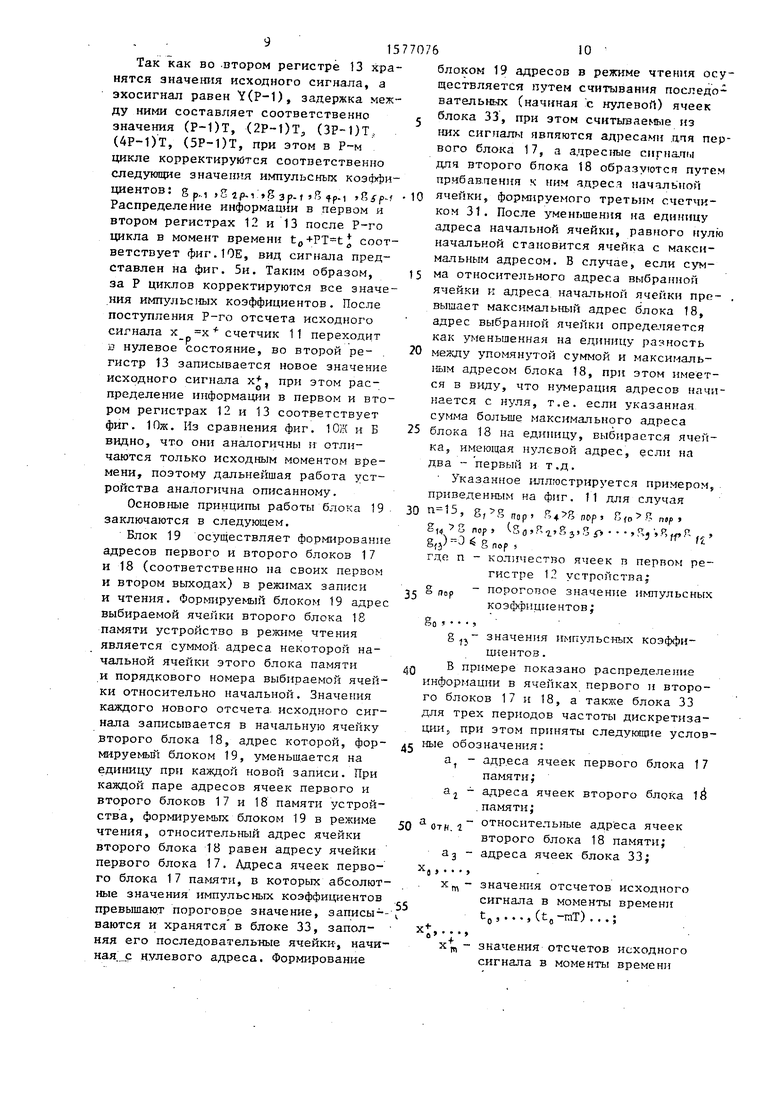

Изобретение относится к технике громкоговорящей телефонной связи. Цель - повышение точности компенсации эхосигнала при повышенной длительности импульсной характеристики эхотракта. Компенсация эхосигнала производится в блоке 2 вычитания, на который подается оцифрованный сигнал с выхода первого аналого-цифрового преобразователя 1 и компенсирующий сигнал с выхода второго аналого-цифрового преобразователя 15. Формирование компенсирующего сигнала производится в три фазы: запоминание исходного компенсирующего сигнала в регистре 13 сдвига и втором блоке 18 памяти

синтез копии эхосигнала с учетом предыдущих его значений путем считывания информации из первого и второго блоков 17 и 18 памяти с соответствующими коэффициентами, вводимыми в сумматор 9 и первый и второй перемножители 5 и 6, и коррекция импульсных коэффициентов, записанных в первый блок 17 памяти. Управление фазами коррекции производится блоком 19 управления и блоком 20 синхронизации. 3 з.п. ф-лы, 1 осн., 2 доп.11 ил.

легшя, второй выход которого подключенjj режима и вход третьего счетчика, обък третьему входу второго блока памяти, четвертый вход которого объединен с третьим входом первого блока памяти и подключен к третьему выходу блока синхронизации, четвертый выход которого подключен к шестому входу блока управления, третий выход которого со- П лнен с входом блока синхронизации, пятый выход которого соединен с син- -- .визирующими входами первого и вто- jjoro аналого-цифровых преобразователей, а шестой выход блока синхронизации соединен с сннхрони- мфуюцим входом цифроаналогового образователя.

-в- j,H которого подключен к первым входам первого счетчика, первого, второго и третьего коммутаторов, вторые входы второго и третьего из которых объединены и подключены-к выходу блока памяти, первый вход которого под- ключей к выходу первого коммутатора, второй вход которого соединен с выходом первого счетчика и входом дешифратора, выход которого соединен с первым входом блока установки релшма, второй вход которого объединен с вторым входом первого счетчика, а также последовательно соединенные пороговый блок, ключ и второй счетчик, выход которого подключен к третьему входу первого коммутатора, последовательно соединенные формирователь импульсов и формирователь номера импульсных коэффициентов, выход которого подключен к второму входу блока памяти и третьему входу третьего ком- му атора, последовательно соединенные ретий счетчик и сумматор, второй од которого соединен с выходом вто20

25

30

35

40

45

50

55

единенные второй вход ключа и третий вход формирователя номера импульсных коэффициентов являются пятым входом блока управления, шестым входом которого являются объединенные второй вход блока установки режима и второй вход первого счетчика, первый вход КОТОРОГО соединен с третьим выходом блока управления, первым и вторым выходами которого являются соответственно выход третьего коммутатора и выход первого сумматора, при этом блок установки режима содержит последовательно соединенные RS-триггер, элемент ИЛИ, блок задержки и D-триггер, другой вход и выход которого являются соответственно вторым входом и выходом блока установки режима, первым входом которого является 5-вход RS-триггера, R-вход которого, объединенный с вторым входом элемента ИЛИ, является третьим входом блока установки режима, а формирователь номера импульсных коэффициентов содержит последовательно соединенные четвертый счетчик, перемножитель и второй сумматор, выход которого является выходом формирователя номера импульсных коэффициентов, первым и третьим входами которого являются соответственно первый и второй входы четвертого счетчика, а второй вход второго сумматора является вторым входом формирователя номера импульсных коэффициентов .

к первым входам первого и второго элементов И, выходы которых являются первым и вторым выходами блока синхронизации, входом которого является вход триггера, пер зьп выход которого

5

0

5

0

5

0

5

единенные второй вход ключа и третий вход формирователя номера импульсных коэффициентов являются пятым входом блока управления, шестым входом которого являются объединенные второй вход блока установки режима и второй вход первого счетчика, первый вход КОТОРОГО соединен с третьим выходом блока управления, первым и вторым выходами которого являются соответственно выход третьего коммутатора и выход первого сумматора, при этом блок установки режима содержит последовательно соединенные RS-триггер, элемент ИЛИ, блок задержки и D-триггер, другой вход и выход которого являются соответственно вторым входом и выходом блока установки режима, первым входом которого является 5-вход RS-триггера, R-вход которого, объединенный с вторым входом элемента ИЛИ, является третьим входом блока установки режима, а формирователь номера импульсных коэффициентов содержит последовательно соединенные четвертый счетчик, перемножитель и второй сумматор, выход которого является выходом формирователя номера импульсных коэффициентов, первым и третьим входами которого являются соответственно первый и второй входы четвертого счетчика, а второй вход второго сумматора является вторым входом формирователя номера импульсных коэффициентов .

к первым входам первого и второго элементов И, выходы которых являются первым и вторым выходами блока синхронизации, входом которого является вход триггера, пер зьп выход которого

5

подключен к вторым входам первого и второго элементов И, а второй выход триггера через последовательно соединенные первый счетчик и первый дешифратор соединен с его входом сброса, причем второй вход первого счетчика соединен с выходом тактового генератора, являющимся четвертым выходом блока синхронизации, между входом и тре- JQ тьим выходом которого включен Второй инвертор, а также содержит последова

тельно соединенные третий инвертор, второй счетчик, второй дешифратор и третий элемент И, выход которого является пятым выходом блока синхронизации, и одновибратор, включенный между входом блока синхронизации и его шестым выходом, причем второй вход третьего элемента И объединен с входом третьего инвертора и подключен к выходу тактового генератора.

Л

7 f Ж 9

9

9

.ши$1

а

Вход

г д

е

ж

kUk,x27

-чW

tЈl Ць

f№

%.й

-л,

I 1-101

%,,-#.

Ж

мгт

ч

Ж

-я

-ч

ж i

Г

тч

i м™

t-ri

ja

7J

с

гШ

l i i iWI

и,

tut. 9

ВГ&

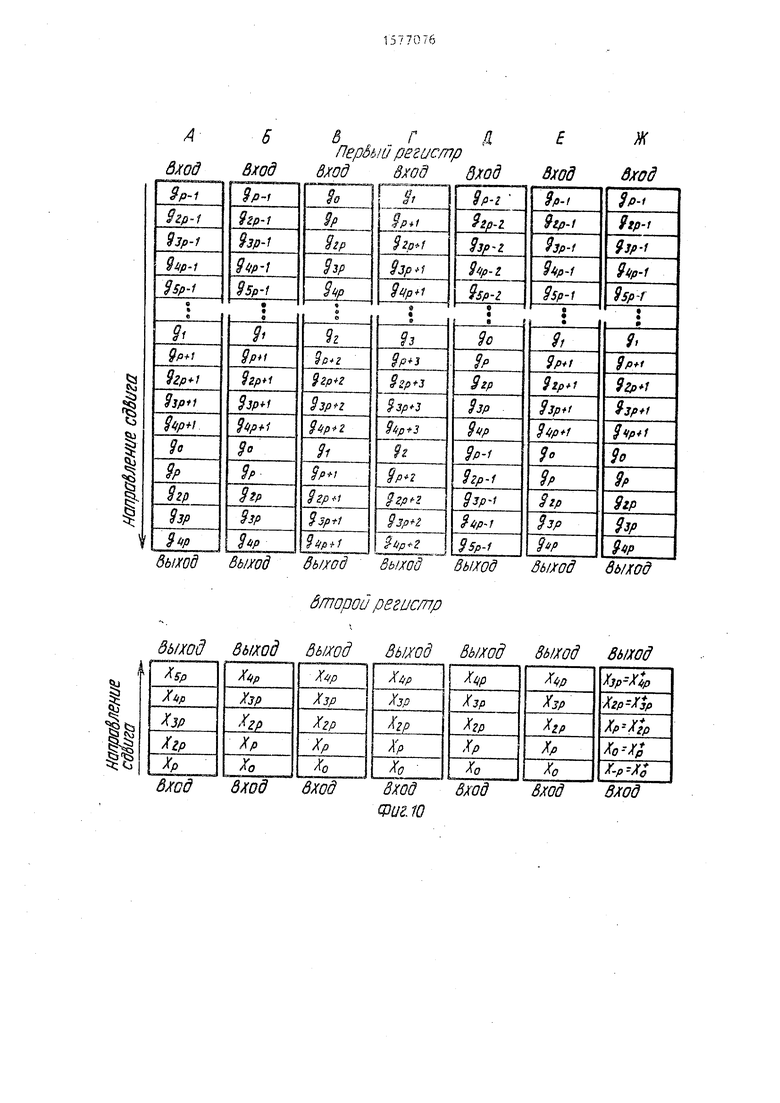

Пер&ый регистр

Вход Вход вход

выход Выход выход Выход Выход Выход выход

второй регистр

Выход выход Выход Выход Выход Выход выход

1

I

fe&

Вход Вход вход

Вход

Ж вход

Вход Вход Фиг. ю

Вход

вход

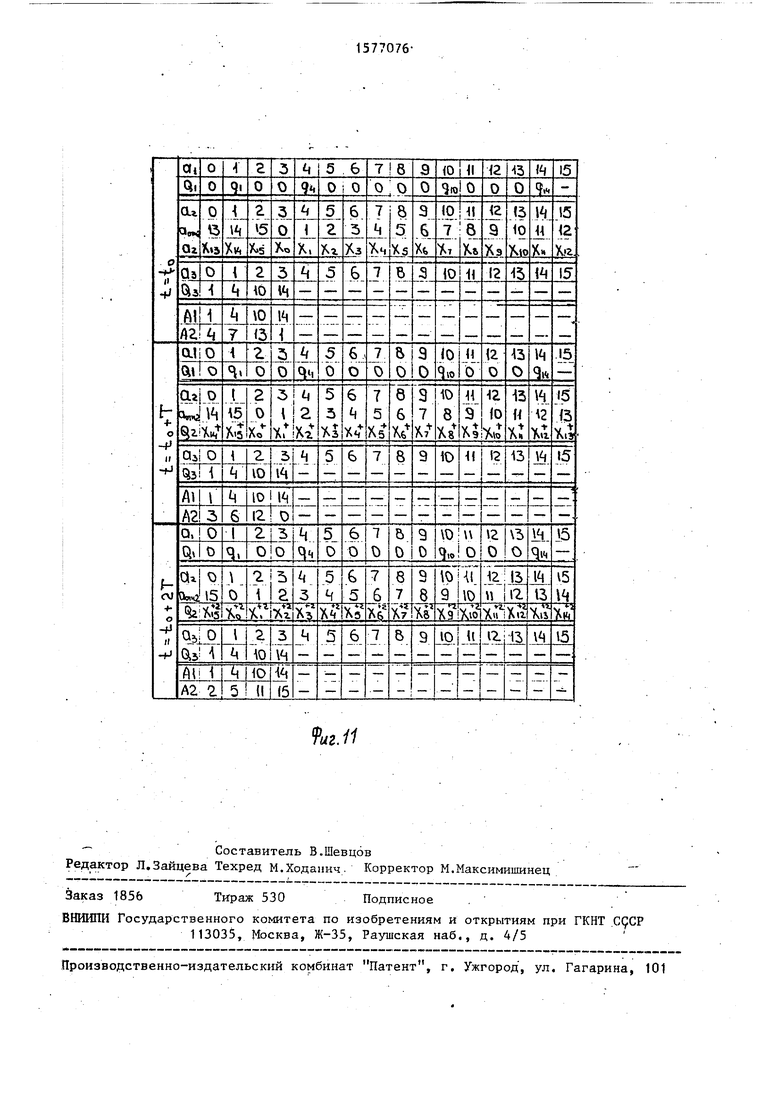

Чиг.11

Составитель В.Шевцов

Редактор Л.Зайцева Техред М.Ходаиич Корректор М.Максимишинец

Заказ 1856

Тираж 530

ВНИИГШ Государственного комитета по изобретениям и открытиям при ГКНТ 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Analysis of an Adaptive impulse response echo conceller | |||

| - COMSAT Texnieal Revive, 1972, v.2, N 1. |

Авторы

Даты

1990-07-07—Публикация

1988-03-31—Подача