Изобретение относится к вычислительной технике и может быть использовано при построении радиолокаторов с синтезированной апертурой антенны (РСА) и цифровой обработкой информации в реальном масштабе времени на борту носителя РСА при жест ких ограничениях на энергопотребление.

Цель изобретения - упрощениеустройства путем сокращения количества .

умножителей, реализующих параллельно выполняемые операции умножения при вычислении оценки взаимной корреляционной функции опорног5 и при- ня то го сигнале в.

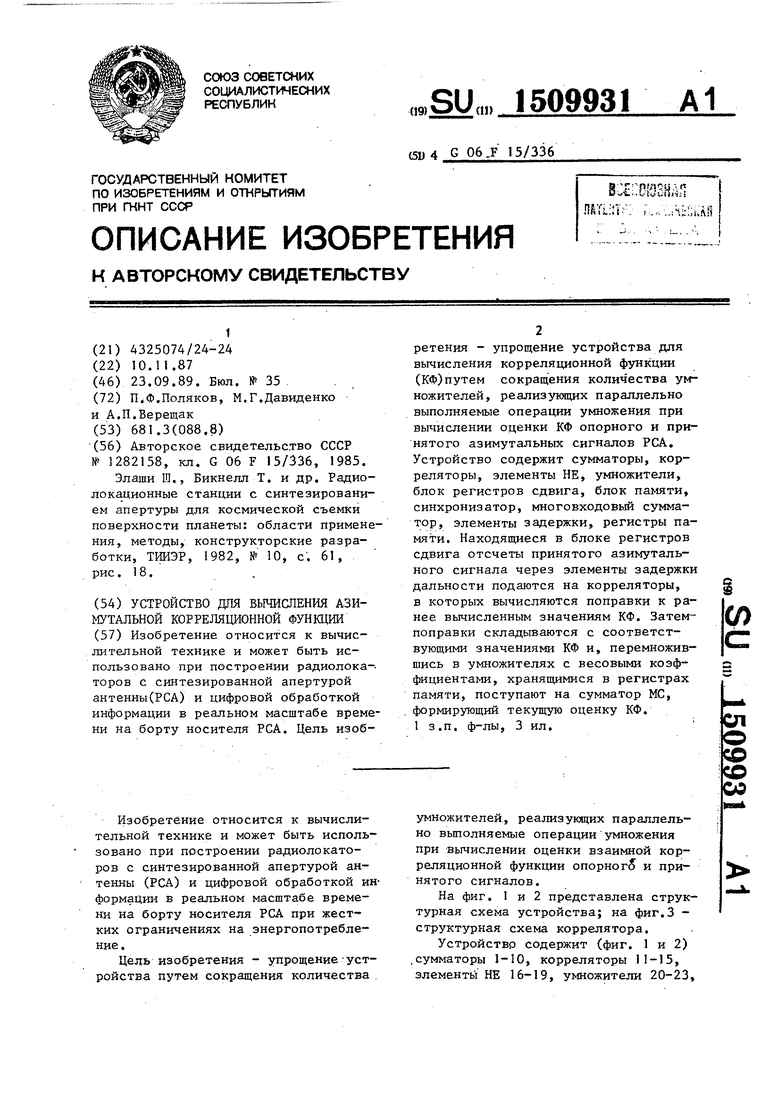

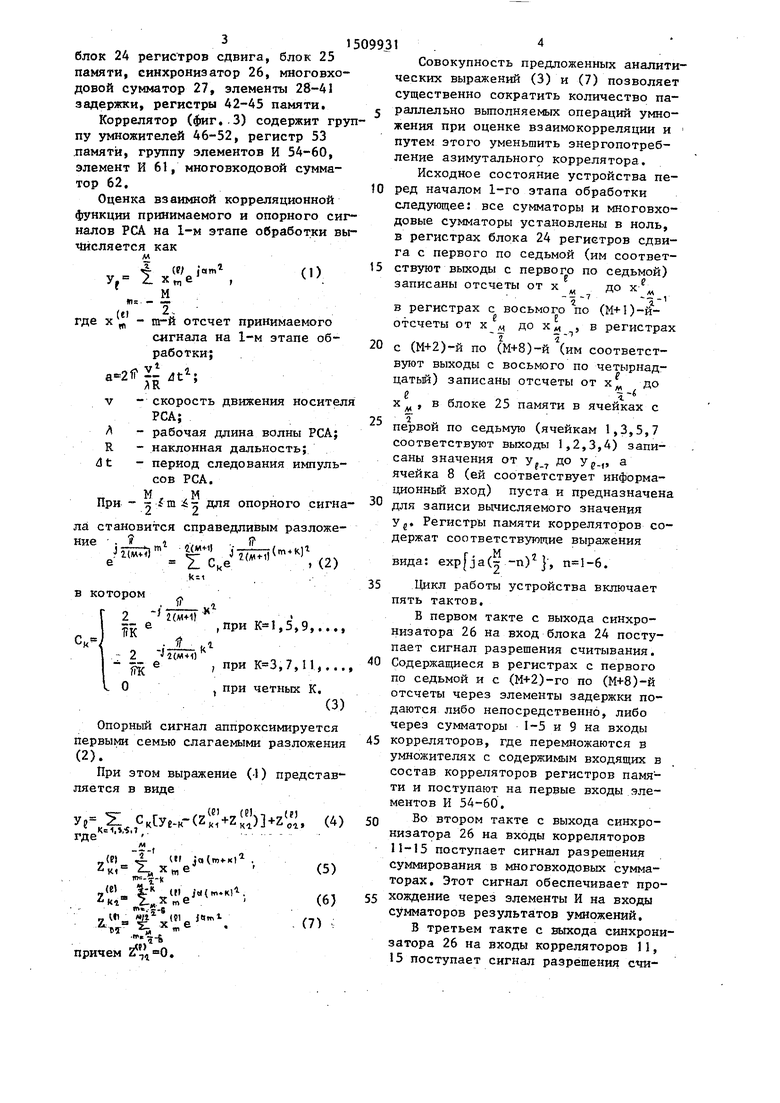

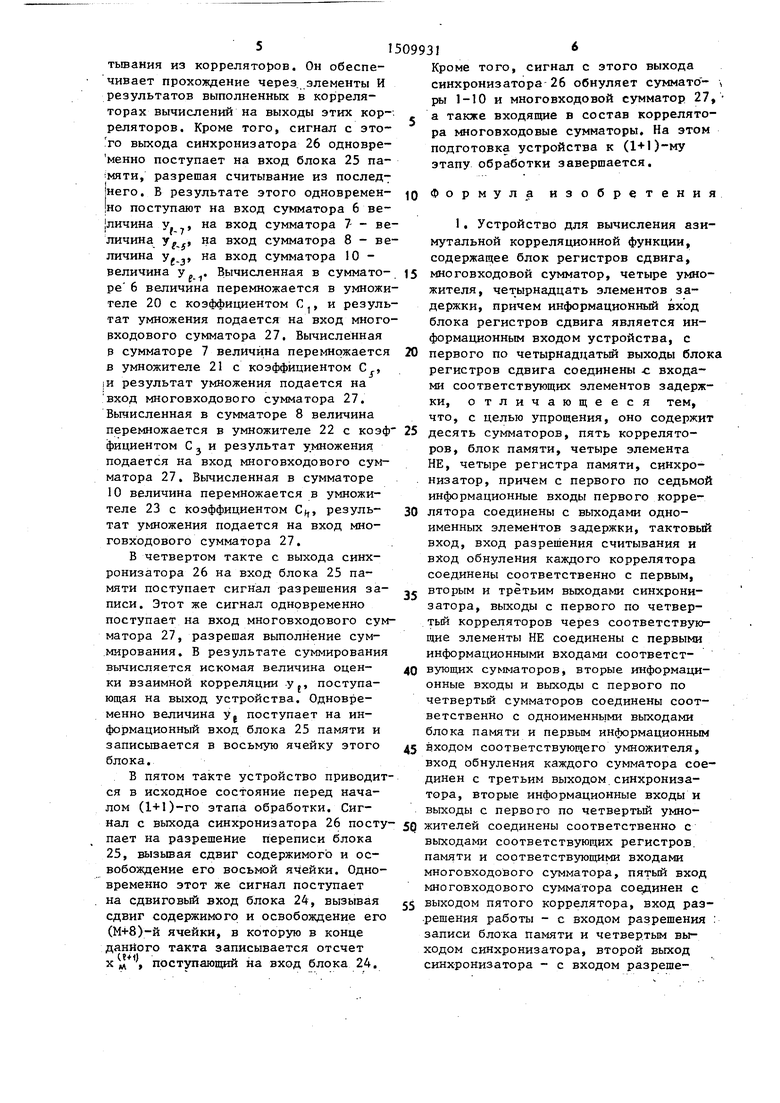

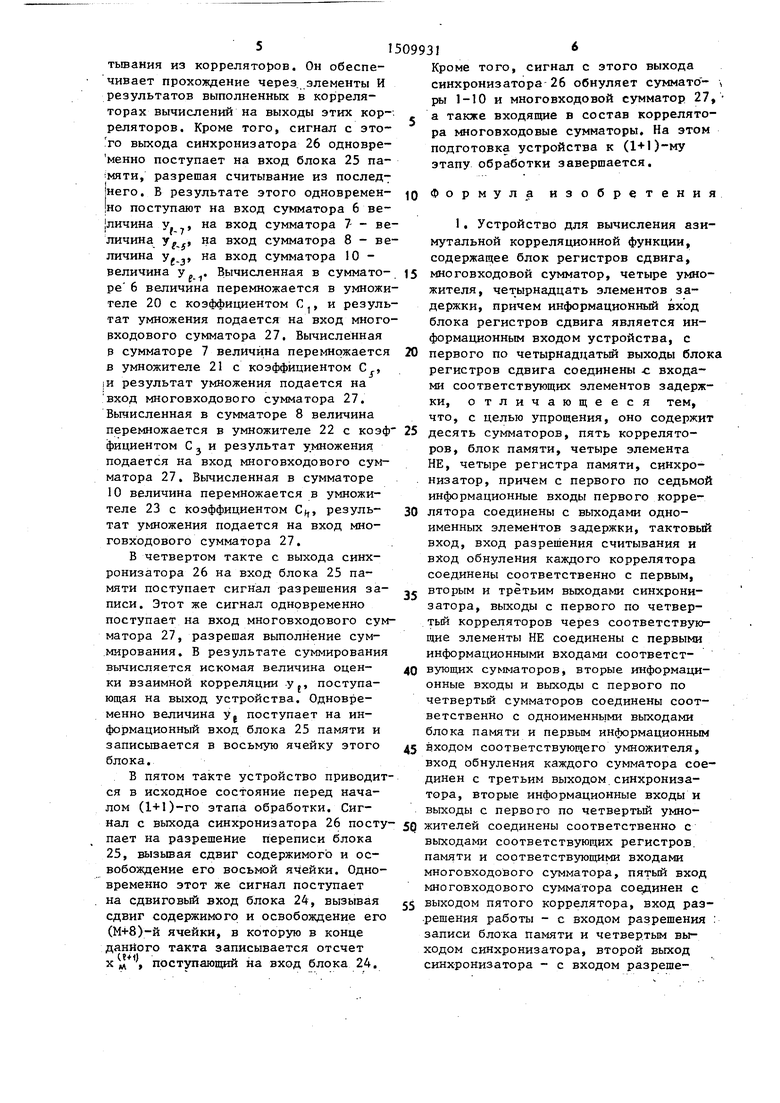

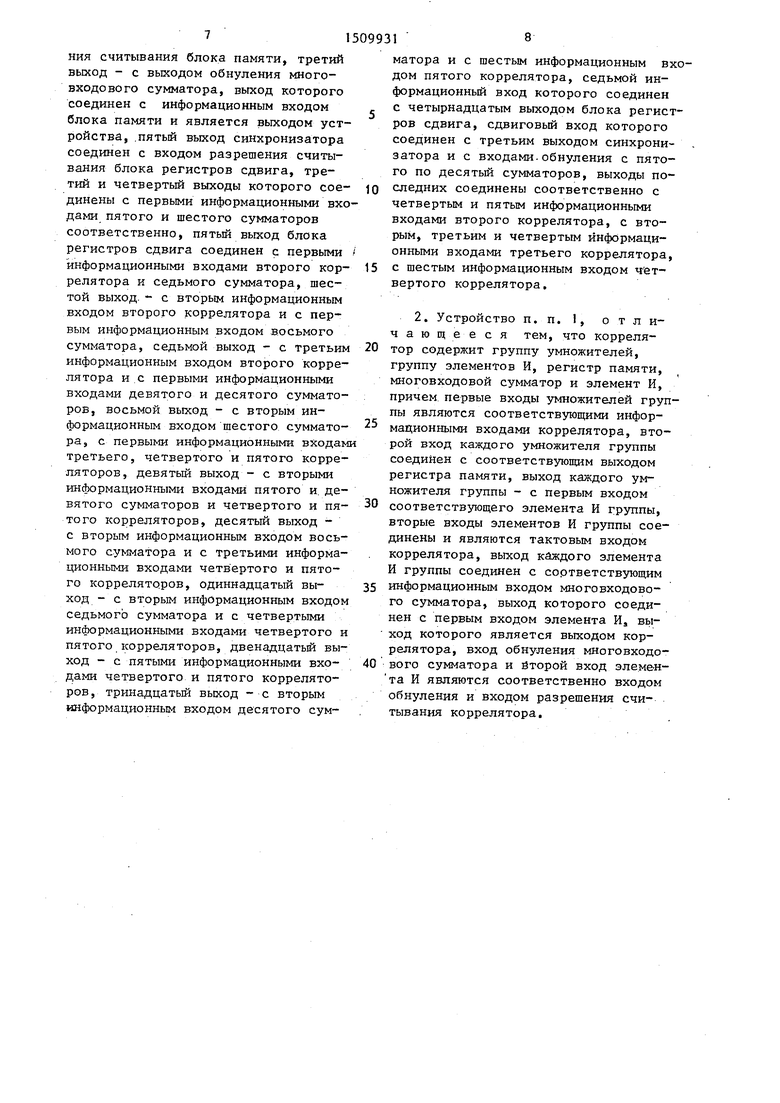

На фиг. 1 и 2 представлена структурная схема устройства; на фиг.З - структурная схема коррелятора.

Устройство содержит (фиг. 1 и 2) .сумматоры 1-10, корреляторы 11-15, элементы НЕ 16-19, умножители 20-23,

31509931

блок 24 регистров сдвига, блок 25 памяти, еинхрониэатор 26, многовхо- довой сумматор 27, элементы 28-41 задержки, регистры 42-45 памяти, ,

Коррелятор (фиг..З) содержит группу умножителей 46-52, регистр 53 .памяти, группу элементов И 54-60, элемент И 61, многовкодовой сумматор 62,10

Оценка взаимной корреляционной функции принимаемого и опорного сигналов РСА на 1-м этапе обработки выt5 с

яется как

м т

е

W jam 2. х„е

m

(1)

М 1.

X - т-й отсчет принимаемого сигнала на 1-м этапе обработки;

a.2f- .tS

е1-

X , в блоке 25 памяти в ячейках с

Л

R

ut

При

- период следования импульсов РСА,

ММ

- для опорного сигна30

ла становится справедливым разложение

в котором

,, (2)

)

г , -М , 2 )1 /

вида: exp|ja(2 -п) , .

f

с«2 2(Mi-it К

,при ,5,9,,,,,

1f

2

т L о

: If ,Л

VKW+D

, при ,7,I1,...,

при четных К,

(3)

.(f)

(е)

причем

-скорость движения носителя

Р С А 7 i 2

т, первой по седьмую (ячейкам 1,3,5,7

-рабочая длина волны РСА;ior /

соответствуют выходы 1,2,3,4) запи-наклонная дальность;

саны значения от у до Ур.„ а

ячейка 8 (ей соответствует информа- ционньй вход) пуста и предназначена для записи вычисляемого значения у. Регистры памяти корреляторов содержат соответствующие выражения ,М 2

35 Цикл работы устройства включает пять тактов.

В первом такте с выхода синхронизатора 26 на вход блока 24 поступает сигнал разрешения считывания.

40 Содержащиеся в регистрах с первого по седьмой и с (М+2)-го по (М+8)-й отсчеты через элементы задержки подаются либо непосредственно, либо через сумматоры 1-5 и 9 на входы

45 корреляторов, где перемножаются в умножителях с содержимым входящих в состав корреляторов регистров памяти и поступают на первые входы элементов И 54-60.

Во втором такте с выхода синхронизатора 26 на входы корреляторов П-15 поступает сигнал разрешения суммирования в многовходовых сумматорах. Этот сигнал обеспечивает про55 хождение через элементы И на входы сумматоров результатов умножений.

В третьем такте с выхода синхронизатора 26 на входы корреляторов 11, 15 поступает сигнал разрешения счиОпорный сигнал аппроксимируется первыми семью слагаемыми разложения (2),

При этом выражение (-1) представляется в виде

Уе 51 с,уе-к-(), (4)

где

50

-Г Хмв(П ja()

-и м

т«-Й-х

Ь lei j«(. ki- l.x«eV

m«.5.e

ylti

tf j .№.7(0

1

(5) (6)

(7) :

0.

Совокупность предложенных аналитических выражений (3) и (7) позволяет существенно сократить количество параллельно выполняемых операций умножения при оценке взаимокорреляции и путем этого уменьшить энергопотребление азимутального коррелятора.

Исходное состояние устройства перед началом 1-го этапа обработки следующее: все сумматоры и многовхо- довые сумматоры установлены в ноль, в регистрах блока 24 регистров сдвига с первого по седьмой (им соответ- ствуют выходы с первого по седьмой) записаны отсчеты от х , до

1-1 в регистрах с восьмого по (М+1)-йС Е отсчеты от X л, до Хм в регистрах

Т

с (М+2)-й по (М+8)-й (им соответствуют выходы с восьмого по четырнад- цатьй) записаны отсчеты от х „ до

е1-

X , в блоке 25 памяти в ячейках с

г , -М , 2 )1 /

вида: exp|ja(2 -п) , .

ячейка 8 (ей соответствует ин ционньй вход) пуста и предна для записи вычисляемого значе у. Регистры памяти коррелято держат соответствующие выраже ,М 2

тьшания из корреляторов. Он обеспечивает прохождение через элементы И результатов выполненных в корреляторах вычислений на выходы этих кор-. реляторов. Кроме того, сигнал с это- го выхода синхронизатора 26 одновре- менно поступает на вход блока 25 па- мяти, разрешая считывание из последу него. В результате этого одновременно поступают на вход сумматора 6 ве- |личина у. , на вход сумматора 7 - величина у, на вход сумматора 8 - величина у ,, на вход сумматора 10 Кроме того, сигнал с этого выхода синхронизатора 26 обнуляет суммато - ры 1-10 и многовходовой сумматор 27,- е а также входящие в состав коррелятора многовходовые сумматоры. На этом подготовка устройства к ()-му этапу обработки завершается.

0 формула изобретения

1. Устройство для вычисления азимутальной корреляционной функции, содержащее блок регистров сдвига,

величина у. Вычисленная в суммато- 15 многовходовой сумматор, четыре умножителя, четырнадцать элементов задержки, причем информационньй вход блока регистров сдвига является информационным входом устройства, с 20 первого по четырнадцатый выходы блока регистров сдвига соединены -с входами соответствующих элементов задержки, о тличающееся тем, что, с целью упрощения, оно содержит

-

ре 6 величина перемножается в умножителе 20 с коэффициентом С., и результат умножения подается на вход много- рходового сумматора 27, Вычисленная Э сумматоре 7 величина перемножается в умножителе 21 с коэффициентом С , |И результат умножения подается на вход многовходового сумматора 27, Вьгаисленная в сумматоре 8 величина

перемножается в умножителе 22 с коэф 25 десять сумматоров, пять коррелято- фициентом С j и результат умножения подается на вход многовходового сумматора 27. Вычисленная в сумматоре 10 величина перемножается в умножителе 23 с коэффициентом С,, результат умножения подается на вход многовходового сумматора 27.

В четвертом такте с выхода синхронизатора 26 на вход блока 25 паров, блок памяти, четыре элемента НЕ, четыре регистра памяти, синхро- . низатор, причем с первого по седьмой

информационные входы первого корре- 30 лятора соединены с выходами одноименных элементов задержки, тактовый вход, вход разрешения считывания и вход обнуления каждого коррелятора соединены соответственио с первым.

Кроме того, сигнал с этого выхода синхронизатора 26 обнуляет суммато - ры 1-10 и многовходовой сумматор 27,- а также входящие в состав коррелятора многовходовые сумматоры. На этом подготовка устройства к ()-му этапу обработки завершается.

формула изобретения

1. Устройство для вычисления азимутальной корреляционной функции, содержащее блок регистров сдвига,

десять сумматоров, пять коррелято-

ров, блок памяти, четыре элемента НЕ, четыре регистра памяти, синхро- низатор, причем с первого по седьмой

информационные входы первого корре- лятора соединены с выходами одноименных элементов задержки, тактовый вход, вход разрешения считывания и вход обнуления каждого коррелятора соединены соответственио с первым.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Генератор случайных чисел | 1988 |

|

SU1531094A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1727134A1 |

| Цифровой коррелятор | 1984 |

|

SU1275467A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении радиолокаторов с синтезированной апертурой антенны (РСА) и цифровой обработкой информации в реальном масштабе времени на борту носителя РСА. Цель изобретения - упрощение устройства для вычисления корреляционной функции (КФ) путем сокращения количества умножителей, реализующих параллельно выполняемые операции умножения при вычислении оценки КФ опорного и принятого азимутальных сигналов РСА. Устройство содержит сумматоры, корреляторы, элементы НЕ, умножители, блок регистров сдвига, блок памяти, синхронизатор, многовходовый сумматор, элементы задержки и регистры памяти. Находящиеся в блоке регистров сдвига отсчеты принятого азимутального сигнала через элементы задержки дальности подаются на корреляторы, в которых вычисляются поправки к ранее вычисленным значениям КФ. Затем поправки складываются с соответствующими значениями КФ и, перемножившись в умножителях с весовыми коэффициентами, хранящимися в регистрах памяти, поступают на сумматор формирующий текущую оценку КФ. 1 о.п. и 1 з.п. ф-лы, 2 ил.

мяти поступает сигнал разрешения за- , вторым и третьим выходами синхрони- писи. Этот же сигнал одновременно затора, выходы с первого по четвер- поступает на вход многовходового сум- тьй корреляторов через соответствую- матора 27, разрешая выполнение суммирования, В результате суммирования

щие элементы НЕ соединены с первыми информационными входами соответствычисляется искомая величина оценки взаимной корреляции у., поступающая на выход устройства. Одновременно величина у поступает на информационный вход блока 25 памяти и записывается в восьмую ячейку этого блока,

В пятом такте устройство приводися в исходное состояние перед началом (1+1)-го этапа обработки, Сигнал с выхода синхронизатора 26 посту- 5Q жителей соединены соответственно с пает на разрешение переписи блока 25, вызьшая сдвиг содержимого и освобождение его восьмой ячейки. Одновременно этот же сигнал поступает на сдвиговый БХОД блока 24, вызывая сдвиг содержимого и освобождение его (М+8)-й ячейки, в которую в конце данного такта записывается отсчет

X

J , поступающий на вход блока 24,

выходами соответствующих регистров. памяти и соответствующими входами многовходового сумматора, пятый вхо многовходового сумматора с 55 выходом пятого коррелятора, вход ра .решения работы - с входом разрешени записи бло ка памяти и четвертым выходом синхронизатора, второй выход синхронизатора - с входом разрешевторым и третьим выходами синхрони- затора, выходы с первого по четвер- тьй корреляторов через соответствую-

щие элементы НЕ соединены с первыми информационными входами соответствующих сумматоров, вторые информационные входы и выходы с первого по четвертый сумматоров соединены соответственно с одноименными выходами блока памяти и первым информационным

входом соответствующего умножителя, вход обнуления каждого сумматора соединен с третьим выходом.синхронизатора, вторые информационные входы и выходы с первого по четвертый умножителей соединены соответственно с

выходами соответствующих регистров. памяти и соответствующими входами многовходового сумматора, пятый вход многовходового сумматора с выходом пятого коррелятора, вход раз- решения работы - с входом разрешения : записи бло ка памяти и четвертым выодом синхронизатора, второй выход синхронизатора - с входом разрешения считывания блока памяти, третий выход - с выходом обнуления много- входового сумматора., выход которого соединен с информационным входом блока памяти и является выходом устройства, .пятый выход синхронизатора соединен с входом разрешения считывания блока регистров сдвига, третий и четвертьй выходы которого соединены с первыми информационными входами пятого и шестого сумматоров соответственно, пятый выход блока регистров сдвига соединен с первыми информационными входами второго коррелятора и седьмого сумматора, шестой выход. - с вторым информационным входом второго коррелятора и с первым информационным входом восьмого сумматора, седьмой выход - с третьим информационным входом второго коррелятора и с первыми информационными входами девятого и десятого сумматоров, восьмой выход - с вторым ин- формационньш входом шестого сумматора, с первыми информационными входам третьего, четвертого и пятого корреляторов, девятый выход - с вторыми информационными входами пятого и. девятого сумматоров и четвертого и пятого корреляторов, десятьй выход - с вторым информационным входом восьмого сумматора и с третьими информационными входами четв ертого и пятого корреляторов, одиннадцатый выход - с вторым информационным входом седьмого сумматора и с четвертыми информационными входами четвертого и пятого корреляторов, двенадцатый выход - с пятыми информационными входами четвертого и пятого корреляторов , тринадцатый выход - с вторым информационным входом десятого сум99318

матора и с шестым информационным входом пятого коррелятора, седьмой информационный вход которого соединен с четырнадцатым выходом блока регистров сдвига, сдвиговый вход которого соединен с третьим выходом синхронизатора и с входами.обнуления с пятого по десятый сумматоров, выходы по10 следних соединены соответственно с четвертым и пятым информациоиньми входами второго коррелятора, с вторым, третьим и четвертым информационными входами третьего коррелятора,

15 с шестым информационным входом ч ет- вертого коррелятора.

0

5

5

0

Но Лг. 8л. IS

Кобх. 5ff.n

Фиг.1

.5л.П

,f(.S/J.ff

5хоУ

KoSx.1611.27

Но SxMlB

ж /{8t,ix.5 Sfl.26, Ко fx. 5л. 19

Кбьа.бй. 15

Вып. дстраисгпба

35 7ш/лод

| Цифровой коррелятор | 1985 |

|

SU1282158A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Элаши Ш., Бикнелл Т | |||

| и др | |||

| Радиолокационные станции с синтезированием апертуры для космической съемки поверхности планеты: области применения, методы, конструкторские разработки, ТШЭР, 1982, № 10, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1989-09-23—Публикация

1987-11-10—Подача