Изобретение относится к вычислительной технике, преимущественно к анализу формы сигналов, и может быть использовано для построения цифровых корреляторов; определяющих оценку монотонной корреляции двух сигналов.

Цель изобретения - расширение класса решаемых задач за счет обеспечение возможности оценки монотонной корреляции сигналов.

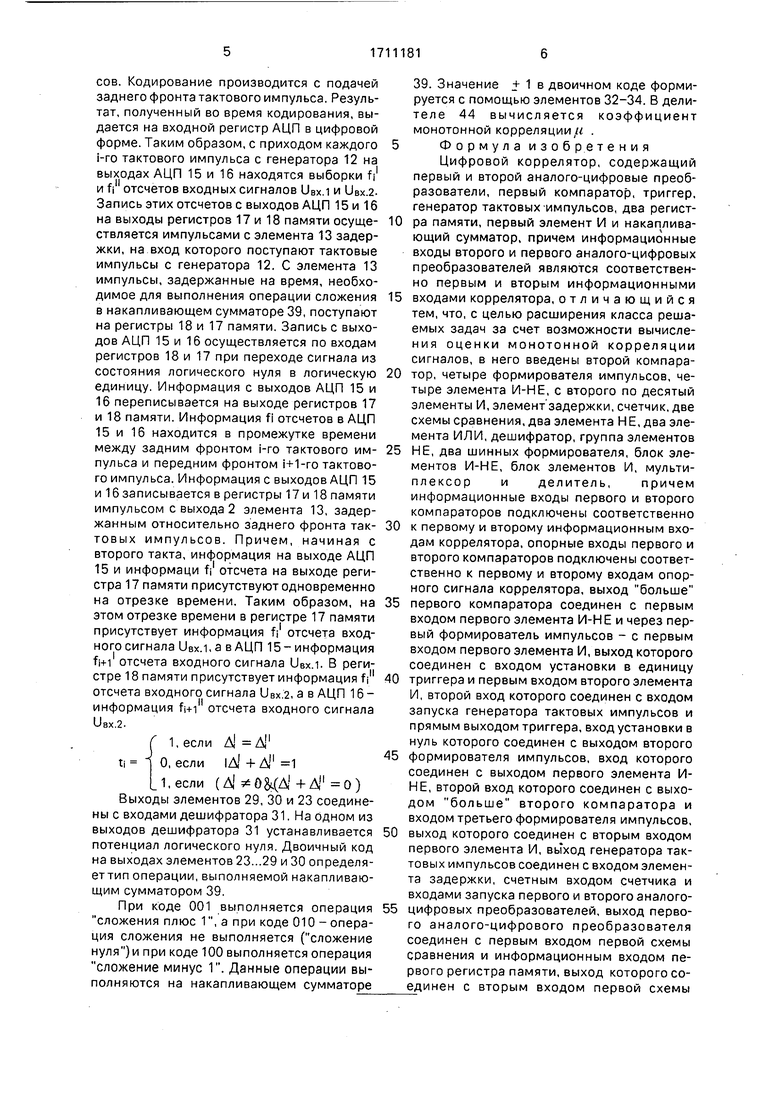

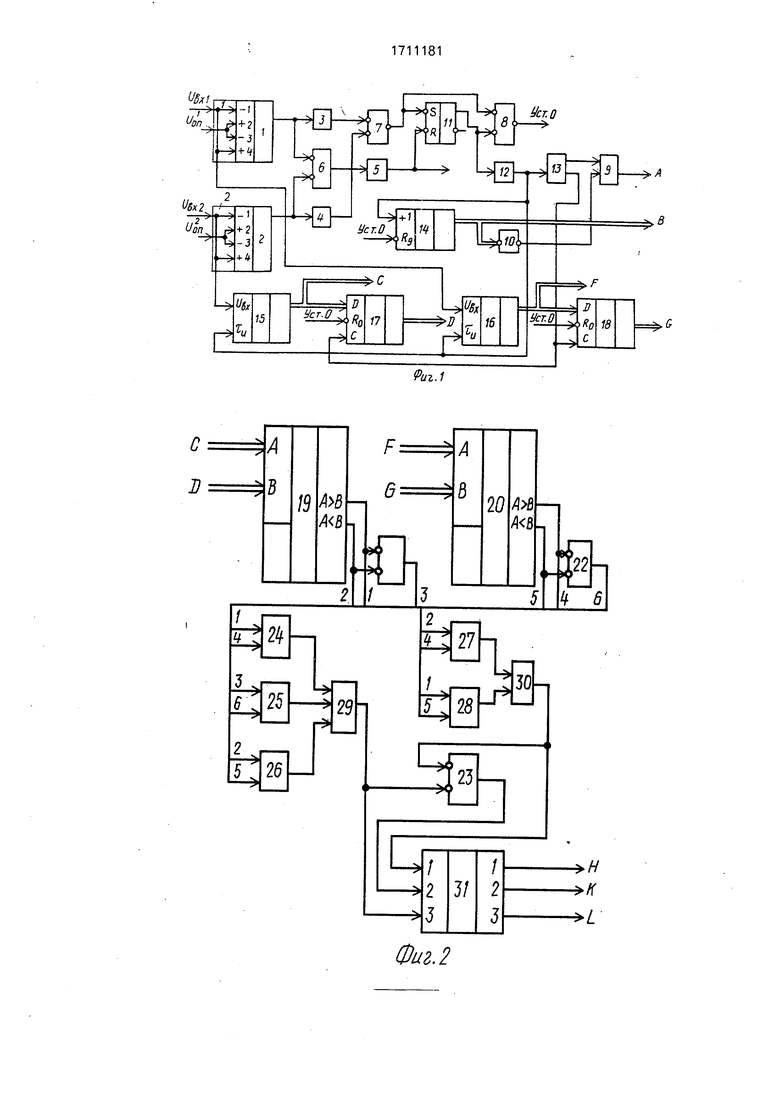

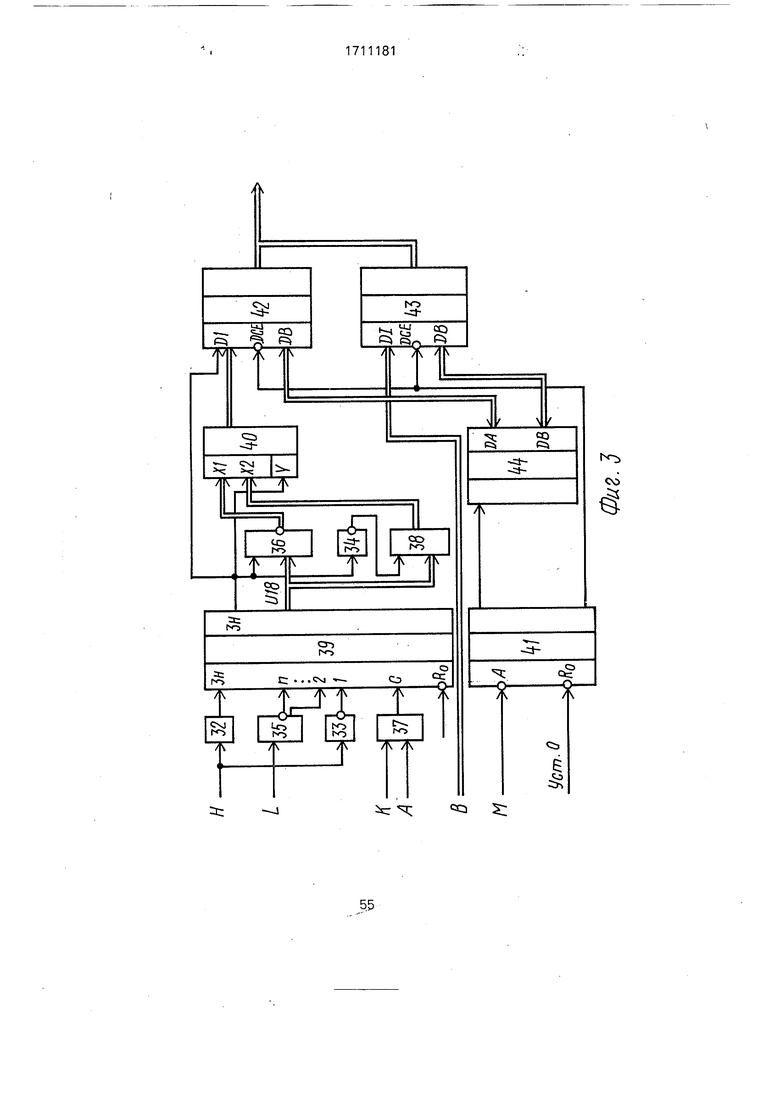

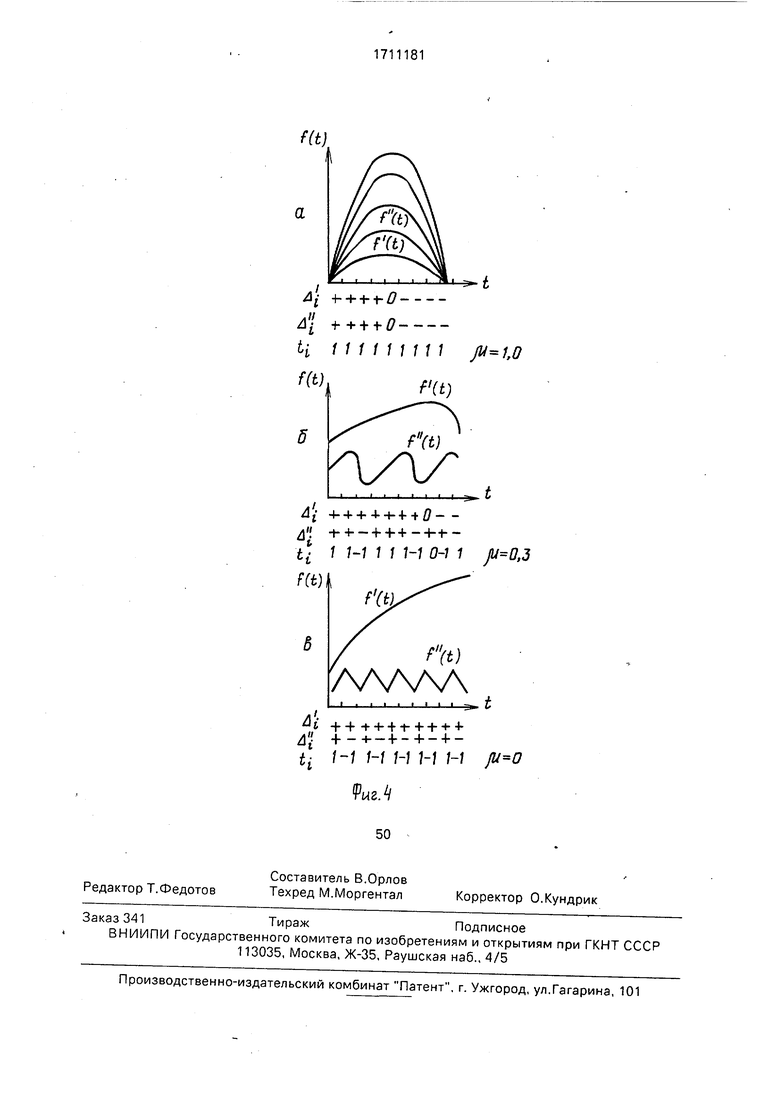

На фиг. 1-3 приведена структурная схема коррелятора; на фиг. 4 приведены формы сигналов и значения коэффициентов монотонной корреляции.

Коррелятор содержит компараторы 1 и 2, формирователи 3-5 импульсов, элемент И-Н Е 6, элементы И 7-9, элемент И 10, триггер 11, генератор 12 тактовых импульсов, элемент 13 задержки, счетчик 14, аналого- цифровые преобразователи 15 и 16, регистры 17 и 18 памяти, схемы 19 и 20 сравнения, элементы И-НЕ 21-23, элементы И 24-28, элементы ИЛИ 29 и 30, дешифратор 31, буферный элемент 32, элементы НЕ 33 и 34. группу элементов НЕ 35, блок элементов И-Н Е 36, элемент И 37, блок элементов И 38, накапливающий сумматор 39, мультиплексор 40, формирователь 41 импульсов, шинные формирователи 42 и 43, делитель 44.

При определении монотонной корреляции используют факт совпадения или несовпадения тенденции изменения двух сигналов в i+1-й момент времени по отношению к i-му моменту. Если знаки Д , Л их изменения совпадают, коэффициент/г монотонной корреляции получает один голос

за (ti 1), если знаки Д , Д 1 противоположны, fi получает один голос против (ti -1). В ситуации, когда знак изменения одно00

го сигнала нулевой, а знак изменения другого - ненулевой, воздерживаются от голосования (ti 0). Определяют указанные знаки для всех i 1, N-1 отрчетов сигналов (кроме N-ro, для которого не определен N+1- й отсчет). Вычислив сумму голосов и ее отношение к числу голосов, получаем коэффициент монотонной корреляции. Легко убедиться, что если между сигналами имеется прямо (или обратно) пропорциональная зависимость (коэффициенты линейной корреляции между ними соответственно 1 и -1), коэффициенты монотонной корреляции тем более равны 1 и -1 соответственно. Обратное утверждение неверно, например, коэффициент монотонной корреляции может быть равен единице или быть близким к единице, в то же время коэффициент линейной корреляции может быть близким к нулю. В любом случае значение коэффициента линейной корреляции по модулю не превосходит коэффициента монотонной корреляции. Монотонная связь - более общее понятие, чем линейная.

На фиг. 4а показаны пять непрерывных сигналов в одном интервале времени t. Для всех четырех пар сигналов, включающих сигнал f(t), коэффициенты монотонной корреляции равны единице, тогда как коэффициенты линейной корреляции различны и меньше единицы. На фиг. 46, в показаны пары сигналов с коэффициентами монотонной корреляции /г 0,3 и/г 0 соответственно.

Коррелятор работает следующим образом. При включении источника питания состояние триггеров, счетчиков, регистров памяти и накапливающего сумматора произвольное. При одновременном поступлении анализируемых сигналов.на входы вырабатывается импульс, который на выходах счетчика 14 устанавливает код двоичного числа 1...1, на выходах регистров 17 и 18 памяти - коды 0...0, на выходах накапливающего сумматора 39 - код 0...0, на выходах формирователя 41 импульсов отсутствуют импульсы, на входах компараторов 1 и 2 установлен соответствующий уровень порога.

Коды отсчетов fn и fj формируются следующим образом. На информационный вход компаратора 1 поступает входной сигнал (однополярный или двухполярный), На выходах компараторов 1 и 2 формируются сигналы положительной полярности, если амплитуды входных сигналов превышают уровень порога. По переднему фронту положительных импульсов формирователи 3 и 4 формируют короткие отрицательные импульсы. G выходов формирователей 3 и 4 импульсы отрицательной полярности поступают на входы 1 и 2 элемента ИЛИ 7. С элемента И 7 отрицательные импульсы поступают на триггер 11 и устанавливают на выходе потенциал логической единицы.

Триггер 11 устанавливается в единичное состояние тем импульсом, который по времени формируется раньше. Импульс, который пришел позже, подтверждает единичное состояние триггера 11. Триггер 11 устанавли0 вается в нулевое состояние импульсом отрицательной полярности с формирователя 5 (этот импул ьс формируется тогда и только тогда, когда на выходах компараторов 1 и 2 одновременно устанавливаются уровни

5 логического нуля). Уровни логического нуля поступают соответственно на входы элемента И-НЕ 6. На выходе элемента И-НЕ 6 «Ьоомиоуется положительный перепад, который поступает на формирователь 5. По пе0 реднему фронту положительного импульса формирователь 5 вырабатывает импульс отрицательной полярности, который поступает на триггер 11 и устанавливает его в нулевое состояние. Длительность импуль5 сов отрицательной полярности, формируемых на выходе компараторов 1 и 2, и одновременно их положение соответствуют переходу от одной полярности к другой, зависит от уровня порога и скорости нараста0 ния амплитуды сигналов. Эти импульсы могут установить триггер 11 в нулевое состояние только в ом случае, когда времена переходрв от одной полярности к другой совпадают и по длительности превышают

5 длительность импульсов, необходимую для установки триггера 11 в нулевое состояние. С триггера 11 потенциал логической единицы поступает на генератор 12 тактовых импульсов. Длительность единичного

0 состояния триггера 11 определяет массив отсчетов fj и f|. На выходе генератора 12 тактовых импульсов формируется последовательность положительных импульсов. Эти импульсы поступают на счетчик 14 и на ана5 лого-цифровые преобразователи 15 и 16. Счетчик 14 изменяет свое состояние при переходе сигнала от уровня логического нуля к уровню логической единицы на счетном входе. Поскольку исходное состояние счет0 чика 14 соответствует двоичному коду 11...1, при поступлении на его вход N импульсов на его выходах устанавливается двоичный код числа N-1 (так как счетчик переходит в состояние 00...0).

5 Тактовые импульсы, поступающие на входы АЦП 15 и 16, преобразуют аналоговую форму входных сигналов в цифровую форму.

Выборка входного сигнала осуществляется по переднему фронту тактовых импульсов. Кодирование производится с подачей заднего фронта тактового импульса. Результат, полученный во время кодирования, выдается на входной регистр АЦП в цифровой форме. Таким образом, с приходом каждого i-ro тактового импульса с генератора 12 на выходах АЦП 15 и 16 находятся выборки fV и fi отсчётов входных сигналов Uex.1 и Uex.2. Запись этих отсчетов с выходов АЦП 15 и 16 на выходы регистров 17 и 18 памяти осуществляется импульсами с элемента 13 задержки, на вход которого поступают тактовые импульсы с генератора 12. С элемента 13 импульсы, задержанные на время, необходимое для выполнения операции сложения в накапливающем сумматоре 39, поступают на регистры 18 и 17 памяти. Запись с выходов АЦП 15 и 16 осуществляется по входам регистров 18 и 17 при переходе сигнала из состояния логического нуля в логическую единицу. Информация с выходов АЦП 15 и 16 переписывается на выходе регистров 17 и 18 памяти. Информация fi отсчетов в АЦП 15 и 16 находится в промежутке времени между задним фронтом i-ro тактового импульса и передним фронтом i+1-го тактового импульса. Информация с выходов АЦП 15 и 16 записывается в регистры 17 и 18 памяти импульсом с выхода 2 элемента 13, задержанным относительно заднего фронта тактовых импульсов. Причем, начиная с второго такта, информация на выходе АЦП 15 и информаци fi отсчета на выходе регистра 17 памяти присутствуют одновременно на отрезке времени. Таким образом, на этом отрезке времени в регистре 17 памяти присутствует информация fj отсчета входного сигнала 1)вх.1,а в АЦП 15-информация fi-н1 отсчета входного сигнала UBX.L В регистре 18 памяти присутствует информация fi отсчета входного сигнала Uex.2, а в АЦП 16- информация fj+i отсчета входного сигнала

Uex.2.

Г 1,если ti j 0, если |Д| + ДП 1

U, если (Д О Д +Д О) Выходы элементов 29, 30 и 23 соедиме- ны с входами дешифратора 31. На одном из выходов дешифратора 31 устанавливается потенциал логического нуля. Двоичный код на выходах элементов 23...29 и 30 определяет тип операции, выполняемой накапливающим сумматором 39.

При коде 001 выполняется операция сложения плюс 1, а при коде 010 - операция сложения не выполняется (сложение нуля)и при коде 100 выполняется операция сложение минус 1. Данные операции выполняются на накапливающем сумматоре

39. Значение + 1 в двоичном коде формируется с помощью элементов 32-34. В дели- теле 44 вычисляется коэффициент монотонной корреляции fi .

Формула изобретен и я

Цифровой коррелятор, содержащий первый и второй аналого-цифровые преобразователи, первый компаратор, триггер, генератор тактовых импульсов, два регист0 ра памяти, первый элемент И и накапливающий сумматор, причем информационные входы второго и первого аналого-цифровых преобразователей являются соответственно первым и вторым информационными

5 входами коррелятора, отличающийся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления оценки монотонной корреляции сигналов, в него введены второй компара0 тор, четыре формирователя импульсов, четыре элемента И-НЕ, с второго по десятый элементы И, элемент задержки, счетчик, две схемы сравнения, два элемента НЕ, два элемента ИЛИ, дешифратор, группа элементов

5 НЕ, два шинных формирователя/блок элементов И-НЕ, блок элементов И, мультиплексор и делитель, причем информационные входы первого и второго компараторов подключены соответственно

0 к первому и второму информационным входам коррелятора, опорные входы первого и второго компараторов подключены соответственно к первому и второму входам опорного сигнала коррелятора, выход больше

5 первого компаратора соединен с первым входом первого элемента И-НЕ и через первый формирователь импульсов - с первым входом первого элемента И, выход которого соединен с входом установки в единицу

0 триггера и первым входом второго элемента И, второй вход которого соединен с входом запуска генератора тактовых импульсов и прямым выходом триггера, вход установки в нуль которого соединен с выходом второго

5 формирователя импульсов, вход которого соединен с выходом первого элемента И- НЕ, второй вход которого соединен с выходом больше второго компаратора и входом третьего формирователя импульсов.

0 выход которого соединен с вторым входом первого элемента И, выход генератора тактовых импульсов соединен с входом элемента задержки, счетным входом счетчика и входами запуска первого и второго аналого5 цифровых преобразователей, выход первого аналого-цифрового преобразователя соединен с первым входом первой схемы сравнения и информационным входом первого регистра памяти, выход которого со- единен с вторым входом первой схемы

сравнения, первый выход элемента задержки соединен с первым входом третьего элемента И, второй вход которого соединен с выходом четвертого элемента И, группа входов которого соединена с группой разряд- ных выходов счетчика, второй выход элемента задержки соединен с тактовыми входами первого и второго регистров памяти, информационный вход второго регистра памяти соединен с выходом второго анало- го-цифрового преобразователя и первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра памяти, выход больше первой схемы, сравнения соединен с первым вхо- дом второго элемента И-НЕ и первым входом пятого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход второго элемента И-НЕ соединен с первым входом шестого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход меньше первой схемы сравнения соединен с вторым входом второго элемента И-НЕ и первым входом седьмого элемента И, выход которого соединен с третьим входом первого элемента ИЛИ, выход больше второй схемы сравнения соединен с первым входом третьего элемента И-НЕ, вторым входом пятого элемента И и первым входом восьмого элемента И, второй вход которого соединен с выходом меньше первой схемы сравнения, выход меньше второй схемы сравнения соединен с вторым входом третьего элемента И-НЕ, вторым входом седьмого элемента И, первым входом девятого элемента И, второй вход которого соединен с выходом больше первой схемы сравнения, выход третьего элемента И-НЕ соединен с вторым входом шестого элемен- та И, выходы восьмого и девятого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первыми входами дешифратора и четвертого элемента И-НЕ, выход которого соединен с вторым входом дешифратора, третий вход которого соединен с выходом первого элемента. ИЛИ и вторым входом четвертого элемента И-НЕ, первый выход дешифратора соединен с зна- ковым входом накапливающего сумматора

и через первый элемент НЕ - с входом первого разряда накапливающего сумматора, второй выход дешифратора соединен с первым входом десятого элемента И, второй вход которого соединен с выходом третьего элемента И, выход десятого элемента И соединен с тактовым входом накапливающего сумматора, третий выход дешифратора соединен с входами элементов НЕ группы, группа выходов которых соединена с группой входов, старших разрядов накапливающего сумматора, информационный выход накапливающего сумматора соединен с информационными входами блока элементов И-НЕ и блока элементов И, выходы которых соединены соответственно с первым и вторым информационными входами мультиплексора, выход знакового разряда накапливающего сумматора соединен с входом знакового разряда первого информаци- онного входа первого шинного формирователя, управляющим входом мультиплексора и блока элементов И-НЕ и через второй элемент НЕ - с управляющим входом блока элементов И, выход мультиплексора соединен с разрядными входами первого информационного входа первого шинного формирователя, выход счетчика соединен с первым информационным входом второго шинного формирователя, выход второго формирователя импульсов соединен с информационным входом четвертого формирователя импульсов, первый выход которого соединен с управляющим входом делителя, входы делимого и делителя которого соединены соответственно с первыми выходами первого и второго шинных формирователей, выход делителя соединен с вторыми информационными входами первого и второго шинных формирователей, .второй выход четвертого формирователя импульсов соединен с управляющими/входами второго и первого шинных формирователей, вторые выходы/которых через монтажное ИЛИ подключены к выходу коррелятора, выход второго элемента И соединен с входами установки в,нуль счетчика, первого и второго регистров памяти, накапливающего сумматора, четвертого формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Телевизионное следящее устройство | 1988 |

|

SU1690217A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ УГЛОВОЙ КООРДИНАТЫ СИСТЕМЫ ПОСАДКИ | 1990 |

|

SU1760868A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

Изобретение относится к измерительной технике, преимущественно к анализу формы сигналов, количественной ее оценки и может быть использовано для построения цифровых корреляторов, определяющих оценку монотонной корреляции двух сигналов. Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности вычисления коэффициента монотонной корреляции сигналов. Коррелятор содержит компараторы 1,2, формирователи 3,4, 5, 41 импульсов, элементы И-НЕ 6, 21- 23, элементы И 7-10, 24-28, 37, триггер 11, генератор 12 тактовых сигналов, элемент 13 задержки, счетчик 14, аналого-цифровые преобразователи 15, 16, регистры 17, 18 памяти, две схемы сравнения, два элемента НЕ, два элемента ИЛИ. дешифратор, группу элементов НЕ, блок элементов И-НЕ, блок элементов И, накапливающий сумматор 39, мультиплексор 40, два шинных формирова- теля.42, 43, делитель 44. 1 ил.

D

L

Фиг.2

CQ

Д 4-++fO

+++ + 0

ti 111111111 ,0

A1: 4- + + .Ц-.Ц-0-

-К+- + ++--Ы-t: 11-111 1-1 0-1 1

I

т

6

Ai ++ -n- +1- + + + + й« .4--+- +

1-1 И MM Ч

-э-i

t

,3

(L

f(t)

гллллл

lL.

t

1-1 И MM Ч

M

| Цифровой коррелятор | 1986 |

|

SU1416980A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1989-08-01—Подача