(Л

4

о

05

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство определения конца блока циклического кода | 1987 |

|

SU1515381A2 |

| Устройство динамического управления потоками междугородных вызовов на автоматической телефонной станции | 1988 |

|

SU1617658A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ КОНЦА БЛОКА ЦИКЛИЧЕСКОГО | 1973 |

|

SU407428A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU743218A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для измерения параметров жидкости | 1990 |

|

SU1830460A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

Изобретение относится к электросвязи, м.б. использовано в устр-вах циклового фазирования систем передачи данных, применяющих полные или укороченные циклические коды. Цель изобретения - уменьшение вероятности ложного определения конца блока циклического кода. Устройство содержит приемный регистр 1, состоящий из ячеек памяти 2 по числу бит в кодовом блоке, сдвигающий регистр 3 с обратными связями, состоящий из ячеек памяти 4 по числу проверочных разрядов кода и сумматоров 5 по модулю два по числу, определяемому числом обратных связей и связей с выходом приемного регистра 1, элемент ИЛИ 6, инвертор 7, Для достижения цели в устройство введены блок памяти 8, дополнительный элемент ИЛИ 9, элемент задержки 10, счетчики 11, 12 и пороговый блок 13. 1 ил.

к

Изобретение относится к электросвязи, может быть использовано в устройствах циклового фазирования систем передачи данных, применяющих полные или укороченные циклические коды и является усовершенствованием устройства по авт. св.

№ 407428.

Цель изобретения - уменьшение вероятности ложного определения конца блока циклического кода.

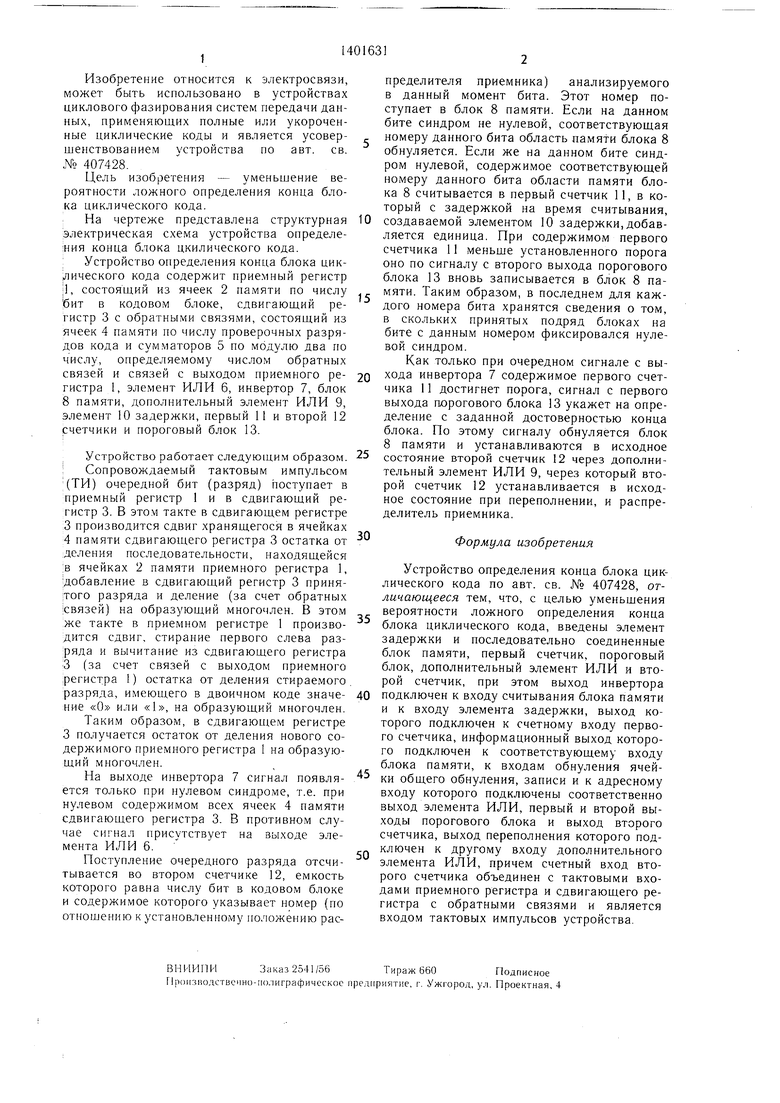

На чертеже представлена структурная электрическая схема устройства определе- ;ния конца блока цкилического кода.

Устройство определения конца блока циклического кода содержит приемный регистр 1, состоящий из ячеек 2 памяти по числу бит в кодовом блоке, сдвигающий регистр 3 с обратными связями, состоящий из ячеек 4 памяти по числу проверочных разрядов кода и сумматоров 5 по модулю два по числу, определяемому числом обратных связей и связей с выходо.м приемного регистра 1, элемент ИЛИ 6, инвертор 7, блок 8 памяти, дополнительный элемент ИЛИ 9, элемент 10 задержки, первый 11 и второй 12 счетчики и пороговый блок 13.

Устройство работает следующим образом. ; СопровождаемьЕЙ тактовым импульсом (ТИ) очередной бит (разряд) поступает в приемный регистр 1 и в сдвигающий регистр 3. В этом такте в сдвигающем регистре

3производится сдвиг хранящегося в ячейках

4памяти сдвигающего регистра 3 остатка от деления последовательности, находящейся :в ячейках 2 памяти приемного регистра 1, добавление в сдвигающий регистр 3 приня- iToro разряда и деление (за счет обратных связей) на образующий многочлен. В этом же такте в приемном регистре 1 производится сдвиг, стирание первого слева разряда и вычитание из сдвигающего регистра 3 (за счет связей с выходом приемного регистра 1) остатка от деления стираемого разряда, имеющего в двоичном коде значение «О или «1, на образующий многочлен.

Таким образом, в сдвигающем регистре 3 получается остаток от деления нового содержимого приемного регистра 1 на образующий многочлен.

На выходе инвертора 7 сигнал появляется только при нулевом синдроме, т.е. при нулевом содержимом всех ячеек 4 памяти сдвигающего регистра 3. В противном случае сигнал присутствует на выходе элемента ИЛИ 6.

Поступление очередного разряда отсчитывается во втором счетчике 12, емкость которого равна числу бит в кодовом блоке и содержимое которого указывает номер (по отнощению к установленному положению рас0

5

0

5

0

5

0

5

0

пределителя приемника) анализируемого в данный момент бита. Этот номер поступает в блок 8 памяти. Если на данном бите синдром не нулевой, соответствующая номеру данного бита область памяти блока 8 обнуляется. Если же на данном бите синдром нулевой, содержимое соответствующей номеру данного бита области памяти блока 8 считывается в первый счетчик 11, в который с задержкой на время считывания, создаваемой элементом 10 задержки, добавляется единица. При содержимом первого счетчика 11 меньше установленного порога оно по сигналу с второго выхода порогового блока 13 вновь записывается в блок 8 памяти. Таким образом, в последнем для каждого номера бита хранятся сведения о том, в скольких принятых подряд блоках на бите с данным номером фиксировался нулевой синдром.

Как только при очередном сигнале с выхода инвертора 1 содержимое первого счетчика 11 достигнет порога, сигнал с первого выхода порогового блока 13 укажет на определение с заданной достоверностью конца блока. По этому сигналу обнуляется блок 8 памяти и устанавливаются в исходное состояние второй счетчик 12 через дополнительный элемент ИЛИ 9, через который второй счетчик 12 устанавливается в исходное состояние при переполнении, и распределитель приемника.

Формула изобретения

Устройство определения конца блока циклического кода по авт. св. № 407428, отличающееся тем, что, с целью уменьшения вероятности ложного определения конца блока циклического кода, введены элемент задержки и последовательно соединенные блок памяти, первый счетчик, пороговый блок, дополнительный элемент ИЛИ и второй счетчик, при этом выход инвертора подключен к входу считывания блока памяти и к входу элемента задержки, выход которого подключен к счетному входу первого счетчика, информационный выход которого подключен к соответствующему входу блока памяти, к входам обнуления ячейки общего обнуления, записи и к адресному входу которого подключены соответственно выход элемента ИЛИ, первый и второй выходы порогового блока и выход второго счетчика, выход переполнения которого подключен к другому входу дополнительного элемента ИЛИ, причем счетный вход второго счетчика объединен с тактовыми входами приемного регистра и сдвигающего регистра с обратными связями и является входом тактовых импульсов устройства.

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ КОНЦА БЛОКА ЦИКЛИЧЕСКОГО | 0 |

|

SU407428A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-15—Подача