1

Изобретение относится к области электросвязи и может быть использовано при конструировании устройств циклового фазирования в системах передачи данных (СПД), использующих полные или укороченные циклические коды.

Известны устройства определения конца блока циклического кода, реализующие параллельный способ синхронизации с помощью специальных служебных комбинаций и последовательный и параллельный способы синхронизации по информационным комбинациям.

Недостатком устройств, реализующих параллельный способ, является необходимость введения специальной служебной комбинации и, соответственно, наличие датчика ее в передатчике и дещифратора в нриемпике. Иедостатком устройств, реализующих последовательный и параллельный способы, является то, что проверка окончания блока кода выполняется только после приема очередной комбинации, т. е. один раз за время поступления кодовой комбинации, что значительно увеличивает время ноиска конца блока кода но сравнению с нараллельным способом, при котором проверка конца блока выполняется с каждым принимаемым разрядом.

С целью уменьщения времени определения конца блока циклического кода в предлагаемом устройстве выход последней ячейки памяти приемного регистра подключен к одному из входов соответствующих сумматоров по модулю 2 сдвигающего регистра с обратными связями, к другим входам которых подключеиы выходы соответствующих ячеек памяти того же сдвигающего регистра.

Поступающая в декодирующее устройство п - разрядная комбинация может быть описана одним из двух выражений

10

F (х) + а, + + -f

+ ... -f -f (I)

или

15

F (х) г «о + ах + а.,х + .. . + +

+ .. . + + .(II)

Если Р(х)- кодовая комбинация, то остаток R(x) от деления ее на образующий многочлен g(x) равен нулю.

Если R(x)Q, то проверяется следующая п-разрядпая комбинапия /(х), образованная

из предыдущей стиранием первого разряда слева и добавлением справа виовь принятого разряда. При этом новый остаток R(x) можно получить из предыдущего остатка. Для комбинации, описываемой выражением

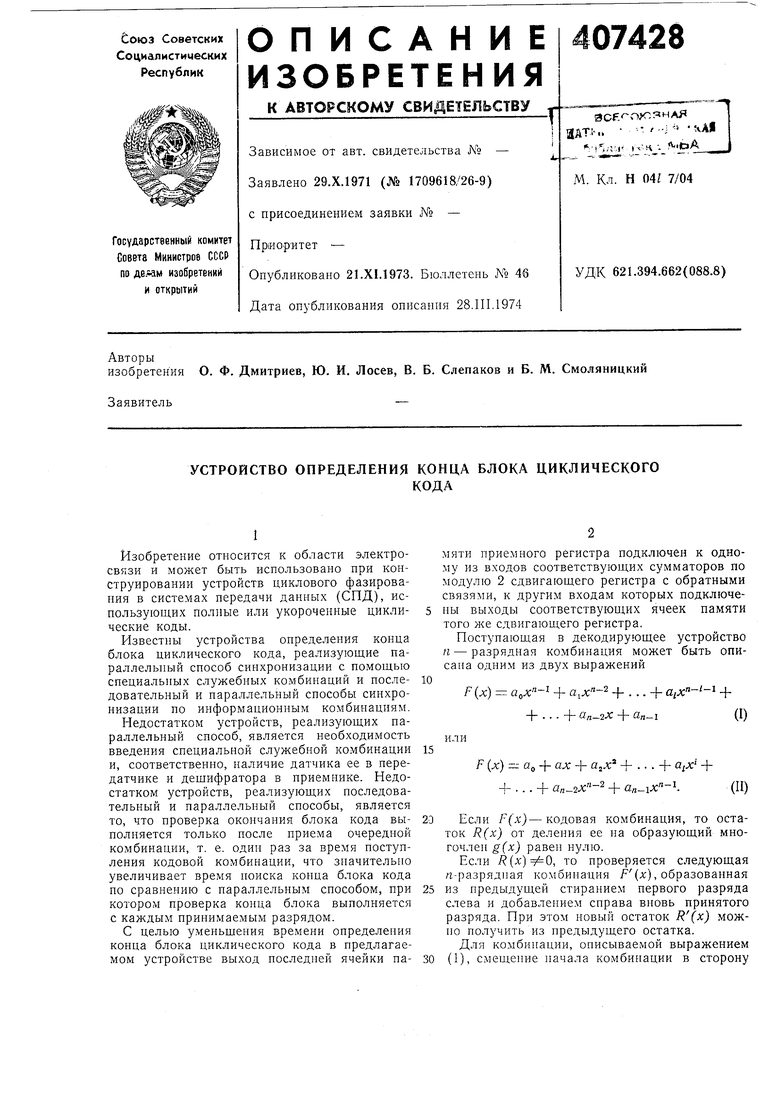

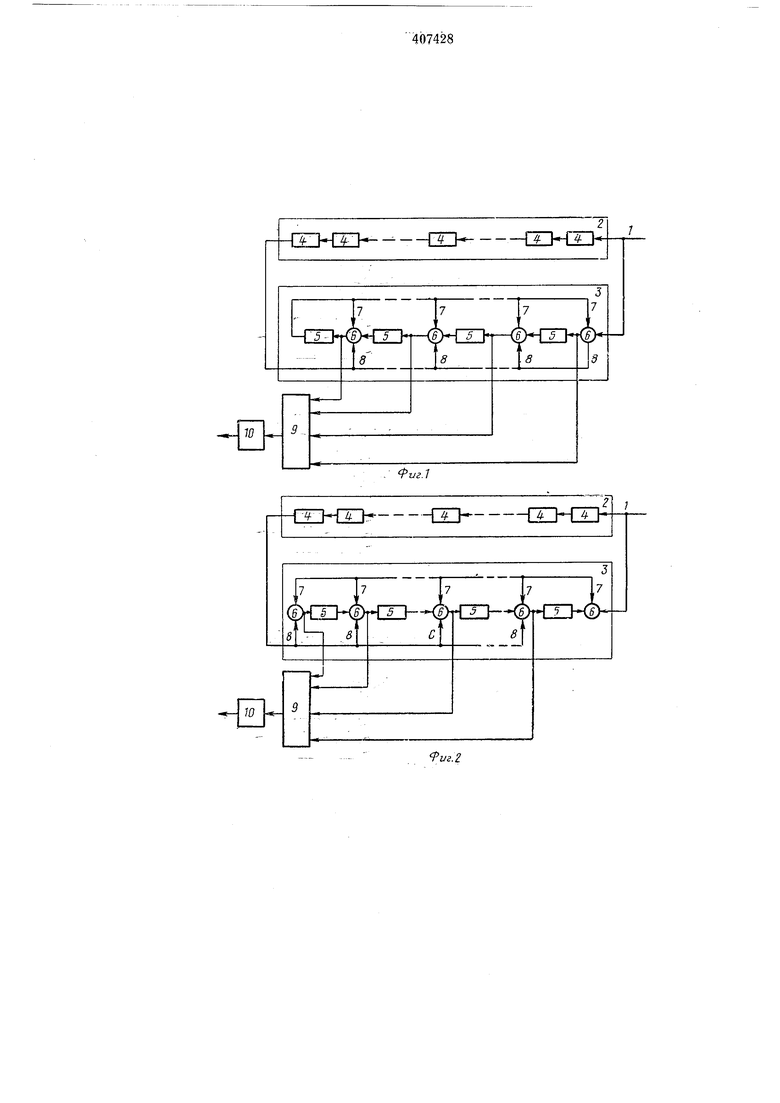

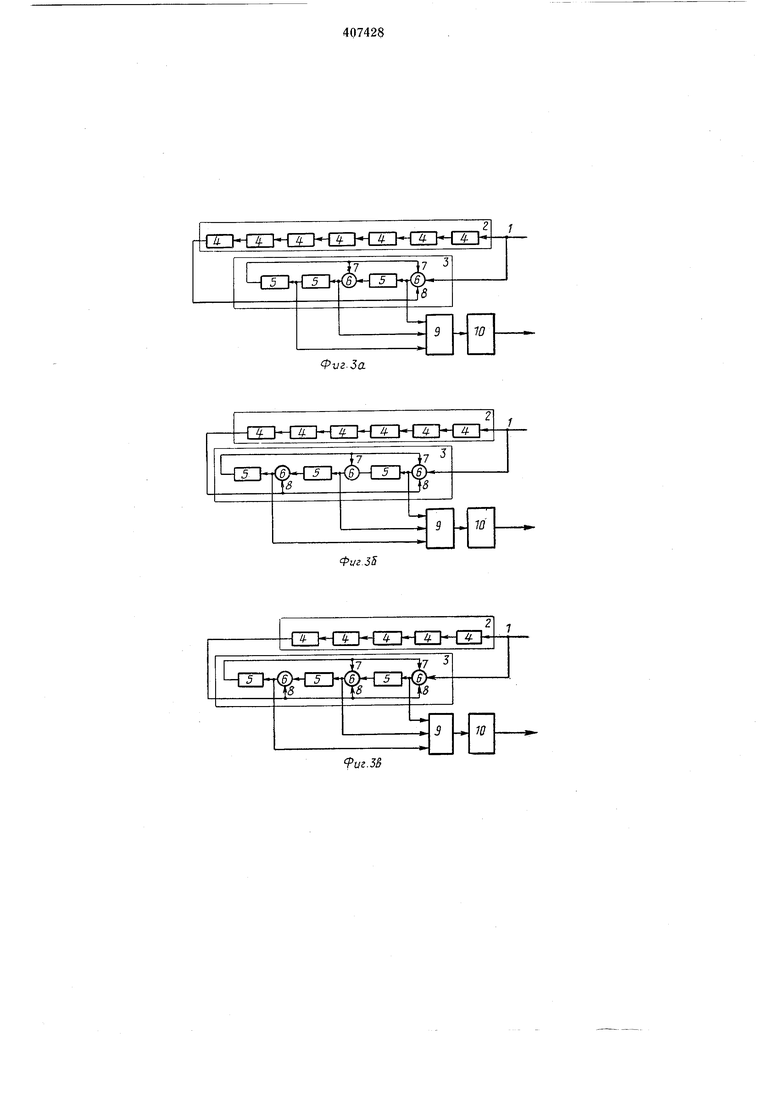

(1), смещение начала комбинации в сторону равнозначно умножению ее на л:, ноэтому R(х) равен разностн остатка от )1,еления R(x)x + а„ . g(f)V где Ш- вновьнринятый;разряд н,-остатка от деления- ,.: : ... g(x). . . где аол; - стираемый разряд. Для комбинации, описываемой выражением (II), смещение начала комбинации в сторону ао равнозначно делению ее на х, ноэтому R(х) равен разности остатка от деления , : R-(x)п I + .апЖ .-т- вновь .принятый разряд и остатка от деления gp где йо - стираемый разряд. Так как для циклического кода всегда по mod g(.s;), то .-(x) . : g(x) . При использовании кода, укороченного на 1-разрядов, нервыми слева разрядами, стираемыми при приеме очередного разряда, будут а, - для выражения(I) - для выражения -для выражения -Поэтому, вычитаемые, в разности, образующей-..(x) ,;: соответственно получаются , . . , ,„ g(xY g(x) На.фиг.;-, и .2 показаны, в. общем виде схемы устройств для...определения конца блока двоичного циклического кода; на фиг. 3 и 4- общий-вид . .устройства для онределения конца блока полного (7; 4) кода (фиг. 3,а и 4,-а), имеющего .образующий многочлен g(K)x - -x-}, и кодов, полученных укорочением его на один (фиг. 3,6 и 4,6) и два (фиг. 3,в и 4,в) разряда. Схемь на фиг.Г и 3 предназначены для ,бинаций, описываемых выражением (I), а схемы на фиг. 2 и 4 - для комбинаций, описываемых выраже.нием (II). Еходн.ая щина 1 соединена с приемным регистром 2 и сдвигающим регистром 3 с обратными, связями ..(СР.ОС). Приемный регистр 2. СОСТОИТ; из ячеек 4 памяти, число которых рарно. длине, блока кода. Регистр 3 состоит ИЗ- последовательно, соединенных ячеек 5 памяти, по числу проверочных разрядОв кода, и сумматбров6 по модулю 2. Количество сум..мато.ро.в 6 зависит от числа обратных связей 7 в регистре 3; определяемого образующим многочленом, и числа связей 8 выходной ячейки 4 регистра 2 с ячейками 5 памяти регистра 3, определяемого количеством едипиц в остатке от деления стираемого разряда на Ъбразую1цйй многочлен. Входы всех ячеек 5 памяти соединены со входами сборки 9, выход которой подключен ко входу инвертора 10. Работа устройства ..проис)(одйт следующимобразом. .О.ч.ередной .р.азр.яд. поступает-.в рег.ист)ы 2 и 3. В этом такте в регистре 3 производится сдвиг хранящегося в ячейках 5 памяти остатка от деления комбинации, находящейся в ячейках 4 памяти-лриемпого, . реглсхра... бавление в регистр 3 принятого разряда и деление (за счет обратных связей 7) па образу-, ющий м-ногочлен. ,.В.-эхом..,же такте .в, прием-, ном регистре 2 производится сдвиг, стирание первого слева разряда и вычитание из регистра 3 (за счет связей 8) остатка от деления стираемого разряда, имеющего- - вдвоичномкоде значение «О или «1, на образующий многочлен. Таким.. о.бразом,.,в регистре З.:паходптся остаток от деления нового содержимого приемного регистра 2 на образующий многочлен. На выходе инвертора 10 сигнал появляется только при нулевом содержимом ячеек 5 па.мяти регистра 3, т. е. когда в приемном регистре 2 находится кодовая комбинапия. .. П р ед ме.т..и.з о б.р е те н и.я ;.. ... Устройство определения коцца. блока циклического кода, содержащее приемный регистр, .состоящий из последовательно соединенных ячеек .памяти по числу разрядов кода, при этом вход приемного регистра ..подключен ко .входу сдвигающего регистра с обратными связями, состоящего из последовательно .соединенны.х сумматоров по модулю 2 и ячеек памяти по числу проверочных разрядо.в кода, прпчем вх.одь ячеек памятп. сдвигагощего регистра с обратными связями через схему «ИЛИ (сборку) подключепьт ко входу инвертора, отличающееся тем, что, с целью уменьщения времени определения конца блока циклического кода, выход носледней ячейки памяти приемного регистра подключен к одному из входов соответствующих су.мматоров но модулю 2 сдвигающего регистра с обратными связями, к другим входам кото- . рых подключены выходы соответствующих ячеек памяти того же сдвигающего рег.истра.

Рг/гЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1977 |

|

SU743218A1 |

| Устройство определения конца блока циклического кода | 1986 |

|

SU1401631A2 |

| Система для приема и накопления информации | 1980 |

|

SU943800A1 |

| Устройство для перестановочного декодирования циклических кодов | 1973 |

|

SU552716A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ двоичных ЦИКЛИЧЕСКИХ кодов | 1972 |

|

SU335691A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

Тиг.ЗВ

РигЛа.

fv2.5

Даты

1973-01-01—Публикация