СО

Изобретение относится к вычислительной технике и может быть применено в системах цифровой обработки сигналов для сглаживания и экстраполяции линейно нарастающего или убывающего сигнала.

Целью изобретения является повышение точности.

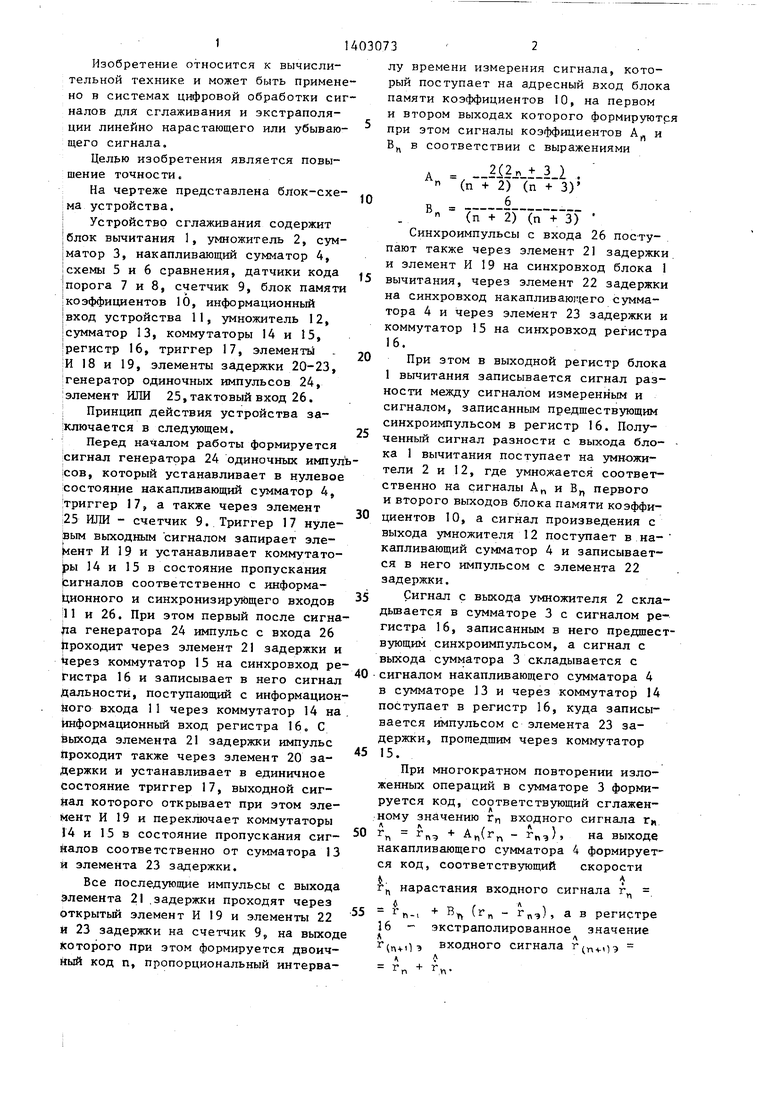

На чертеже представлена блок-схе- :ма устройства.

I Устройство сглаживания содержит |блок вычитания 1, умножитель 2, сум- матор 3, накапливающий сумматор 4, Iсхемы 5 и 6 сравнения, датчики кода Порога 7 и 8, счетчик 9, блок памяти I коэффициентов 10, информационный |вход устройства 11, умножитель 12, Iсумматор 13, коммутаторы 14 и 15, |регистр 16, триггер 17, элементь |И 18 и 19, элементы задержки 20-23, Iгенератор одиночных импульсов 24, элемент ИЛИ 25, тактовый вход 26, : Принцип действия устройства за- ключается в следующем.

Перед началом работы формируется |Сигнал генератора 24 одиночных импул |сов, который устанавливает в нулевое состояние накапливающий сумматор 4, триггер 17, а также через элемент 25 ИЛИ - счетчик 9. Триггер 17 нуле- йым выходным сигналом запирает эле- Иент И I9 и устанавливает коммутато- Ьы 14 и 15 в состояние пропускания Сигналов соответственно с информа- 1;ионного и синхронизирующего входов 111 и 26. При этом первый после сигна ha генератора 24 импульс с входа 26 Проходит через элемент 21 задержки к 1ерез коммутатор 15 на синхровход регистра 16 и записывает в него сигнал Дальности, поступающий с информацион його входа 11 через коммутатор 14 на информационный вход регистра 16, С йыхода элемента 21 задержки импульс Проходит также через элемент 20 задержки и устанавливает в единичное состояние триггер 17, выходной сиг- Нал которого открывает при этом элемент И 19 и переключает коммутаторы 14 и 15 в состояние пропускания сиг- йалов соответственно от сумматора 13 и элемента 23 задержки.

Все последующие импульсы с выхода элемента 21 .задержки проходят через Открытый элемент И 19 и элементы 22 и 23 задержки на счетчик 9, на выход Которого при этом формируется двоич- йый код п, пропорциональный интерва

5

лу времени измерения сигнала, который поступает на адресный вход блока памяти коэффициентов 10, на первом и втором выходах которого формируются при этом сигналы коэффициентов А„ и В в соответствии с выражениями

А - .1 . (п + 2) (п + 3)

06

. (п + 2) (п + 3)

Синхроимпульсы с входа 26 поступают также через элемент 21 задержки, и элемент И 19 на синхровход блока 1

5 вычитания, через элемент 22 задержки на синхровход накапливаю1Г(его сумматора 4 и через элемент 23 задержки и коммутатор 15 на синхровход регистра 16.

0 При этом в выходной регистр блока 1 вычитания записывается сигнал разности между сигналом измеренным и сигналом, записанным предшествующим синхроимпульсом в регистр 16. Полученный сигнал разности с выхода бло- - ка 1 вычитания поступает на умножители 2 и 12, где умножается соответственно на сигналы А, и В„ первого и второго выходов блока памяти коэффи0 циентов 10, а сигнал произведения с выхода умножителя 12 поступает в на- капливающий сумматор 4 и записывается в него импульсом с элемента 22 задержки.

5 Сигнал с выхода умножителя 2 скла- дьшается в сумматоре 3 с сигналом регистра 16, записанным в него предшествующим синхроимпульсом, а сигнал с выхода сз матора 3 складывается с

0 сигналом накапливающего сумматора 4 в сумматоре 13 и через коммутатор 14 поступает в регистр 16, куда записывается ш 1пульсом с элемента 23 задержки, прошедшим через коммутатор

5 15.

При многократном повторении изложенных операций в сумматоре 3 формируется код, соответствующий сглаженному значению Гп входного сигнала г,

л . /

0 г„ г„, + А(г„ - г„э),

п ОЭ

накапливающего сумматора ся код, соответствующий

;

на выходе 4 формирует- скорости

нарастания входного сигнала г

5 г,

B,v (г„ л ГпЭ

16

(пч-Оэ

л г„ + г

п - п

экстраполированное

), а в регистре значение

входного сигнала г..,

,т

Код счетчика 9 поступает также на схему 6 сравнения. После истечения определенного времени измерения,когда коэффициент Bf, становится малым, код, поступающий со счетчика 8, превышает порог, поступающий от датчика 8 на второй вход схемы 6 сравнения, на выходе которого при этом формируется сигнал, открьшающий элемент И 18. При этом в случае возникновения на выходе блока вычитания 1 большого значения сигнала (невязки), поступающего на схему 5 сравнения и превышающего порог, поступающий на его второй вход от датчика 7, на выходе схемы 5 сравнения формируется сигнал, проходящий через открытый элемент И 18, элемент 25 ИЛИ и обнуляющий счетчик 9. При этом сигналы коэффициента А и В„ на выходах блока 10 вновь приобретают большие значения и сигнал г быстро подстраивается под изменившийся входной сигнал г„.

Формула изобретения

Устройство сглаживания.сигнала, содержащее блок вычитания, первый

0

5

ственно с входом задания второго порога устройства и выходом блока вычитания, вход уменьшаемого которого соединен с информационным входом устройства и первым информационным входом первого коммутатора, выход которого соединен с информационным входом регистра, выход которого соединен с выходом устройства, входом первого слагаемого первого сумматора и входом вычитаемого блока вычитания, выход которого соединен с входом первого сомножителя первого умножителя, выход которого соединен с входом второго слагаемого первого сумматора, выход которого соединен с входом первого слагаемого второго сумматора, вход второго слагаемого и выход которого соединены соответственно с выходом накапливающего сумматора и вторым информационным входом первого коммутатора, управляющий вход которого соединен с выходом триггера и управляю- 5 щим входом второго коммутатора, первый информационный вход которого соединен с выходом первого элемента задержки и входом второго элемента задержки, выход которого соединен с вхо0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1203552A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВУХ ПЕРЕМЕННЫХ | 1983 |

|

SU1362318A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

Изобретение относится к области вычислительной техники, может быть применено для сглаживания и экстраполяции линейно нарастающего или убывающего сигнала. Устройство позволяет повысить точность работы в более широком диапазоне скорости изменения сигнала, поскольку в нем реализован алгоритм оптимальной линейной фильтрации Калмана и по истечении определенного времени фильтрации включается допусковой контроль рассогласования между входным и выходным сигналами с помощью схемы 5 сравнения. В случае, когда рассогласование превышает установленный порог, производится обнуление интервала времени сглаживания в счетчике 9 временных интервалов и отсчет времени начинается снова от НУЛЯ. 1 ил.

коммутатор, регистр, первый сумматор, ЗО ДОм установки в 1 триггера, выход

блок памяти коэффициентов и счетчик, причем выход счетчика соединен с адресным ВХОДОМ блока памяти коэффициентов, отличающееся тем, что с целью повьш1ения точности, в него введены два умножителя, второй сумматор, накапливающий сумматор, второй коммутатор, четыре элемента задержки, триггер, два элемента И, две схемы сравнения, элемент ИЛИ и генератор одиночных импульсов, выход которого соединен с входами установки в О триггера и накапливающего сумматора и первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом первой схемы сравнения, первый и второй входы которой соединены соответственно с входом задания первого порога устройства и выходом счетчика, вход установки в О которого соединен с выходом элемента ИЛИ, второй вход первого элемента И соединен с выходом

которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента за держки и входом третьего элемента задержки, выход которого соединен с входом синхронизации накапливающего сумматора и входом четвертого элемента задержки, выход которого соединен

40 со счетным входом счетчика и вторым информационным входом второго коммутатора, выход которого соединен с входом синхронизации регистра, выходы первого и второго коэффициентов

45 блока памяти соединены соответственно с входом второго сомножителя первого умножителя и входом первого сомножителя второго умножителя, вход второго сомножителя и выход которого

gQ соединены соответственно с выходом блока вычитания и информационным входом накапливающего сумматора, вход первого элемента задержки соединен

с тактовым входом устройства, выход второй схемы сравнения, первый и вто- 55 второго элемента И соединен с входом рой входы которой соединены соответ- синхронизации блока вычитания.

ВНИИПИ Заказ 2862/41 Тираж 704

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и входом третьего элемента задержки, выход которого соединен с входом синхронизации накапливающего сумматора и входом четвертого элемента задержки, выход которого соединен

со счетным входом счетчика и вторым информационным входом второго коммутатора, выход которого соединен с входом синхронизации регистра, выходы первого и второго коэффициентов

блока памяти соединены соответственно с входом второго сомножителя первого умножителя и входом первого сомножителя второго умножителя, вход второго сомножителя и выход которого

соединены соответственно с выходом блока вычитания и информационным входом накапливающего сумматора, вход первого элемента задержки соединен

Подписное

| Финкельштейн МоИ, Основы радиолокации | |||

| М.: Сов.радио, 1973, с.75, рис.1.7.4 | |||

| Авторское свидетельство СССР № 1201848, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1986-03-28—Подача