СО

а -j

Изобретение относится к радиотехнике и может быть использовано в радиоприемных и радиопередающих устройствах и в системах обработки инфор- йании.

Целью изобретения является повышение точности установки выходной частоты.

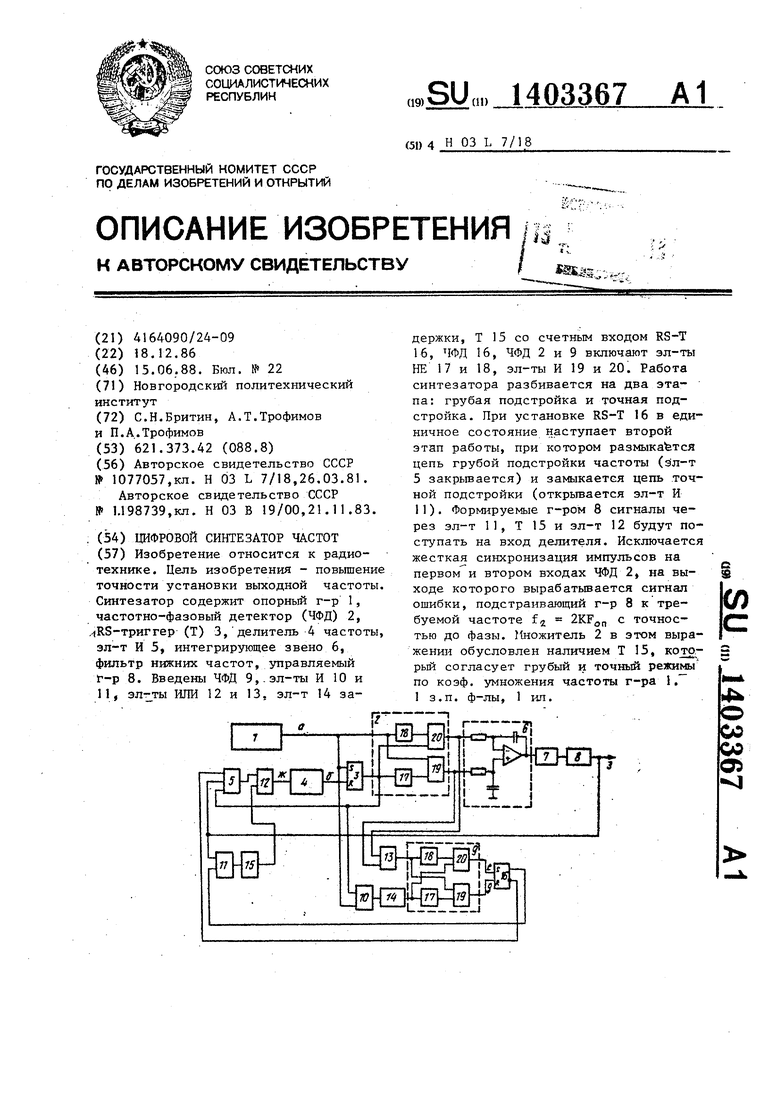

На чертеже представлена электрическая структурная схема цифрового синтезатора частот.

i Цифровой синтезатор частот содер|жит опорный генератор 1, первый час- тотно-фазовый детектор (ЧФД) 2, пер- |вый RS-триггер 3, делитель 4 частоты Ьервый элемент И 5, интегрирующее |звено б, фильтр 7 нижних частот, уп- |равляемый генератор 8, второй ЧФД 9, |второй элемент И 10, третий элемент И 11, первый элемент ИЛИ 12, второй |элемент ИЛИ 13, элемент задержки 14, Триггер с счетным входом 15, второй RS-триггер 16. При этом первый и второй ЧФД 2 и 9 включают первый.элемент НЕ 17, второй элемент НЕ 18, первый элемент И 19, второй элемент И 20.

Цифровой синтезатор частот работает следующим образом. ; Работа .цифрового синтезатора час- :Тот условно разбивается на два эта- ina. Н I первом этапе осуществляется груба) подстройка частоты, а на вто- jpoM - точная.

В режиме грубой подстройки после |переключення частоты выходного сиг- нала второй RS-триггер устанавлива- :ется в нулевое состояние, при кото- ipoM третий элемент И 11 закрыт, а на первый элемент И 5 подан разрещающий потенциал. Требуемое значение выходной частоты с выхода управляемого генератора 8 определяется коэффициентом деления делителя 4 и частотой Рд опорного генератора I, котррьш вырабатывает колебания типа меандр со скважностью Q. 2. Первый RS-триггер 3 по переднему фронту устанавливается в единичное состояние и откры ва-ет первый элемент И 5. Через пер- вьй элемент И 5 и первый элемент ИЛИ 12 импульсы управляемого генератора 8 поступают на вход делителя 14, ко- торьй осуществляет счет К импульсов и переключает первый RS-триггер 3 в нулевое состояние. Длительность сигнала на выходе первого RS-триггера 3 определяется частотой управляемого

генератора 8 и коэ(})фициентом деления К делителя 4. Если частота управляемого генератора 8 отличается от за- данной, задний фронт выходного импульса первого RS-триггера 3 оказывается смещенным относительно середины периода опорного колебания. При этом на выходе первого ЧФД 2 выфабатывается сигнал ошибки соответствунщего

знака, который интегрируется интегрирующим звеном б, через фильтр 7 поступает на вход -управляемого генератора 8, изменяя его частоту, такиг-i

образом, чтобы скомпенсировать сигнал ошибки. Теоретически этому условию удовлетворяет частота fj - 2KFon .

Благодаря синхронизации между сигналами опорной частоты и сигналами с выхода делителя 4 перестройка управляемого генератора 8 в рассматриваемом режиме осуществляется со скоростью, пропорциональной величине сигнала рассогласования на выходе первого ЧФД 2, что обеспечивает высокое быстродействие цифрового синтезатора частот.

Используемая в этом режиме жесткая

синхронизация приводит к ошибкам,максимальное значение t; „кй которых может достигать одного дискрета форми5

0

руемой сетки частот uf

макс

ё F.

on

Первый этап подстройки частоты осуществляется до тех пор, пока частота выходного сигнала отличается от заданной более чем на один дискрет. В этом случае длительностьiсигнала ошибки c oi превышает пороговое значение , которое рассчитывается исходя из значения минимального значения выходной частоты

1МИ«

5

Ч

1

1

f.

2К.

0

5

2 мин он Сравнение сигнала ощибки с порогом осуществляется с помощью второго ЧФД 9, на первый вход которого поступает опорный сигнал, сформированньй с по мощью второго элемента И 10 и элемен- . та задержки 14 () из сигналов опорного генератЬра 1 и первого RS-триггера 3. На второй вход второго ЧФД 9 поступают через второй элемент ИЛИ I3 сигналы с выходов первого ЧФД 2. Пока происходит подстройка частоты Гци С ) второй ЧФД 9 . формирует импульсы на первом выходе, которые поддерживают второй RS-триг5

10

20

rep 16 в нулевом состоянии, при котором цепь автоподстройки частоты замкнута. Как только длительность сигнала ошибки становится меньше пороговой о , второй ЧФД 9 начинает формировать импульсы на втором выходе, которые устанавливают второй RS-триггер 16 в.единичное состояние.

Второй ЧФД 9, работающий по описанному алгоритму, может быть реализован как первый ЧФД в виде двух цепей из последовательно.включенных первого элемента НЕ 17, первого элемента И 9,,последовательно включенных 5 второго элемента НЕ 18 и второго элемента И 20 со связями, указанными на фиг.1.

При установке второго RS-триггера 16 в единичное состояние наступает второй этап цифрового синтезатора частот, при котором размыкается цепь грубой подстройки частоты (первый элемент И 5 закрьшается) и замыкается цепь точной - фазовой автоподстройки частоты (открывается третий элемент И 11). Формируемые управляемым генератором 8 сигналы через третий элемент И 11, триггер со счетным

- т

ВХОДОМ 15 и первый элемент ИЛИ 12 непрерывно поступают на вход делителя 4. При этом исключается жесткая синхронизация импульсов на первом и втором входах фазового детектора 2, на выходе которого вырабатывается сигнал ошибки, вьшуждающий подстраиваться управляемый генератор 8 и

требуемой частоте г fj on точ- но стью до фазы. Множитель 2 в этом выражении обусловлен наличием триггера с счетным -входом 15, который позволяет согласовать грубый и точный режимы по коэффициенту з множения частоты опорного генератора.

При переключении цифрового синте25

30

35

40

45

затора частот на другую частоту этапы настройки повторяются.

Таким образом, введение указанньпс элементов значительно улучшает точ- кость установки частоты при сохранении высокого быстродействия.

Формула изобретения

1. Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый частотно- Фазп-пый детектор, интегрирующее зве-

0

0

5

но, фильтр пгокних частот, управляе- мьй генератор и первый элемент И, а ; также последовательно соединенные делитель частоты и первый RS-триггер, при этом второй вход первого частотно-фазового детектора объединен с . , вторым входом первого элемента И и подключен к выходу первого RS-триггера, а S-вход первого RS-триггера соединен с выходом опорного генератора и второй выход первого частотно-фазового детектора подключен к второму входу интегрируюрдего звена, отличающийся тем, что, с целью -- повьппения точности установки выходной частоты, между выходом опорного генератора и входом делителя частоты введены последовательно соединенные второй элемент И, элемент задержки, второй частотно-фазовый детектор, второй RS-триггер, третий элемент И,, триггер со счетным входом и первый элемент ИЛИ, а также введен второй

5 элемент ИЛИ, первый и второй входы и выход которого подключены соответственно к первому и второму выходам первого частотно-фазового детектора и второму входу второго частотно-фа0 зового детектора, второй вьгход которого соединен с S-входом второго RS-триггера, инверсный выход второго RS-триггера подключен.к третьему входу первого элемента И, второй вход второго элемента И соединен с выходом первого RS-триггера, второй вход третьего элемента И подсоединен к выходу управляемого генератора, а второй вход первого элемента ИПИ подключен к выходу первого элемента И.

2. Синтезатор по п. I, отличающийся тем, что первый и второй частотно-фазовый детектор выполнены идентично и каждый из них со5

0

45

50

55

держит последовательно соединенные первый элемент НЕ, первый элемент И, последовательно соединенные второй элемент НЕ и второй элемент И, второй вход второго элемента- И объединен с входом первого элемента НЕ и является первым входом частотно-фазового детектора, второй вход первого элемента И объединен с входом второго элемента НЕ и является вторым входом частотно-фазового детектора, при этом выход первого элемента И и выход второго элемента И являются соответственно первым и вторым выходами частотно-фазового детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| Цифровой синтезатор частот Усачева И.П. | 1986 |

|

SU1417186A2 |

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

| Цифровой синтезатор частот | 1985 |

|

SU1252940A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьппение точности установки выходной частоты. Синтезатор содержит опорный г-р 1, частотно-фазовый детектор (ЧФД) 2, ,К8-триггер (Т) 3, делитель 4 частоты, зл-т И 5, интегрирующее звено 6, фильтр нижних частот, управляемый Г-р 8. Введены ЧФД 9,.эл-ты И 10 и 11, эл-ты ИЛИ 12 и 13, зл-т 14 задержки, Т 15 со счетным входом RS-T 16, ЧФД 16, ЧФД 2 и 9 включают эл-ты НЕ 17 и 18, эл-ты И 19 и 20. Работа синтезатора разбивается на два этапа: грубая подстройка и точная подстройка. При установке RS-T 16 в единичное состояние наступает второй этап работы, при котором размыкается цепь грубой подстройки частоты (з л-т 5 закрьшается) и замыкается цепь точной подстройки (открьгоается эл-т И 11). Формируемые г-ром 8 сигналы через эл-т 11, Т 15 и эл-т 12 будут поступать на вход делителя. Исключается жесткая синхронизация импульсов на первом и втором входах ЧФД 2, на выходе которого вырабатывается сигнал ошибки, подстраивающий г-р 8 к требуемой частоте fj с точностью до фазы, {{ножитель 2 в этом выражении обусловлен наличием Т 15, кото- рьй согласует грубый и точный режимы по коэф. умножения частоты г-ра i. 1 з.п. ф-лы, 1 ил.

| Цифровой синтезатор частот | 1981 |

|

SU1077057A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-06-15—Публикация

1986-12-18—Подача