;памяти и третьим входом триггера, выход триггера записи переходов соединен с вторым входом первого элемента И и вторым входом четвертого элемента И, выход триггера подключен к входу записи буферного регистра, информационные входы которого соединены с выходами первого и второго коммутаторов, к первым информационным входам которых подключены выходы первого и третьего регистров, выход хчетчика времени соединен с вторьми информационными входами первого и второго коммутаторов, выход третьего коммутатора подключен к информационному входу первого регистра

66122

адреса, первый и второй информа1№1онные входы устройства соединены с первым и вторым информационными входами третьего коммутатора, второй информационный вход устройства соединен с информационным входом регистра управления, шестой выход которого соединен с управляющим входом третьего коммутатора, выход генератора одиночных сигналов соединен

с первым входом второго элемента

ИЛИ, счетным входом регистра адреса, тактовый вход устройства является вторым входом второго элемента ИЛИ, выход которого соединен с входбм элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для отладки программ | 1989 |

|

SU1689955A1 |

| Устройство для отладки программ | 1985 |

|

SU1280636A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее первый и второй регистры адреса, блок оперативной памяти, регистр считанной информации, триггер записи переходов и буферный регистр, причем выход буферного регистра соединен с информационным входом блока оперативной памяти, выход которого соединен с входом регистра считанной информации, выход которого является выходом устройства, выход второго регистра адреса соединен с адресным входом блока оперативной памяти, вход записи команды перехода устройства соединен с первым установочным входом триггера записи переходов, отличающееся тем, что, с целью повышения достоверности отладки, в него введены первый, второй и третий регистры, счетчик времени, два элемента ИЛИ, генератор одиночных импульсов, триггер, три коммутатора и регистр управления, причем первый . и .второй выходы регистра управления соединены соответственно с вторым установочным входом триггера записи переходов и с первым входом первого элемента ИЛИ, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые -ВХОДЫ которых соединены соответственно с первым, вторым и третьим выходами элемента задержки, выходы первого, второго и третьего элементов. И соединены соответственно с входами записи соответственно пер. вого, второго и третьего регистров, выход первого элемента ИЛИ соединен с входом записи первого регистра адреса, информационный выход которого подключен к информационному входу третьего регистра, информационный выход которого подключен к информационному входу второго регистра и информационному входу вто(Л рого регистра адреса, информационный выход которого подключен к информационному входу первого регистра, первый вход четвертого элемента И соединен с входом сброса триггера записи переходов и с четвертым выходом элемента задержки, первый о выход которого соединен с первьм Од входом пятого элемента И, выход которого соединен с входом счетчика ND tC времени, третий выход регистра управления соединен с входами управления первого и второго коммутаторов, четвертый выход регистра управления подключен к второму входу пятого элемента И и первому входу триггера, первый выход элемента задержки соединен с вторым входом триггера, пятый выход регистра управления соединен с входом записи блока оперативной памяти, выход четвертого элемента И блока соединен с входом обращения блока оперативной

1

Изобретение относится к цифровой вычислительной технике и может быть использовано для отладки в реальном масштабе времени програЬм специализированных вычислительных машин (СЦВМ).

Целью изобретения является повышение достоверности отладки программ.

С помощью элемента задержки ИЗ синхроимпульса, поступающего на вход устройства, формируют последовательность импульсов, обеспечивающих в каждом цикле, работы отлаживаемой СЦВМ распределение адресов команд переходов по регистрам устройства с последующей записью их в блок оперативной памяти и фиксируют время вьйорки команд из памяти СЦВМ.

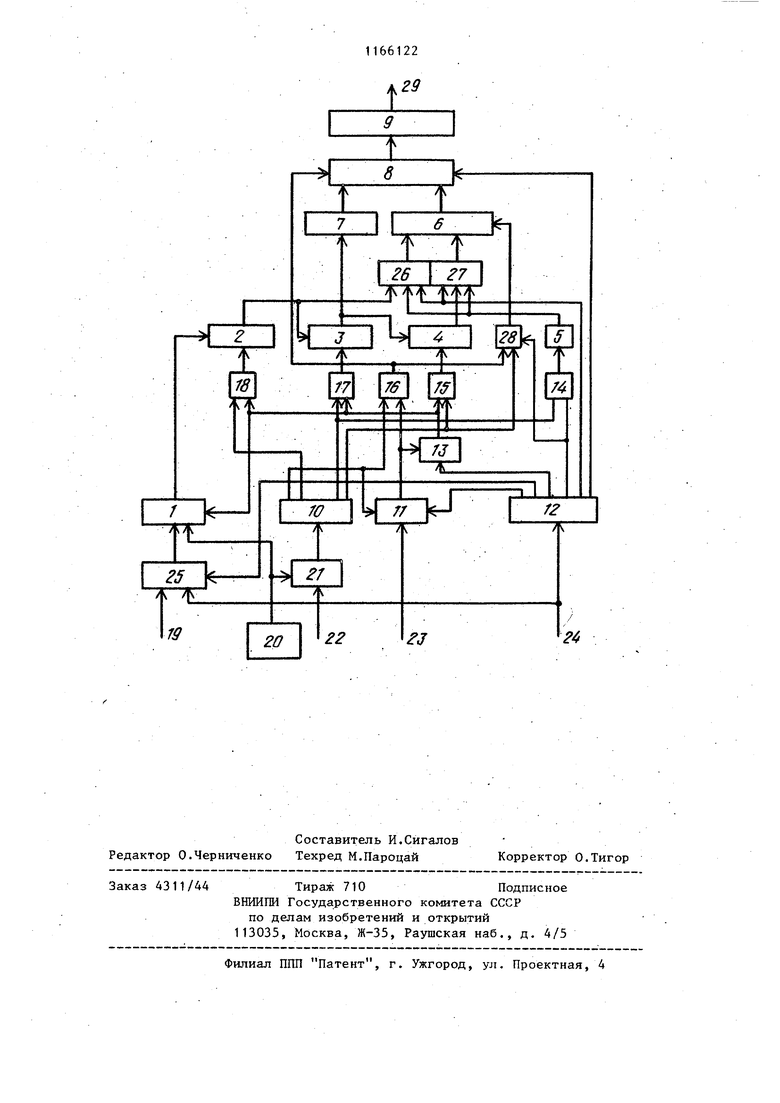

На чертеже представлена структурная схема устройства для отладки программ.

Устройства содержит регистр 1 адреса, регистры 2-4, счетчик 5 времени, буферный регистр 6, регистр 7 адреса, блок 8 оперативной памяти, регистр 9 считанной информации, элемент 10 задержки, триггер 11 записи переходов, регистр 12 управления, элемент ИЛИ 13, элементы И 14-18 вход 19 устройства, генератор 20 одиночных импульсов, элемент ИЛИ 21, вход 22 устройства, вход 23 устройства, вход 24 устройства, коммутаторы 25-27, триггер 23, выход 29 устройства.

, Регистр 1, представляющий собой счетчик-регистр, вьтолненный на микросхеме 133ИЕ7, своим выходом соединен с кодовым входом регистра 2, выход которого соединен с кодовым входом регистра 3, а его выход подключен к кодовому входу регистра 4. Счетчик 5 времени представляет собой последовательньй счетчик импульсов, собранный на статических триггерах, выход которого подключен к кЬдовым входам вторых каналов коммутаторов 26 и 27. Вход регистра 7 адреса соединен с выходом регистра 3, выходы регистров 6 и 7, вьшолненнык на микросхемах 133ТМ2, подключены соответственно к числовому и адресному входам блока оперативной памяти, а его выход соединен с входом регистра 9, выполненного на микросхемах 133ТМ2.

Выход 4 элемента 10 задержки соединен с входом 3 синхронизации триггера 11 записи перехода, выполненного на микросхеме 133ТМ2, и входом элемента И 16, а выход триггера 11 .подключен к первым входам элемента ИЛИ 13 и элемента И 16. Регистр 12

3

управления режимами работы устройства, представляющий собой запоминающий регистр на триггерах с параллельным вводом информации, выполнен на микросхемах 133ТМ2, первым выходом соединен с вторым входо триггера 11, вторым выходом соедине с вторым входом элемента ИЛИ 13, третьим выходом соединен с управляющими входами коммутаторов 26 и 27, пятым выходом регистр 12 управления подключен к режимному входу блока 8 оперативной памяти, в зависимости о потенциала которого определяется режим записи или считывания блока, шестым выходом регистр 12 соединен с управляющим входом коммутатора.25 Выход элемента 13 ИЛИ подключен к вторым входам элементов И 15, 17 и 18 и к входу управления записью регистра 1. Первый вход элемента И 14 соединен с первым, входом элемента И 17 и с вторым выходом элемента 10 задержки, а выход элемента И 14 подключен к входу счечика 5 времени. Первьй вход элемента И 15 соединен с первым выходом элемента 10 задержки и нулевым входом триггера 28, выход элемента И 15 подключен к входу управления записью регистра 4. Выход элемента И 16 подключен к входу сигнала выборки блока 8 оперативной памяти и к единичному входу 1 триггера 28. Элемент 17 своим выходом подключен к входу управления записью регистра 3. Первый вход элемента И 18 соединен с третьим выходом элемента 10 задержки, а его выход подключен к входу управления записью регистра 2. Вход 18 устройства соединен с кодовым йходом коммутатора 25. Генератор 20 одиночных импульсов своим выходом подключен к счетному входу регистра 1 и к первому входу элемента ИЛИ 21, выход которого подключен к входу элемента 10 задержки. Второй вход элемента ИЛИ 21 является входом 22 устройства. Вход 23 устройства является единичным входом триггера 11 записи переходов. Вход 24 устройства соединен с кодовым входом регистра 12 управления, кодовым входом коммутатора 25 и подсоединяется к внепшему наборному полю. Коммутаторы 26 и 27 своими кодовыми вхдами подключены к выходам регистров

2 и 4 соответственно, триггер 28 своим выходом подключен к входу, разрешения .записи регистра 6, а единичным входом 3 соединен с четвертым выходом регистра 12 управления. Устройство может.работать в четыр ех р ежимах з апис и информа ции

в блок памяти, а также в режиме счи тьшания из блока памяти. Режим работы определяется текущими задачами отладки программ и устанавливается с помощью соответствующих тумблеров на наборном поле, соединенном с регистром 12. управления и вторым кана5 лом коммутатора 25. Перед началом работы обнуляются регистры 1-4,6,7, счетчик 5, триггеры 11 и 28. Регистр 1 приема адреса при записи информации через кодовый вход 1 функциони20- рует как параллельный статический Ьегистр, а при подаче импульсов на счетный вход 2 - как последовательный счетчик. На вход 19 устройства поступает код со счетчика команд

СЦВМ, который в каждом цикле работы увеличивается на .единицу (СК+1 . Когда в СЦВМ вырабатываются усло вия программного перехода, то в машине вырабатывается сигнал Перезапись счетчика команд (Пер. СК) который сбрасывает в ноль счетчик команд СЦВМ, и после этого в него записьшается адрес команды, куда произошел переход.

5 Каждый цикл работы отлаживаемой СЦВМ сопровождается импульсом синхронизации (СИ). За один цикл из памяти СЦВМ производится считывание одной команды, адрес которой соответствует состоянию счетчика команд СЦВМ. СИ поступают на элемент. 10 задержки, где вырабатьюается последовательность из четырех импульсов, обеспечивается временная диаграмма

5 работы устройства.

Работа устройства в первом режиме заключается в фиксации блоком 8 оперативной памяти по каждому его адресу, совпадающему с адресом

0 данного перехода, кода, соответствующего адресам предьщущего и ... последующего переходов относительно данного. При этом регистр 12 управления с четвертого выхода вьвдает

5 сигнал запрета на второй вход элемента И 14 и на единичный вход триггера 28 сигнал, который постоянно его удерживает во взведенном состоянии, при этом с триггера выдается разрешение записи в регистр С третьего, четвертого, пятого и шест го выходов регистра 12 соответственно выдается разрешение на кодовые вхоДы коммутаторЪв 26, 27 и 25, а с пятогв выхода регистра - сигнал разрешающий запись в блок 8 оперативной памяти. После прихода из СЦВМ на вход 23 устройства сигнала Пер. СК через JBXOA 19 устройства и коммутатора25 в регистр 1 поступает адрес команды перехода. По сигналу СИ, поступающему из СЦВМ после прихода адреса через вход 22 устройства и элемент 21 ИЛИ, на элементе 10 задержки вырабатывается последовательность тактов и производится по ним последовательная перезапись информации из регистра 3 в регистр 4, из регис ра 2 в регистр 3 и из регистра 1 в регистр 2. Таким образом, после третьего такта в регистрах 2-4 нахо дятся адреса команд трех последних переходов, описанных со счетчика команд СЦВМ. По четвертому такту производится запись в ячейку блока 8 оперативной памяти по адресу, зап санному в регистре 7 из регистра 3 информации регистров 2 и 4 через коммутаторы 26 и 27 в левую и праву части регистра 6 кода. Кроме того, четвертый такт задним фронтом переводит триггер 11 в исходное состо яние, т.е. на регистр -1 и соответствующие схемы совпадения вьщается запрет до прихода нового сигнала Пер. СК. Работа устройства во втором режи ме заключается, в фиксации времени исполнения команд переходов. Сигналами меток времени являются синхроимпульсы, количество которых ра но количеству циклов, пройден ных СЦВМ, с момента включения данного режима. При этом с четвертого выхо да регистра 12 управления вьщается разрешение на второй вход элемента И 14 совпадения, а сигнал с вхо да триггера 28, удерживакнций его в взведенном состоянии, снимается, а с вькода на управляющие входы коммутаторов вьщается разрешение на входы коммутаторов 26 и 27. 6стальныё сигналы с выхода регистра 12 управления не меняются по сравнению с первым режимом. Таким образом, в этом режиме в каждом цикле работы СЦВМ содержимое счетчика 5 увеличивается на единицу вторым тактом элемента 10 задержки через элемент И 14 задним фронтом сигнала записи информации. В блок 8 оперативной памяти взводится триггер 28 и на регистр 6 вьщается разрешение записи информации из счетчика 5 через коммутаторы 26 и 27, которое соответствует времени поступления из СЦВМ адреса команды перехода, записанному в регистр 1. По первому такту следующего цикла триггер 28 сбрасывается и вьщает запрет на запись в регистр 6. При поступлении нового сигнала Пер. СК вторым тактом элемента 10 задержки через регистр 3 в регистр 7 Адреса записывается адрес команды перехода, время выборки которой из памяти СЦВМ записано уже в регистре 6 по предьщущему сигналу Пер. СК. Четвертым тактом информация регистра 6 записьшается в блок 8 оперативной памяти по адресу,записанному в регистре 7, и подается разрешение записи информации в-регистр 6 до первого такта следующего цикла. Работа устройства в третьем режиме заключается в фиксации времени выборки команд из памяти СЦВМ. При этом с первого выхода регистра 12 управления на вход триггера 11 вьщается сигнал, который удерживает его постоянно во выведенном состоянии и на регистр 1 подается постоянное разрешение. Остальные сигналы на выходах регистра 12 такие же как ив предьщущем режиме. При этом все адреса команд, поступающие на вход 19 устройства записываются в регистре 1 и при поступлении СИ переписываться из регистра 3 в регистр 7, определяя номер ячейки блока 8, в которую из счетчика 5 через регистр 6 записьтается время (номер цикла) выборки этой команды. Работа устройства в четвертом режиме заключается в фиксации адресов, откуда и куда произведен переход. ПРИ этом с второго йыхода регистра 12 управления вьщается сигнал разрешения на элемент ИЛИ 13, благодаря которому на элементы И 15, 16 и 17 и регистр 1 подается разрешение независимо от состояния триггера 1 1 , а с его первого выхода снима7ется сигнал, удерживающий во взведе , ном состоянии триггер 11, с третьег выхода вьщается сигнал на третьи входы коммутатора 26 и 27, который выдает разрешение на первые входы этих комм аторов. С четвертого выхода регистра 12 управления вьщаетс запрет на элемент И 14 и постоянное разрешение записи в регистр 6 через триггер 28. Поэтому, как и в предыдущем режиме, в регистрах 2-4 записьшаются адреса подряд идущих команд, однако триггер 11 вьщает разрешение на эле мент И 16 для прохождения четвертого такта для записи в блок 8 опера.тивной памяти информации только пос ле прихода сигнала Пер. СК. Поэто му в момент записи информации в блок В оперативной памяти в регистре 6 имеется адрес команды, откуда производится переход, а в регистре 2 - адрес команды, в которую производится переход. Остальные сигналы аналогичны первому режиму. В режиме считывания информации из блока 8 оперативной памяти с пятого выхода.регистра 12 управления вьщается сигнал считывания оператив ной памяти, а с шестого выхода сигнал на третий вход коммутатора 25, который вьщает разрешение на второй вход коммут1атора, к которому через вход 24 устройства подключает ся наборное поле. С первого выхода регистра 12 управления вьадается сигнал на второй вход триггера 11, 22.8 благодаря которому с выхода триггера 1-1 вьщается постоянное раэрешение на запись в регистр 1 и на элементы И 15-18 совпадения. При этом на наборном поле набирается тумблерами код, соответствующий исходному адресу ячейки блока 8 оперативной памяти.. . При подаче сигнала на генератор 20 одиночных импульсов вырабатьшается импульс, длительность которого превосходит длительность последовательности тактов, формируемую элементом 10 задержки. От переднего фронта этого импульса на элементе 10 задержки формируется последовательность тактов, которая организует перепись адресов в регистрах 2-4 как ив режиме отладки. Задним фронтом импульса, вырабатываемого генератором 20 и подаваемого на вход регистра 1, увеличивается содержимое регистра на единицу. От следующего импульса генератора 20 производится счить1вачие информации из оперативной памяти по адресу, записанному в регистре 3, и изменяется на единицу адреса в регистре 1. Таким образом, можно просмотреть информацию во-всех ячейках оперативной памяти на световом табло иди вывести ее на цифропечать. Технический эффект при использовании предлагаемого устройства по сравнению с известных заключается в повьш1ении достоверности отладки программ.,

29

1

| Устройство для отладки программ | 1974 |

|

SU598077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3673573, кл, 340-172.3 | |||

| опублик | |||

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-19—Подача