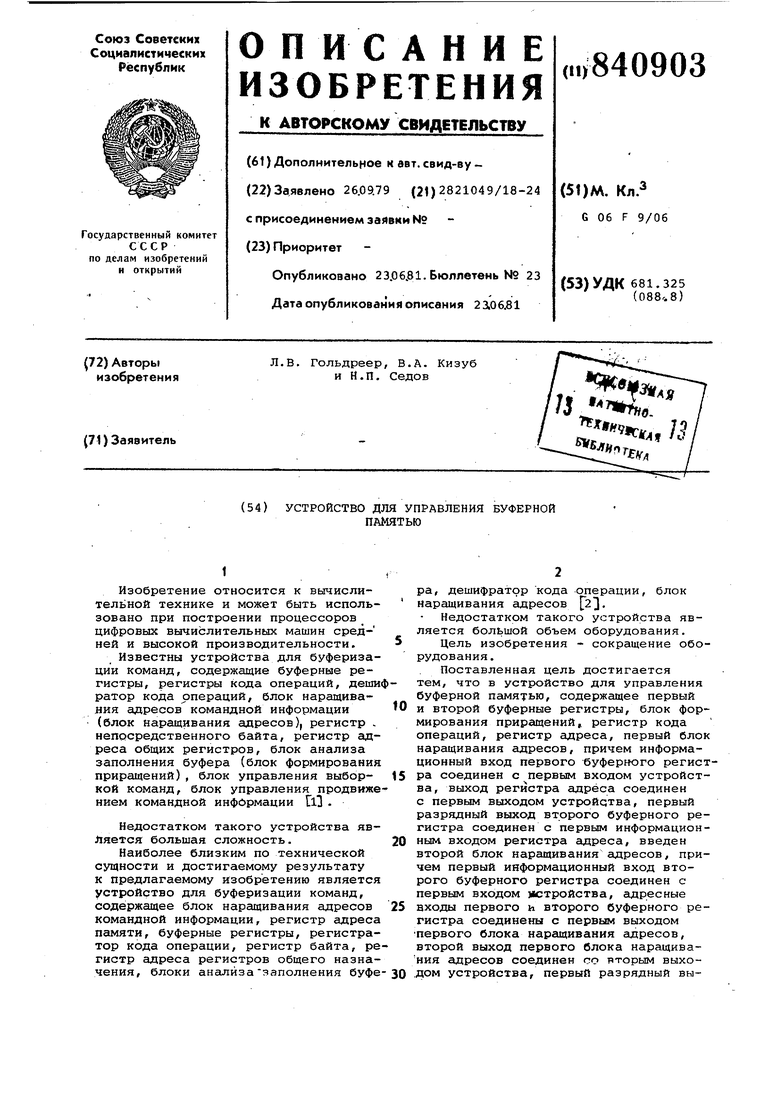

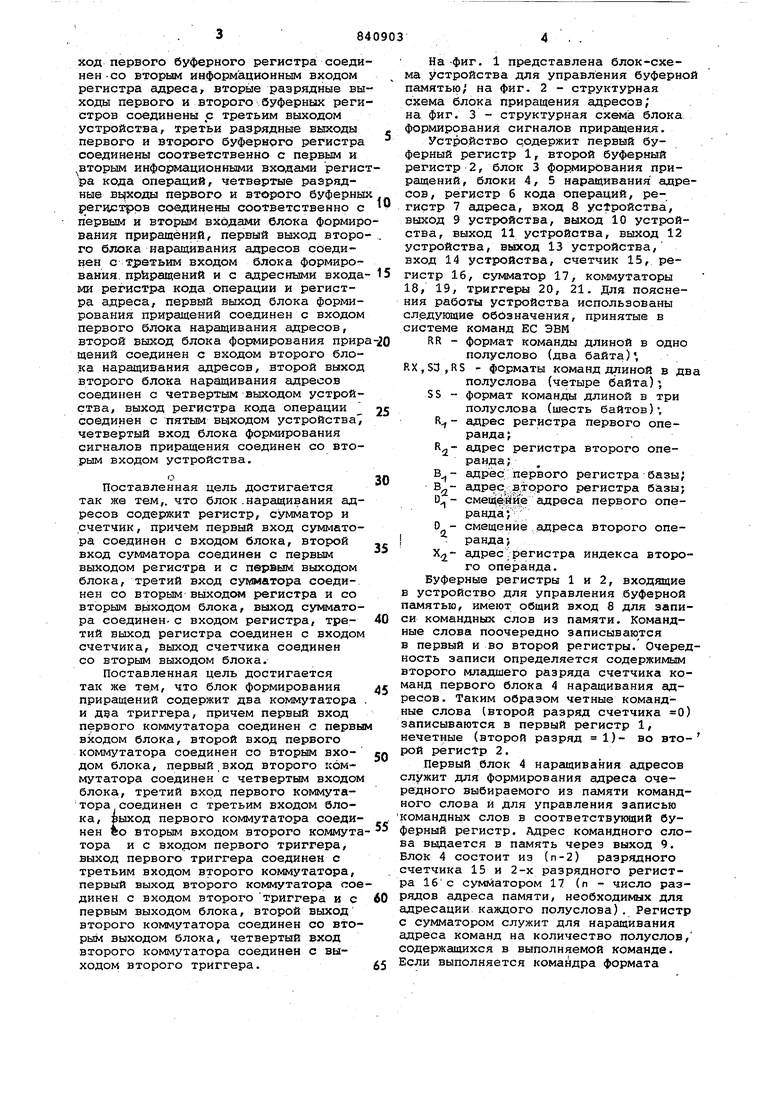

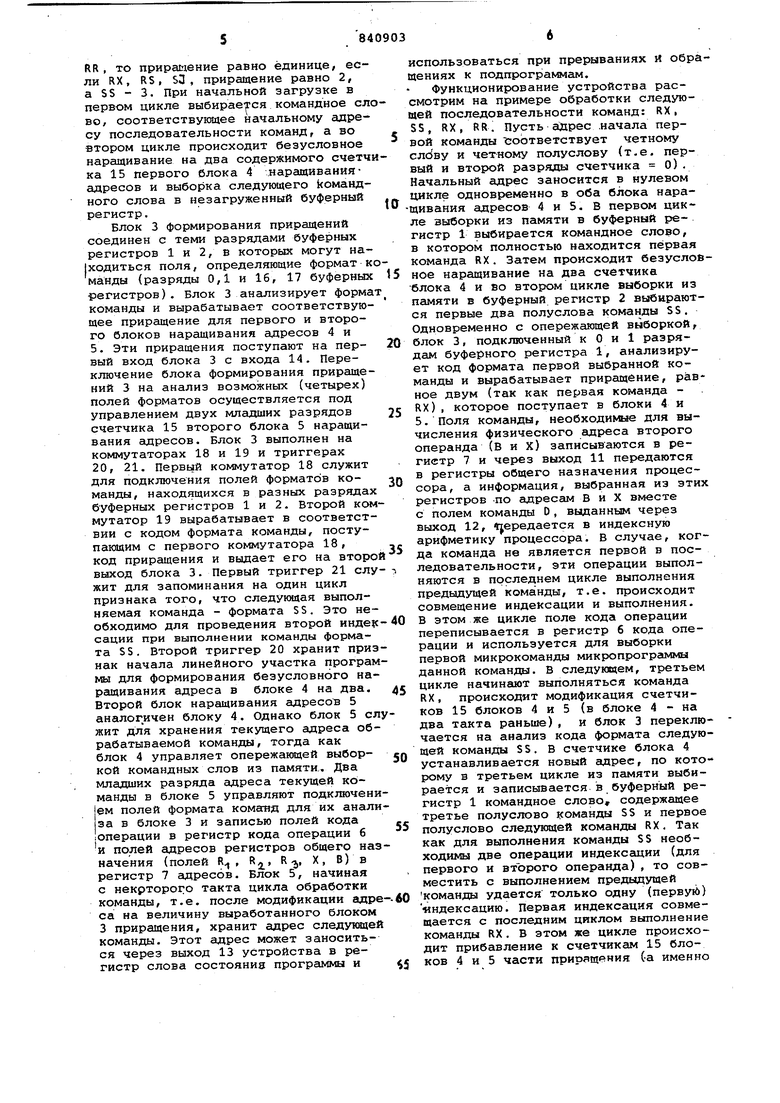

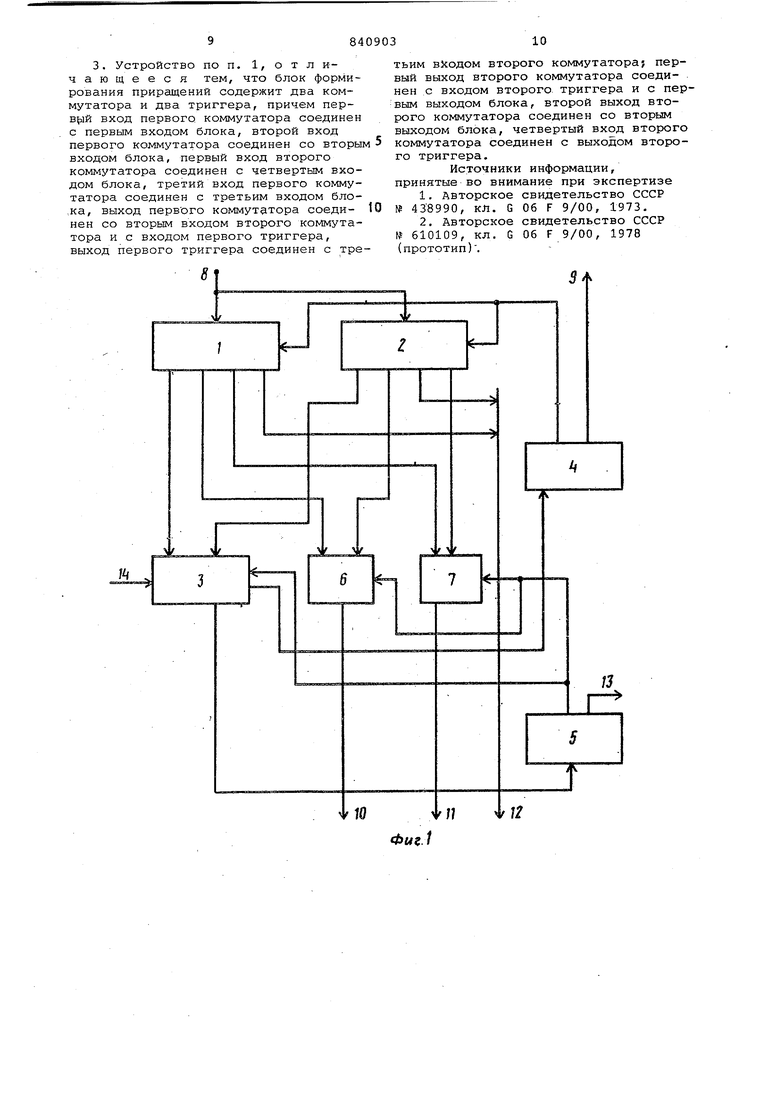

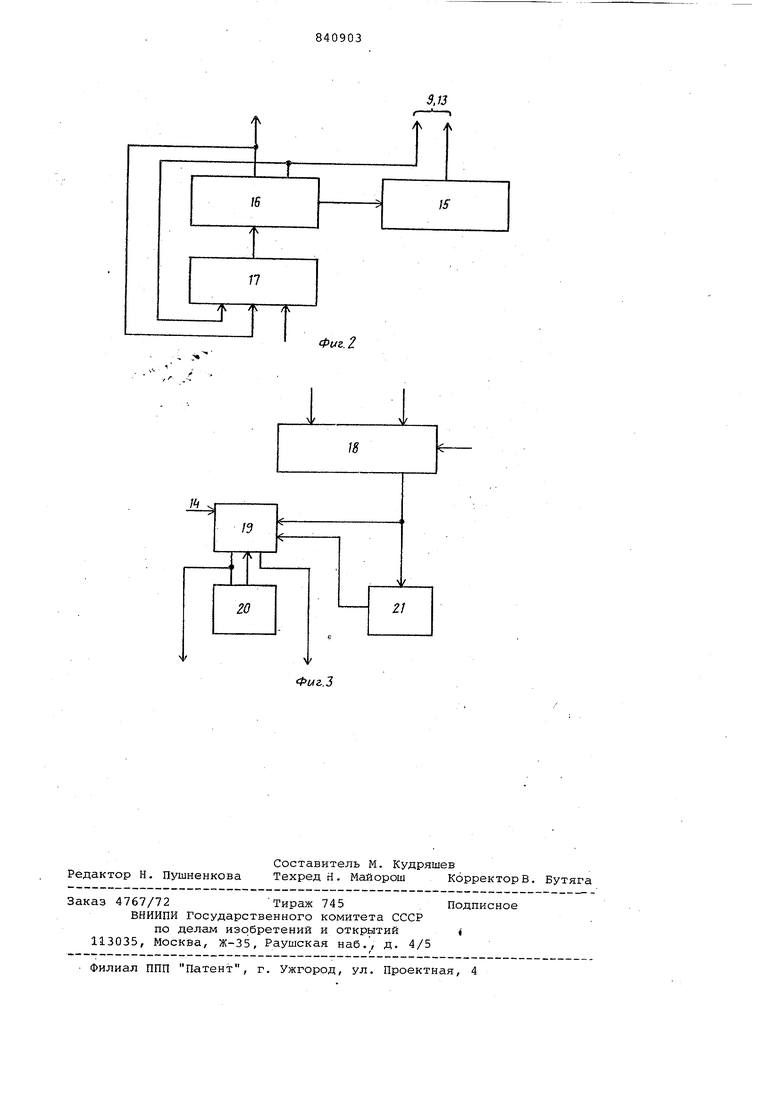

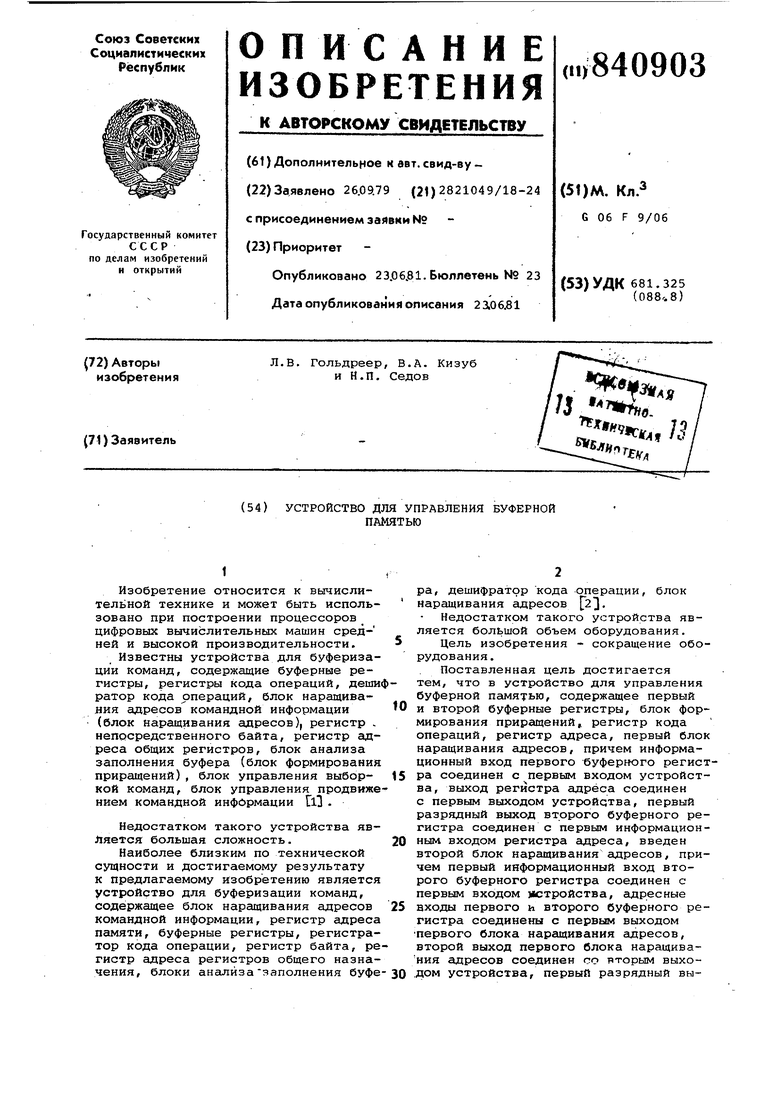

1 Изобретение относится к вычислительной технике и может быть использовано при построении процессоров цифровых вычислительных машин средней и высокой производительности. Известны устройства для буферизации команд, содержащие буферные регистры, регистры кода операций, деши ратор кода операций, блок наращивания адресов командной информации (блок наращивания адресов), регистр . непосредственного байта, регистр адреса общих регистров, блок анализа заполнения буфера (блок формирования приращений), блок управления выборкой команд, блок управления продвиже нием командной информации Ы Недостатком такого устройства явЛяется большая сложность. Наиболее близким по технической сущности и достигаемому результату к предлагаемому изобретению является устройство для буферизации команд, содержащее блок наращивания адресов командной информации, регистр адреса памяти, буферные регистры, регистратор кода операции, регистр байта, ре гистр адреса регистров общего назначения, блоки анализазаполнения буфе ра, дешифратор кода операции, блок наращивания адресов 2. Недостатком такого устройства является большой объем оборудования. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что в устройство для управления буферной памятью, содержащее первый и второй буферные регистры, блок формирования приращений, регистр кода операций, регистр адреса, первый блок наращивания адресов, причем информационный вход первого буферного регистра соединен с первым входом устройства, выход регистра адреса соединен с первым выходом устройства, первый разрядный выход второго буферного регистра соединен с первым информационным входом регистра адреса, введен второй блок наращивания адресов, причем первый информационный вход второго буферного регистра соединен с первым входом жзтройства, адресные входы первого и второго буферного регистра соединены с первым выходом первого блока наращивания адресов, второй выход первого блока наращивания адресов соединен со яторым выходом устройства, первый разрядный выход первого буферного регистра соеди нен -со вторым информационным входом регистра адреса, вторые разрядные вы ходы первого и второго буферных реги стров соединены с третьим выходом устройства, третьи разрядные выходы первого и второго буферного регистра соединены соответственно с первым и вторым информадионными входами регис ра кода операций, четвертые разрядные вцходад первого и второго буферны регистров соединены соответственно с первым и вторым входами блока формир вания приращений, первый выход второ го блока наращивания адресов соединен с третьим входом блока формирования, приращений и с адресными входа ми регистра кода операции и регистра адреса, первый ВЕЛХОД блока формирования приращений соединен с входом первого блока наращивания адресов, второй выход блока формирования прир щений соединен с входом второго блока наращивания адресов, второй выход второго блока наращивания адресов соединен с четвертым выходом устройства, выход регистра кода операции соединен с пятым выходом устройства четвертый вход блока формирования сигналов приращения соединен со вторым входом устройства. Поставленная цель достигается так же тем,, что блок .наращивания адресов содержит регистр, сумматор и счетчик, причем первый вход сумматора соединен с входом блока, второй вход сумматора соединен с первым выходом регистра и с первым выходом блока, третий вход су1(Матора соединен со вторым вьаходом регистра и со вторым выходом блока, выход сумматора соединен, с входом регистра, третий выход регистра соединен с входом счетчика, выход счетчика соединен со вторым выходом блока. Поставленная цель достигается так же те, что блок формирования приращений содержит два коммутатора и два триггера, причем первый вход первого коммутатора соединен с первы входом блока, второй вход первого коммутатора соединен со вторым входом блока, первый,вход второго коммутатора соединен с четвертым входом блока, третий вход первого коммутатора соединен с третьим входом блока, выход первого коммутатора соединен ео вторым входом второго коммута тора и с входом первого триггера, выход первого триггера соединен с третьим входом второго коммутатора, первый выход второго коммутатора сое динен с входом второго триггера не первым выходом блока, второй выход второго коммутатора соединен со вторым выходом блока, четвертый вход второго коммутатора соединен с выходом второго триггера. На -фиг. 1 представлена блок-схема устройства для управления буферной памятью/ на фиг. 2 - структурная схема блока приращения адресов; на фиг. 3 - структурная cxet/ta блока формирования сигналов приращения. Устройство срдержит первый буферный регистр 1, второй буферный регистр 2, блок 3 формирования приращений , блоки 4,5 наращивания адресов, регистр б кода операций, регистр 7 адреса, вход 8 устройства, выход 9 устройства, выход 10 устройства, выход 11 устройства, выход 12 устройства, выход 13 устройства, вход 14 устройства, счетчик 15, регистр 16, сумматор 17, коммутаторы 18, 19, триггеЕ л 20, 21. Для пояснения работы устройства использованы сл.едующие обозначения, принятые в системе команд ЕС ЭВМ RR - формат команды длиной в одно полуслово (два байта), P.X,S3,RS - форматы команд длиной в два полуслова (четыре байта); SS - формат команды длиной в три полуслова (шесть байтов); адрес регистра первого операндаR адрес регистра второго операнда; адрес первого регистра базы; адрес, второго регистра базы; смещение адреса первого операнда j О - смещение адреса второго опеI ранда) Х,- адрес/регистра индекса второго операнда. Буферные регистры 1 и 2, входшцие в устройство для управления буферной памятью, имеют общий вход 8 для записи командных слов из памяти. Командные слова поочередно записываются в первый и во второй регистры/ Очередность записи определяется содержимым второго младшего разряда счетчика команд первого блока 4 наращивания адресов . Таким образом четные командные слова (второй разряд счетчика 0) записываются в первый регистр 1, нечетные (второй разряд 1)- во второй perHctp 2. Первый блок 4 наращивания адресов служит для формирования адреса очередного выбираемого из памяти командного слова и для управления записью командных слов в соответствукнций буферный регистр. Адрес командного слова выдается в память через выход 9. Блок 4 состоит из (п-2) разрядного счетчика 15 и 2-х разрядного регистра 16 с сумматором 17 (п - число разрядов адреса памяти, необходимых для адресации каждого полуслова). Регистр с сумматором служит для наращивания адреса команд на количество полуслов, содержащихся в выполняемой команде. Если выполняется командра формата RR , то прирагпение равно единице, если RX, RS, S3, приращение равно 2, а SS - 3. При начальной загрузке в первом цикле выбирается командное ел во, соответствующее начальному адресу последовательности команд, а во втором цикле происходит безусловное наращивание на два содержимого счетч ка 15 первого блока 4 .наращиванияадресов и выборка следующего koмaндного слова в незагруженный буферный регистр. БЛОК 3 формирования приращений соединен с теми разрядами буферных регистров 1 и 2, в которых могут на|ходиться поля, определяющие формат к манды (разряды 0,1 и 16, 17 буферных регистров). Блок 3 ангшизирует форма команды и вырабатывает соответствующее приращение для первого и второго блоков наращивания гшресов 4 и 5. Эти приращения поступают на первый вход блока 3 с входа 14. Переключение блока формирования приращений 3 на анализ возможных (четырех) полей форматов осуществляется под управлением двух младших разрядов счетчика 15 второго блока 5 наращивания сщресов. Блок 3 выполнен на коммутаторах 18 и 19 и триггерах 20, 21, Первый коммутатор 18 служит для подключения полей форматов команды, находящихся в разных разрядах буферных регистров 1 и 2. Второй ком мутатор 19 вырабатывает в соответствии с кодом формата команды, поступающим с первого коммутатора 18, код приращения и выдает его на второ выход блока 3. Первый триггер 21 слу жит для запоминания на один цикл признака того, что следующая выполняемая команда - формата SS. Это необходимо для проведения второй инде|с сации при выполнении команды формата SS. Второй триггер 20 хранит приз нак начала линейного участка програм мы для формирования безусловного наращивания адреса в блоке 4 на два. Второй блок наращивания адресов 5 аналогичен блоку 4. Однако блок 5 сл жит для хранения текущего адреса обрабатываемой команды, тогда как блок 4 управляет опережающей выборкой командных слов из памяти, Два младших разряда адреса текущей команды в блоке 5 управляют подключени ем полей формата команд для их анали за в блоке 3 и записью полей кода операции в регистр кода операции б и полей адресов регистров общего наз 2. Ъ X ) 2 начения (полей R , R« , R регистр 7 адресов Блок 5, начиная с некрторого такта цикла обработки команды, т.е. после модификации адре са на величину выработанного блоком 3 приращения, хранит адрес следующей команды. Этот адрес может заноситься через выход 13 устройства в регистр слова состояния программы и использоваться при прерываниях И обращениях к подпрограммам. Функционирование устройства рассмотрим на примере обработки следующей последовательности команд: RX, SS, RX, RR. Пусть aiipec .начала первой команды тзоответствует четному сливу и четному полуслову (т.е. первый и второй разряды счетчика 0). Начальный адрес заносится в нулевом цикле одновременно в оба блока наращивания адресов 4 и 5. В первом цикле выборки из памяти в буферный регистр 1 выбирается командное слово, в котором полностью находится первая команда RX. Затем происходит безусловное наращивание на два счетчика блока 4 и во втором цикле выборки из памяти в буферный регистр 2 выбираются первые два полуслова команды SS. Одновременно с опережающей выборкой, блок 3, подключенный к О и 1 разрядам буферного регистра 1, анализирует код формата первой выбранной команды и вырабатывает приращение, равное двум (так как первая команда RX) , которое поступает в блоки 4 и 5. Поля команды, необходи№ е для вычисления физического адреса второго операнда (В и х) записываются в региетр 7 и через выход 11 передаются в регистры общего назначения процессора, а информация, выбранная из этих регистров -по адресам В и X вместе с полем команды D, выданным через выход 12, Чг ередается в индексную арифметику процессора. В случае, когда команда не является первой в последовательности, эти операции выполняются в последнем цикле выполнения предыдущей команды, т.е. происходит совмещение индексации и выполнения. В этом же цикле поле кода операции переписывается в регистр б кода операции и используется для выборки первой микрокоманды микропЕюграммы данной команды. В следующем, третьем цикле начинают выполняться команда RX, происходит модификация счетчиков 15 блоков 4 и 5 (в блоке 4 - на два такта раньше), и блок 3 переключается на анализ кода формата следующей команды SS. В счетчике блока 4 устанавливается новый адрес, по которому в третьем цикле из памяти выбирается и записывается в буферный регистр 1 командное слово, содержащее третье полуслово команды SS и первое полуслово следующей команды RX, Так как для выполнения команды SS необходимы две операции индексгихии (для первого и второго операнда) , то совместить с выполнением предыдущей команды удается только одну (первуй) индексацию. Первая индексация совмещается с последним циклом выполнение команды RX. В этом же цикле происходит прибавление к счетчикам 15 блоков 4 и 5 части приращения Са именно единицы), выработанного блоком 3. Вторая часть приращения (а именно, два добавляется в первом цикле выпол нения команды SS (т.е. в четвертом цикле). После этой модификации в счетчике блока 4 формируется адрес, соответствующий следующему командному слову. Это новое слово выбирается в пятом цикле в буферный регистр 2 и содержит второе полуслово команды RX и команду формата RR. Необходимо отметить, что выборка очередного команд ного слова и занесение в освободившийся буферный регистр происходит автоматически, как только сумма приращений, поступающих из блока 3, ста новится 0ольше двух (но не более, чем на единицу). В общем случае выбо ,ка может повторяться каждый цикл и :при постоянном адресе происходит пов торая запись информации в один и loi же буферный регистр (подтверждение информации). В последнем цикле выполнение команды SS происходит индексация ,адресо.в операндов следующей команды RX. Первое полуслово команды RX находится во второй половине буферного регистра 1, а второе полуслово - в пер вой половине регистра 2, и все необходимые для индексации поля доступны. ИндексациА адресов операндов будущей команды, когда она требуется, осуществляется всегда в последнем цикле выполнения текущей команды. Признак последнего цикла записывается в последней миг рокоманде микропрограммы каждой команды. Код операции, записанный в регистре 6, выдается с выхода 10 в блок центрально го управления процессора, В последнем цикле выполнения команды RX индексации не производится, так как следующая команда - RR. При анализе формата команды RR вырабатывается приращение, равное единице, блок 3, регистр б кода операций, регистр 7 адреса переключаются на одни полуслово дальше. Таким образом, устройство эффекти но решает задачу буферизации команд, обеспечивая согласование работы быст родействия процессора и менее быстродействующей памяти команд, совмещение выполнения текущей команды с индексацией следующей команды. Такая перекомпоновка связей устройст|а обеспечивает повышение быстродейст)зия обработки последовательно ти команд, записанных в ЗУ без промежутков , т.е. следующих друг за другом, и имеющих разный, но кратный полуслову формат, и существенно упро щает устройство. Формула изрбрЪтёния 1. Устройство для управления буферной памятью, содержащее первый и второй буферные регистры, блок формирования приращений, регистр кода операций, регистр адреса, первый блок наращивания адресов, причем информационный вход первого буферного ре- . гистра соединен с первым входом устройства, выход регистра адреса соединен с первым выходом устройства, первый разрядный выход второго буферного регистра соединен с первым информационным входом регистра адреса, отличающееся тем, что, с целью сокращения оборудования устройства, оно содержит второй блок наращивания адресов, причем информационный вход второго буферного регистра соединён с первым входом устройства, адресные входы первого и второго буферного регистра соединены с первым выходом первого блока наращивания адресов, второй выход первого блока наращивания адресов соединен со вторым выходом устройства, первый разрядный выход первого буферного регистра соединен со вторым информационным входом регистра адреса, вторые разрядные выходы первого и второго буферных регистров соединены с третьим выходом устройства, третьи разрядные выходы первого и второго буферного регистра соединены соответственно с первым и вторым информационными входами регистра кода операций, четвертые разрядные выходы первого и второго буферных регистров соединены роответственно с первым и вторым входами блока формирования :прира1аений, первый выход второго блока наращивания адресов соединен с третьим входом блока формирования приращений и с адресными входами-регистра кода операции и регистра адреса, первый выход блока формирования приращений соединен с входом первого блока наращивания адресов, второй выход блока формирования приращений соединен с входом второго блока нарсццивания адресов, второй выход второго блока наращивания адресов соединен -с четвертым выходом устройства, выход регистра кода операции соединен с пятым выходом устройства, четвертый вход блока формирования сигналов приращения соединен со вторым входом устройстваi . . 2. Устройство по п. 1, о т л ичающееся тем, чтр, блок наращивания адресов содержит регистр, сумматор и счетчик, причем первый вход сумматора соединен с входом блока, второй вход сумматора соединен с .первым выходом регистра и с первым выходом блока, третий вход cjwMaTopa соединен со вторым выходом регистра и со вторым выходом блока, выход сумматора соединен с входом регистра, третий выход регистра соединен с входом счетчика, выход счетчика соединен со вторым выходом блока. 3. Устройство по п. 1, о т л ичающееся тем, что блок формирования приращений содержит два коммутатора и два триггера, причем перв з1й вход первого коммутатора соединен с первым входом блока, второй вход первого коммутатора соединен со вторы входом блока, первый вход второго коммутатора соединен с четвертым входом блока, третий вход первого коммутатора соединен с третьим входом бло,ка, выход первого коммутатора соединен со вторым входом второго коммутатора и с входом первого триггера, выход первого триггера соединен с тре тьим входом второго коммутатора; первый выход второго коммутатора соединен с входом второго триггера и с первым выходом блока, второй выход второго ко2 №1утатора соединен со вторым выходом блока, четвертый вход второго коммутатора соединен с выходом второго триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 438990, КЛ. G Об F 9/00, 1973. 2.Авторское свидетельство СССР № 610109, КЛ. G 06 F 9/00, 1978 (прототип).

16

}S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для распаковки команд | 1987 |

|

SU1464157A1 |

| Устройство выборки команд процессора | 1987 |

|

SU1481758A1 |

| Устройство выборки команд процессора | 1986 |

|

SU1410028A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

Т

Фиг. 2

Авторы

Даты

1981-06-23—Публикация

1979-09-26—Подача