дов устройства, второй адресный вход подключен к второму выходу блока синхронизации выдачи байтов состояни ,и третьему выходу узла синхронизации вьщачи собственного адреса, а группа выходов - к первой группе входов узла канальн,ь1х передатчиков, первая и вторая группы выходов которого являются соответственно группой абонентских информационных выходов устройства и группой абонентских выходо сигналов идентификации устройства, а вторая группа входов соединена с первым выходом узла синхронизации передачи данных, третьим выходом узла синхронизации вьщачи байтов состояния, первым выходом узла синхронизации вьщачи собственного адреса и первым и вторым выходами узла дешифрации команд выборки, первый выход которого подключен к второму входу узла синхронизации вьщачи собственного адреса.

2.Устройство по п.1,отличающееся тем,что узел синхронизации вьщачи собственного адреса содержит два триггера, два формирователя импульса,, элемент задержки, элемент ИЛИ, два элемента НЕ и два . элемента И, причем вход установки первого триггера подключен через первый формирователь импульса к выходу первого элемента И, а вход сброса к выходу элемента ИЛИ и входу сброса второго триггера, вход установки которого через последовательно соединенные элемент задержки и торой формирователь импульса соединен с выходом первого триггера, первые входы первого и второго элементов И соединены с вторым входом узла, второй вход первого элемента И подключен к выходу первого элемента НЕ, вход которого и второй вход второго элемента И образуют группу входов узла, первый вход элемента ИЛИ является первым входом узла, а второй , вход подключен к выходу второго элемента И и через второй элемент НЕ к второму выходу узла, выходы первого и второго триггеров являются соответственно третьим и первым выходами узла.

3.Устройство ПОП.1, отличающееся тем, что узел синхронизации вьщачи байтов состояния содержит два триггера, два элемента НЕ три формирователя импульса, три элемента ИЛИ, элемент задержки и три элемента И, причем первый вход первого элемента ИЛИ подключен через последовательно соединенные первые формирователь импульса и элемент НЕ к шестому входу узла, второй вход - через второй формирователь импульса к четвертому входу узла и входу второго элемента НЕ, а выход - к входу установки первого триггера, вход сброса которого подключен к входу сброса второго триггера, первому выходу узла и выходу второго элемента ИЛИ, первый вход которого является вторьм входом узла, а второй вход подключен к выходу первого элеjvieHTa И, ;первьй и второй входы которого являются соответственно третьим и первым входами узла, первые входы второго и третьего элементов И являются соответственно пятым и седьмым входами узла, вторые входы соединены с выходом первого триггера и вторым выходом узла, а выходы соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого через последовательно соединенные третий формирователь импуль;са и элемент задержки подключен к v входу установки второго триггера, выход которого является третьим выходом узла третий вход третьего элемента И соединен с выходом второго элемента НЕ.

4. Устройство ПОП.1, отличающееся тем, что узел согла сования формата данных содержит два триггера, переключатель формата, генератор тактовых импульсов, делитель частоты, два элемента НЕ, восемь элементов И, четыре элемента ИЛИ и два формирователя импульсов, причем выходы первого и второго элементов И соединены соответственно с входами установки первого и второго триггеров, входы сброса которых соединены с выходом первого элемента ИЛИ, выход второго элемента ИЛИ является третьим выходом узла, а первый и второй входы подключены соответственно к выходам третьего и четвертого элементов И, первые входы которых соединены с четвертым входом узла, вторле входы - соответственно с первыми входами пятого и шестого элементов И |и первым и вторым выходами переключателя формата,, вход которого соединен с нулевой шиной источника питання, третий вход третьего элемента И соединен с выходом генератора тактовых импульсов и через делитель частоты с третьим входом четвертого элемента И, второй вход пятого элемента И соединен с первьш входом узла и через первый формирователь импульса - с первым входом третьего элемента ИЛИ, вторым входом подключенного через второй формирователь импульса к прямому выходу второго триггера, а выходом - к второму входу шестого элемента И, первый и второй входы седьмого и восьмого элемен тов И соединены соответственно с пря мым и инверсным выходами второго триггера, вторые входы - с четвертым входом узла, а выходы образуют второй ;выход узла, первый и второй входы четвертого :элемента ИЛИ соединены соответственно с выходами пятого и шестого элементов И, а выход является первым выходом узла, первьй вход первого элемента И является третьим входом узла, второй вход соединен с вторым выходом переключателя формата, перзьш вход первого элемента ИЛИ соединен через первьш элемент НЕ с пер вым входом узла, второй вход является пятым входом узла,первый вход второго элемента И соединен с вторым входом . узла и через второй элемент НЕ с треть- ; им входом первого элемента И, а второй ; вход- с выходом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1986 |

|

SU1363226A1 |

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Имитатор канала | 1987 |

|

SU1467555A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕ.НИЯ ДАТЧИКА ИНФОРМАЦИИ С ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ, содержащее узел дешифрации команд общего сброса, выходом соединенный с входом сброса узла дешифрации команд выборки, первьй выход которого подключен к первому входу узла синхронизации передачи данных, вторым выходом соединенного с первым выходом узла согласования формата данных, второй вьрсод и первый вход которого соединены соответственно с первым адресным входом выходного коммутатора информации и входом готовности устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены узел синхронизации вьщачи собственного адреса, узел синхронизации вьвдачи байтов состояния, узел канальных приемников и узел канальных передатчиков, причем первая и вторая группы входов узла канальных приемников являются соответственно группами- канальных информационных входов и входов сигналов идентификации устройства, а первая и вторая группы выходов подключены соответственно к первой и второй группам входов узла дешифрации команд выборки, группы входов блока дешифрации команд общего сброса и узла синхронизации выдачи собственного адреса, первый вход узла вьадачи байтов состояния и вторые входы узла согласования формата данных и узла синхронизации передачи данных соединены с второй группой выходов узла канальных приемки- ков, третий выход узла согласования формата данных является выходом пуска датчика устройства, а третий, четвертый и пятый входы соединены соотi ветственно с первьм и вторым выходами и с третьим входом узла синхрони(Л зации передачи данных, выходом узла дешифрации команд общего сброса, первым входом узла синхронизации вьщачи собственного адреса и вторым входом узла синхронизации вьщачи байтов состояния, третий вход которого соединен с первым выходом узла дешифрации команд выборки и первым входом узла 00 00 дешифрациикоманд общего сброса, вторым входом подключенного к инел формационному входу выходного коммусо татора информации и к второму выходу о узла синхронизации передачи данных, четвертый вход и второй и третий выходы которого подсоединены соответственно к первому выходу и четвертому и пятому входам узла синхронизации вьщачи байтов состояния, шестым и седьмым входами соединенного соответстбенно с первым и вторьм выходами узла синхронизации выдачи собственного адреса, группа информационных входов выходного коммутатора информации является группой информационных вхо

1

Изобретение отйЪсится к вычислительной технике и предназначено для ввода данных ЭВМ серии ЕС ЭВМ от несистемных внешних устройств - источников информации, представляющих информацию в двоичном коде.

Известно устройство для сопряжения внешних устройств с каналом ввода-вывода, содержащее вентили, инверторы, приемник, ключ, генератор пуска и готовности, триггеры ввода и вывода, счетчик и регистр Щ.

Недостаток устройства состоит в том, что оно требует больших затрат оборудования для своей реализации.

Наиболее близким к изобретению по технической сущности, является устройство для сопряжения датчика информации с каналом вычислительной машины, содержащее блок приема и преобразования форматов, блок контроля готовности и блок синхронизации, первые входы которых соединены с соответствукяцими выходами датчика информации, блок формирования номера подканала, блок окончания работы, блок сбоев и блок опроса указателей, первые выходы которых соединены с соответствующими входами канала вычислительной машины, первые входы блока формирования запроса и блока формирования запроса подключены к второму выходу блока приема и преобразования

форматов, третьим выходом соединенного с первым входом блока сбоев, вторым входом - с первым выходом блока синхронизации, второй выход которого

подключен к соответствующим входам блока формирования номера подканала и блока окончания работы, выходы канала вычислительной машины соединены соответственно с входами блоков пуска

и окончания работы, блока синхронизации, блока сбоев и блока приема и : преобразования форматов 2J .

Недостатком известного устройства являются большие затраты аппаратуры.

Целью изобретения является сокращение аппаратурных затрат.Поставленная цель достигается тем, что в устройство, содержащее

узел дешифрации команд общего сброса, выходом соединенный с входом сброса узла дешифрации команд выборки, первьй выход которого подключен к первому входу узла синхронизации передачи

данных, вторым выходом соединенного с первым выходом узла согласования формата данных, второй выход и первый вход которого соединены соответственно с первым адресным входом

выходного коммутатора информации и входом готовности устройства, введены узел синхронизации вьздачи байтов состояния, узел канальных приемников и узел канальных передатчиков, причем первая и вторая группы входов узла канальных приемников являются соответственно группами канальных информационных входов и входов сигналов идентификации устройства, а первая и вторая группы выходов подключены соответственно к первой и второй группам вх8дов узла дешифрации команд выборки, группы входов блока дешифрации команд общего сброса и узла Q синхронизации выдачи собственного адреса, первый вход узла выдачи байтов состояния и вторые входы узла согласования формата данных и узла синхронизации передачи данных соединены с , второй группой выходов узла .канальных приемников, третий вЪкрд узла согласования формата данных является выходом пуска датчика устройства, а Третий, четвертьш и пятый входы соеди- jn нены соответственно с первым и вторым выходами и с третьим входом узла синхронизации передачи данных, выходом узла дешифрации команд общего сброса, первым входом узла синхронизации вы- 25 дачи собственного адреса и вторым входом узла синхронизации выдачибайтов состояния, третий вход которого соединен с первым выходом узла дешифрации команд выборки и первым входом узла дешифрации команд общего сброса, вторым входом подключенного к информационному входу выходного коммутатора информации и к второму выходу узла синхронизации передачи данных, четвертый вход и второй и тре- 35 тий выходы которого подсоединены соответственно к первому выходу и четвертому и пятому входам узла синхронизации вьщачи байтов состояния, шестым и седьмым входами соединенного 40 соответственно с первым и вторым выходами узла синхронизации выдачи собственного адреса, группа информационных входов выходного коммутатора информации является группой информаци- 45 онных входов устройства, второй адресньй вход подключен к второму выходу блока синхронизации выдачи байтов состояния и третьему выходу узла синхронизации выдачи собственного 50 адреса, а группа .выходов - к первой группе входов узла канальных передатчиков, первая и вторая группы выхо-дов которого являются соответственно группой абонентских, информационньк 55

выходов устройства и группой абонентских выходов сигналов идентификации

устройства, а вторая группа

входов соединена с первым выходом узла синхронизации передачи данных, третьим выходом узла синхронизации выдачи байтов состояния, первым выходом узла синхронизации выдачи собственного адреса и первым и вторым выходами узла дешифрации команд выборки, первьш выход которого подключен к второму входу узла синхронизации выдачи собственного адреса.

Узел синхронизации выдачи собственного адреса содержит два тригге ра, два формирователя импульса, элемент задержки, элемент ИЛИ, два элемента НЕ и два элемента И, причем вход установки первого триггера подключен через первый формирователь импульса к выходу первого элемента И а вход сброса - к выходу элемента ИЛИ и входу сброса второго триггера, вход установки которого через последовательно соединенные элемент задержки и второй формирователь импульса соединен с выходом первого триггера, первые входы первого и второго элементов И соединены с вторым входом узла, второй вход первого элемента И подключен к выходу первого элемента НЕ, вход которого и второй вход второго элемента И образуют группу входов узла, первый вход элемента ИЛИ является первым входом узла, а второй вход подключен к выходу второго элемента И и через второй элемент НЕ к второму выходу узла, выходы первого и второго триггеров являются соответственно третьим и первым выходами узла.

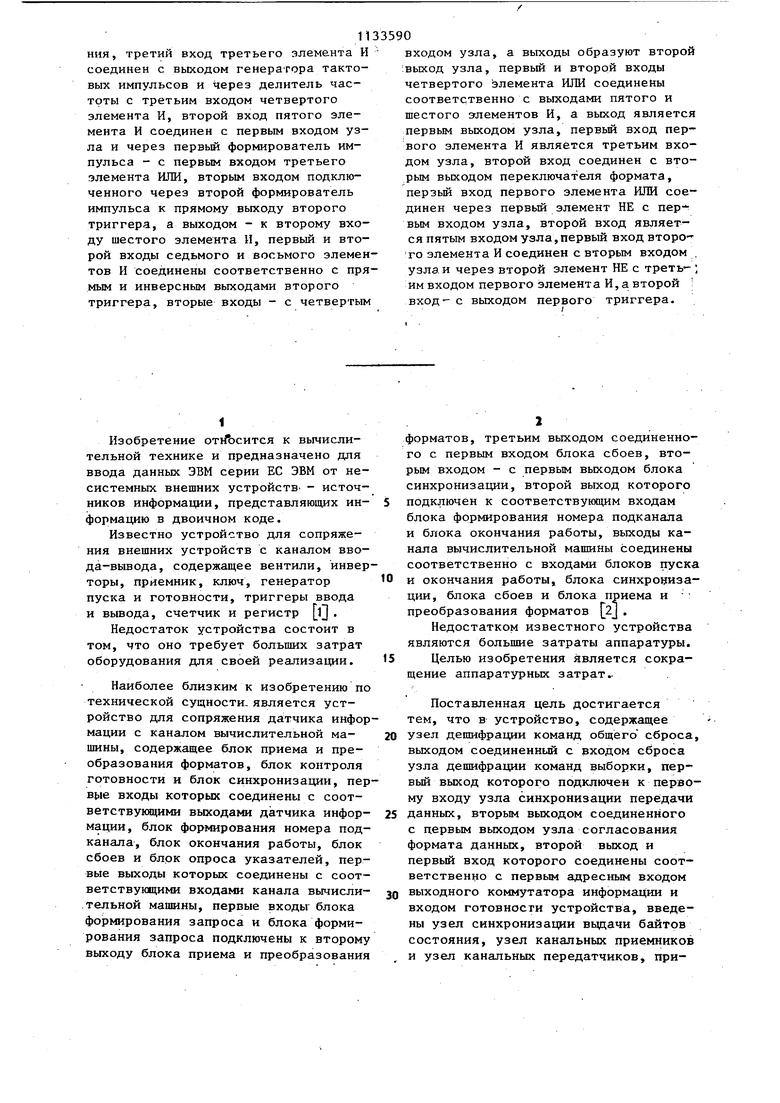

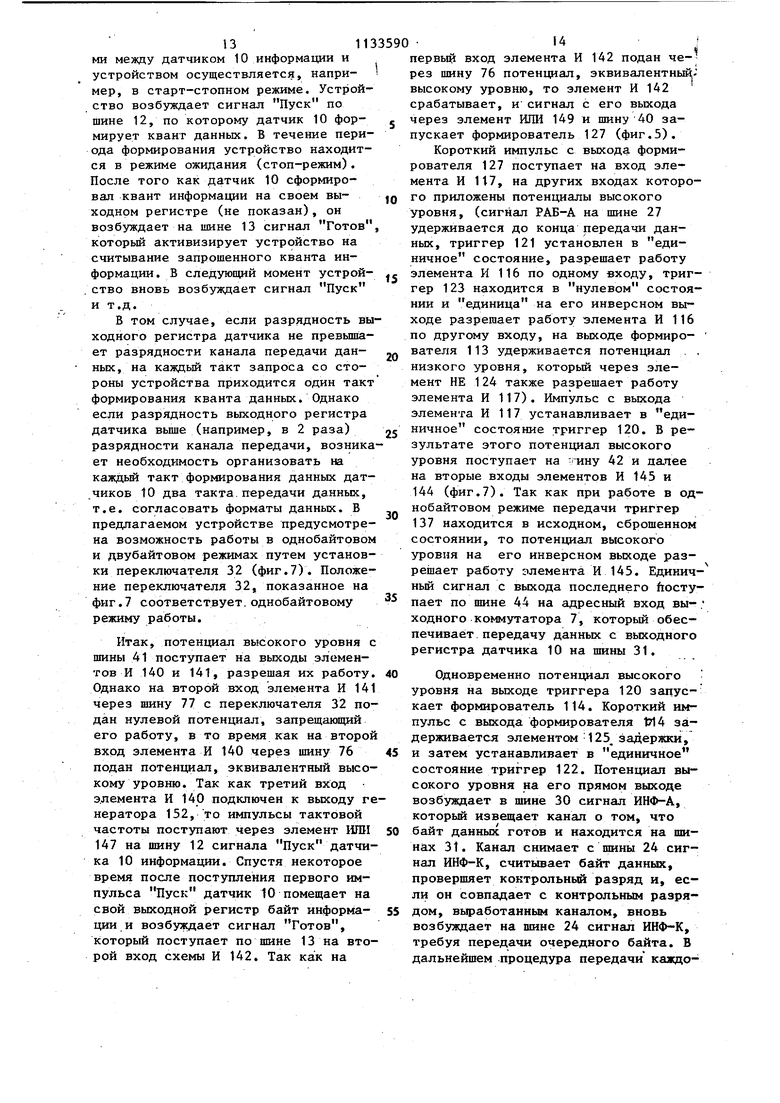

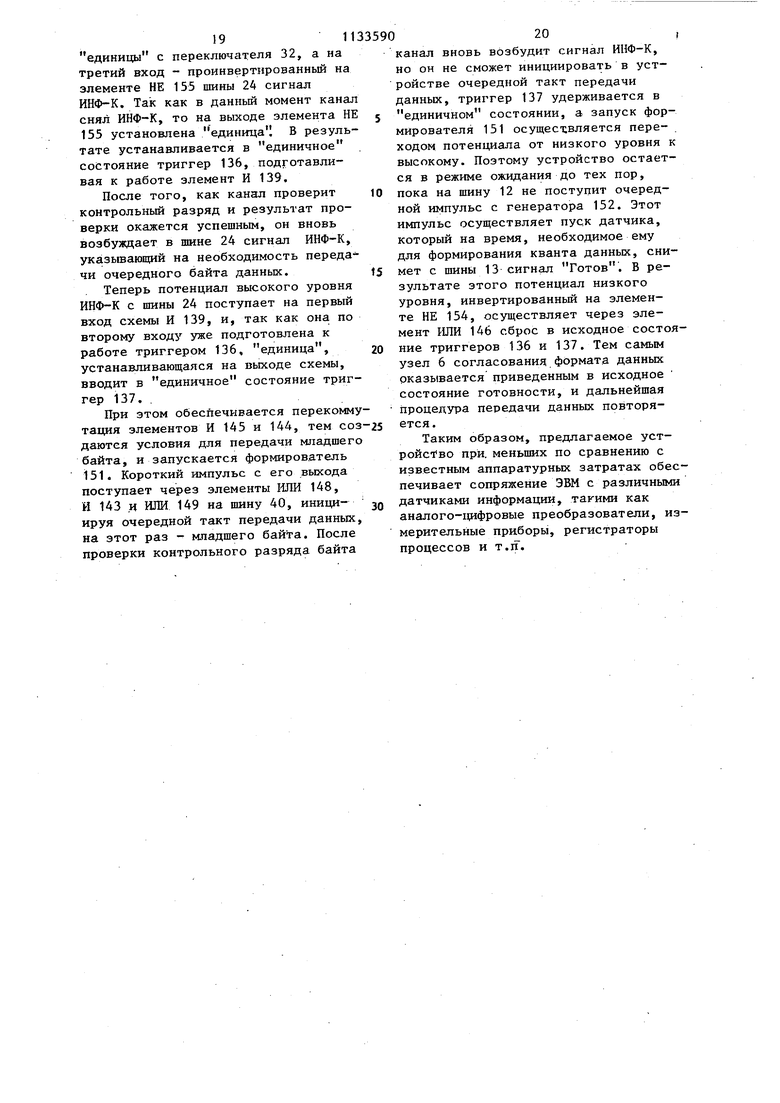

Узел синхронизации вьщачи байтов состояния содержит два триггера, два элемента НЕ, три формирователя импульсов, три элемента ИЛИ, элемент задержки и три элемента И, причем первый вход первого элемента ИЛИ подключен через последовательно соединенные первые формирователь импульса и элемент НЕ к шестому входу узла, второй вход - через второй формирователь импульса к четвертому входу узла и входу второго элемента НЕ, а выход - к входу установки первого триггера, вход сброса которого подключен к ВХОДУ сброса второго триггера, первому выходу узла и выходу второго элемента ИЛИ, первый вход которого является вторым входом узла, а второй вход подключен к выходу первого элемента И, первый и второй .511 входы которого являются соответствен но третьим и первым входами узла, первые ВХОД1Л второго и третьего элементов И - соответственно пятым и седьмым входами узла, вторые входы соединены с выходом первого триггера и вторым выходом узла, а выходы - со ответственно с первым и вторым входами третьего элемента НИИ, выход которого через последовательно соединенные третий формирователь импуль са и элемент задержки подключен к входу установки второго триггера, выход которого является третьим выходом узла, третий вход третьего элемента И соединен с выходом второго элемента НЕ. Узел согласования формата данных содержит два триггера, переключатель формата, генератор тактовых импульсов, делитель частоты, два элемента НЕ, восемь элементов И, четыре элемента ИЛИ и два формирователя импульсов, причем вьгходы первого и второго элементов И соединены соответственно с входами установки первого и второго триггеров, входы сбро са которых соединены с выходом первого элемента ИЛИ, выход второго элемента ИЛИ является третьим выходом узла, а первый и второй входы подклю чены соответственно к выходам третье го и четвертого элементов И, первые входы которых соединены с четвертым входом узла, вторые входы - соответственно с первыми входами пятого и шестого элементов И и первым и вторы выходами переключателя формата, вход которого соединен с нулевой шиной ис точника питания, третий вход третьего элемента И - с выходом генератора тактовых импульсов и через делитель частоты с третьим входом четвертого элемента И, второй вход пятого элемента И - с первым входом узла и через первый формирователь импульса с первым входом третьего элемента ШШ, вторым входом подключенного через второй формирователь импульса к прямому выходу второго триггера, а выхо дом - к второму входу шестого элемен та И, первый и второй входы седьмого и восьмого элементов И соединены соответственно с прямым и инверсным выходами второго триггера, вторые входы - с четвертым входом узла, а выходы образуют второй выход узла, первый и второй входы четвертого :,элемента ИЛИ соединены соответственно с выходами пятого и шестого элемен- ; тов И, а выход является первым выходом узла, первый вход первого элемента И - третьим входом узла, второй вход соединен с вторым выходом переключателя формата, первьпЧ вход первого элемента ИЛИ - через первый элемент НЕ с первым входом узла, второй вход является пятым входом узла, первый вход второго элемента И соединен с вторым входом узла и через второй элемент НЕ с третьим входом первого элемента И, а второй вход - с выходом первого триггера. На фиг.1 представлена блок-схема устройства, на фиг.2-8 - функциональные схемы узла дешифрации команд выборки, узла синхронизаюри выдачи собственного адреса, узла синхронизации вьщачи байтов состояния, узла синхронизации передачи данных, узла дешифрации команд общего сброса, узла согласования формата данных, выходного коммутатора информации соответственно, на фиг.9 - блок-схема алгоритма управления устройством на строке ЭВМ. Устройство (фиг.1) содержит узел 1 дешифрации команд выборки, узел 2 синхронизации выдачи собственного адреса, узел 3 синхронизащш выдачи байтов состояния, узел 4 синхронизации передачи данных, узел 5 дешифрации команд общего сброса, узел 6 согласования формата данных, выходной коммутатор 7 данных, узел 8 канальных усилителей-приемников, узел 9 канальных усилителей-передатчиков, датчик 1О информации, информационный вход 11 устройства, шину 12 выхода пуска датчика устройства, шину 13 входа готовности устройства, группы абонентских информационных выходов 14 и абонент,,3 выходов 15 сигналов идентификации устройства, группы канальных информационных.входов 16 и канальных входов 17 сигналов идентификации устройства, первую группу выходов 18 и шины 19-25 второй группы выходов узла 8 канальных усилителей-приемников, шины 26-30 первой группы входов и вторую группу выходов 31 узла 9 канальных усилителей-передатчиков, пе-г реключатель 32 формата узла 6, шины 33-44 связей между узла устройства, шины 45-52 группы входов 18, шины 53-61 группы выходов 31 и шины 62-77i

информационного входа 11, шины 78 и 79 выходов переключателя 32.

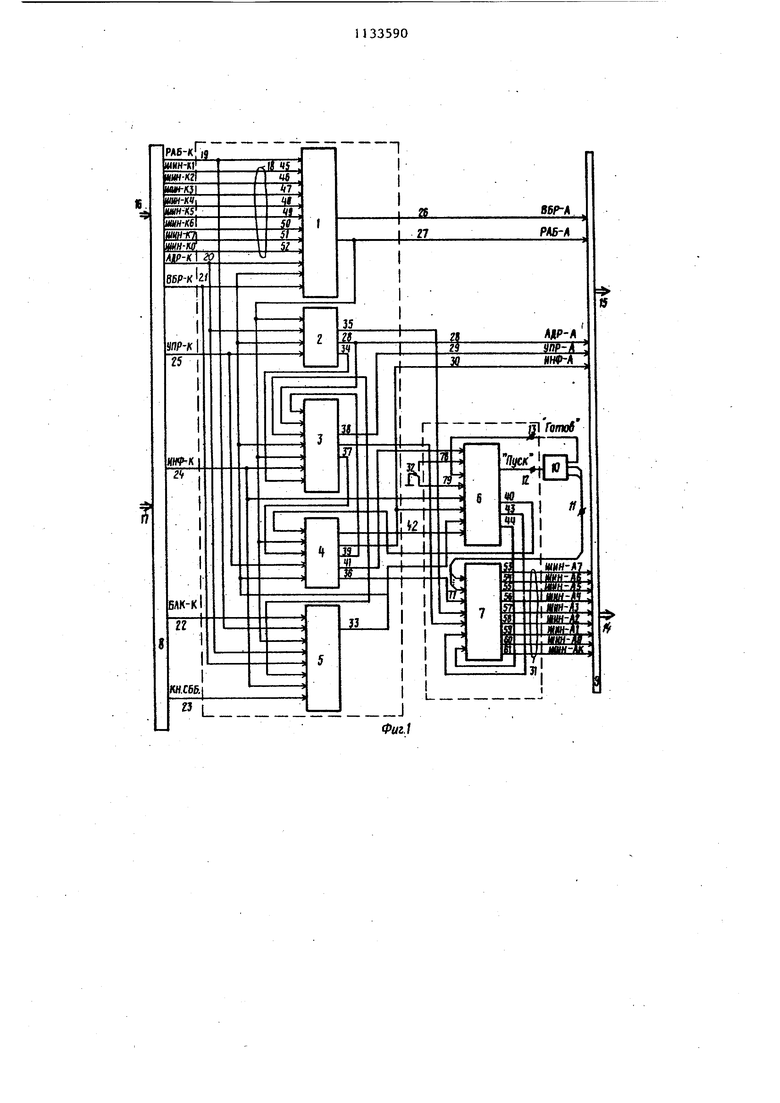

Узел 1 дешифрации команд выборки содержит (фиг.2) триггеры 80 и 81, элементы И 82-85, элементы НЕ 86-f, 86 и 87, элемент ИЛИ 88.

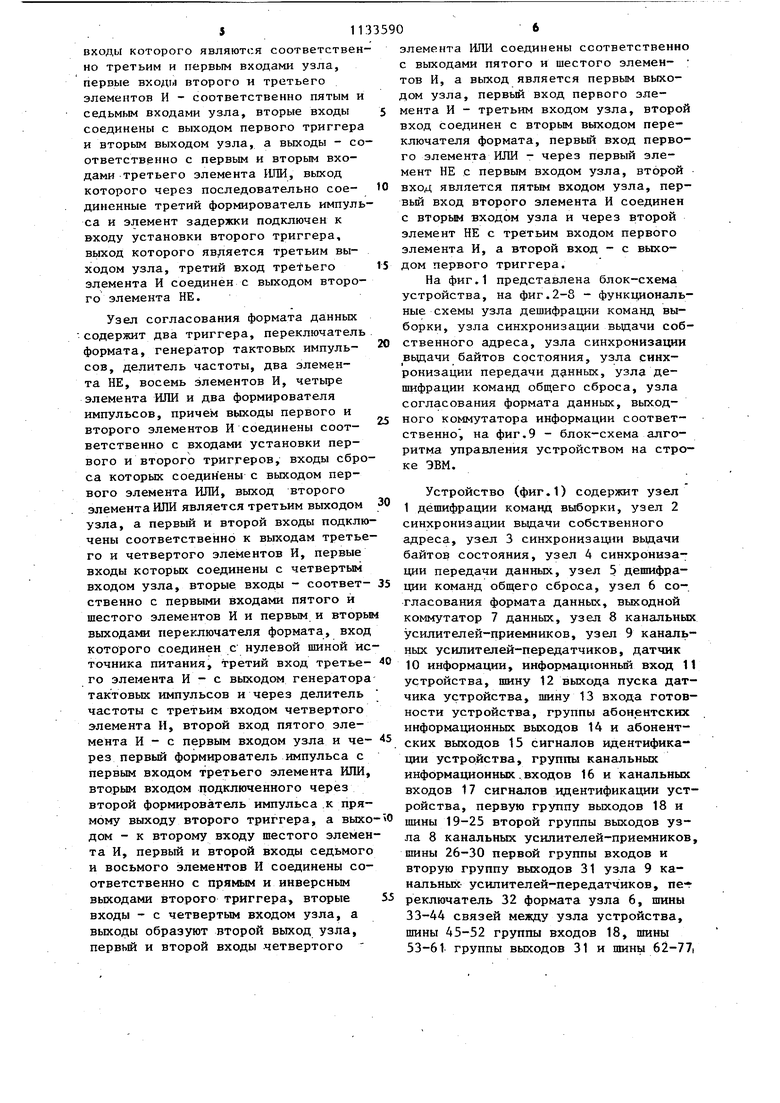

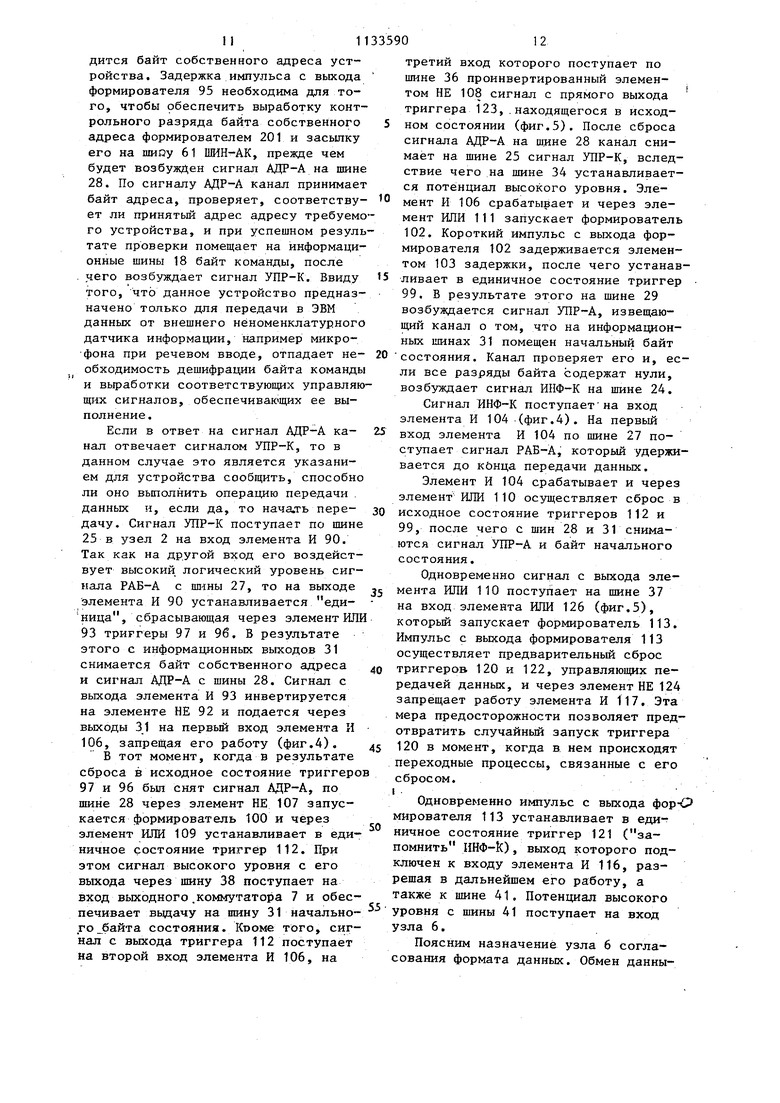

Узел сиахронизации выдачи собственного адреса содержит (фиг.З) элементы И 89 и 90, элементы НЕ 91 и 92, элемент ИЛИ 93, формирователи 94 и 95 импульса, триггеры 96 и 97, элемент 98 задержки.

Узел 3 синхронизации выдачи байтов состояния содержит (фиг.4) второй триггер 99, .формирователи 100102 импульса, элемент 103 задержки,, элементы И 164-106, элементы НЕ 107 и 108, элементы ИЛИ 109-111, первый триггер 112.

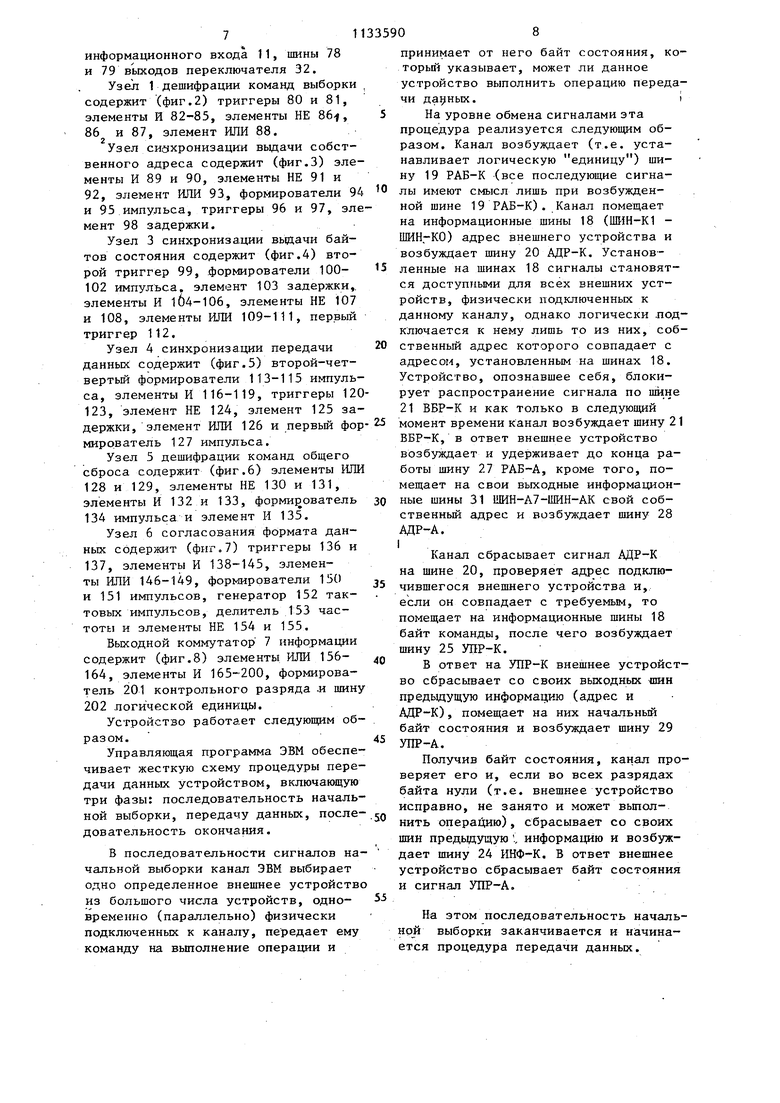

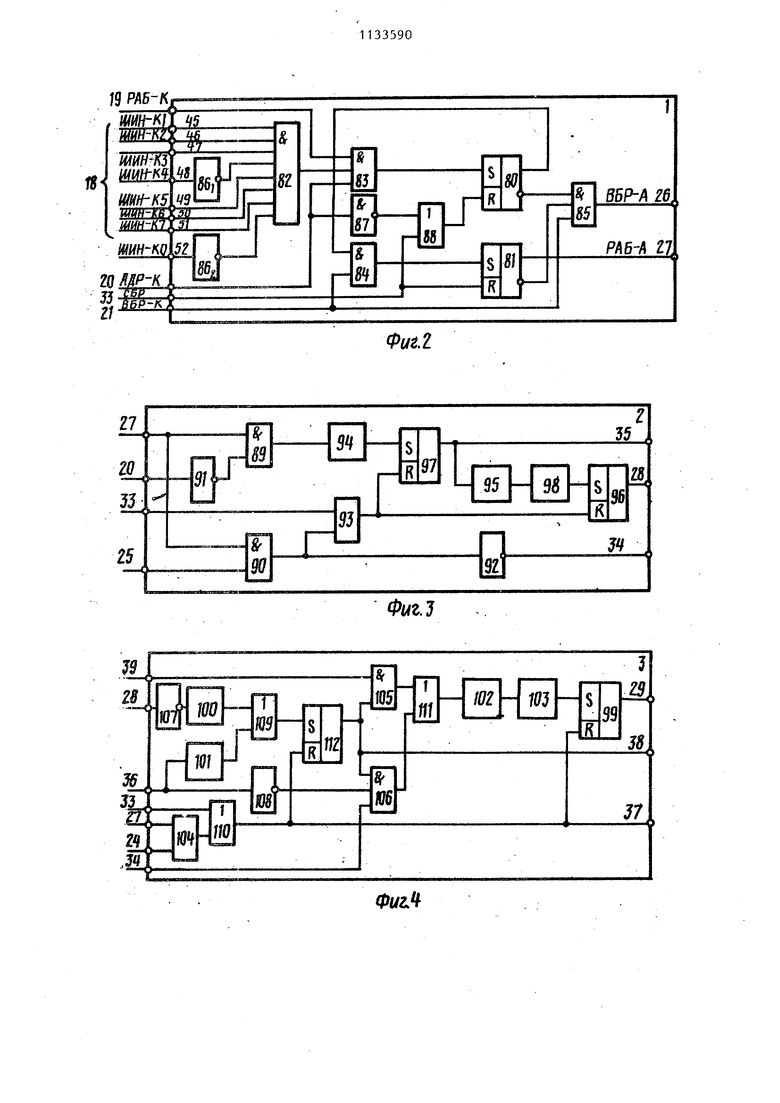

Узел 4 синхронизации передачи данных содержит (фиг.5) второй-четвертый формирователи 113-115 импульса, элементы И 116-119, триггеры 120123, элемент НЕ 124, элемент 125 задержки, элемент ШШ 126 и первьй формиррватель 127 импульса.

Узел 5 дешифрации команд общего сброса содержит (фиг.6) элементы ИЛИ 128 и 129, элементы НЕ 130 и 131, элементы И 132 и 133, формирователь 134 импульса и элемент И 135.

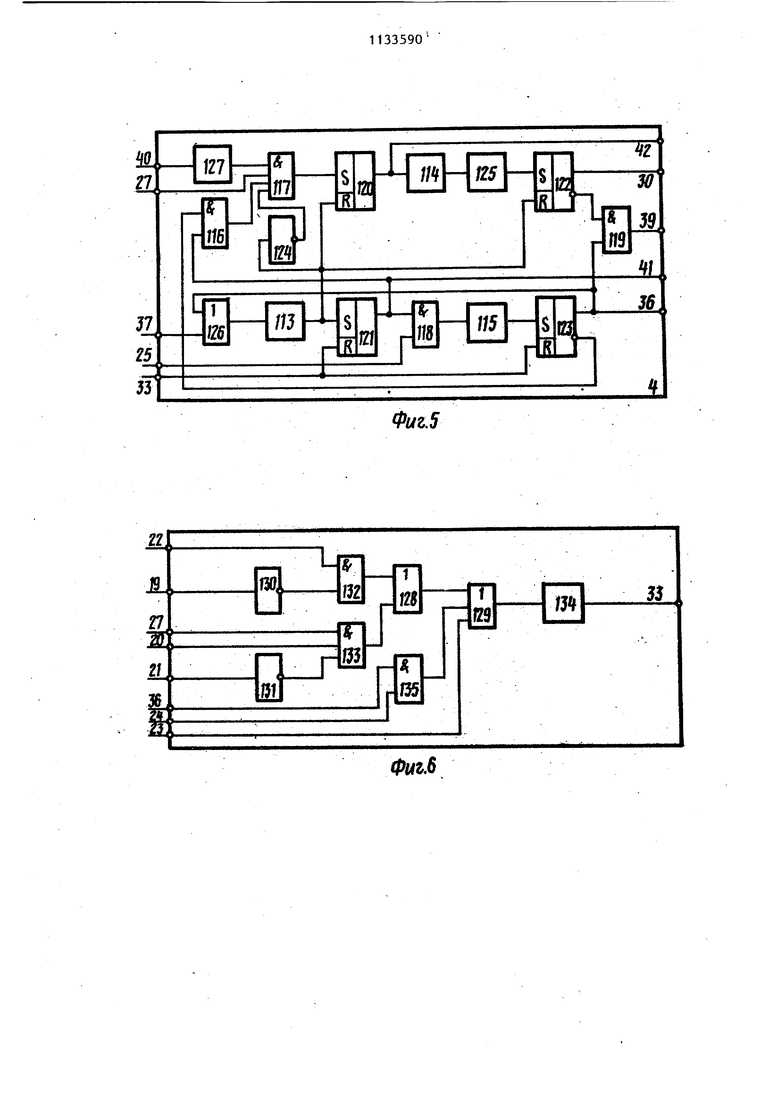

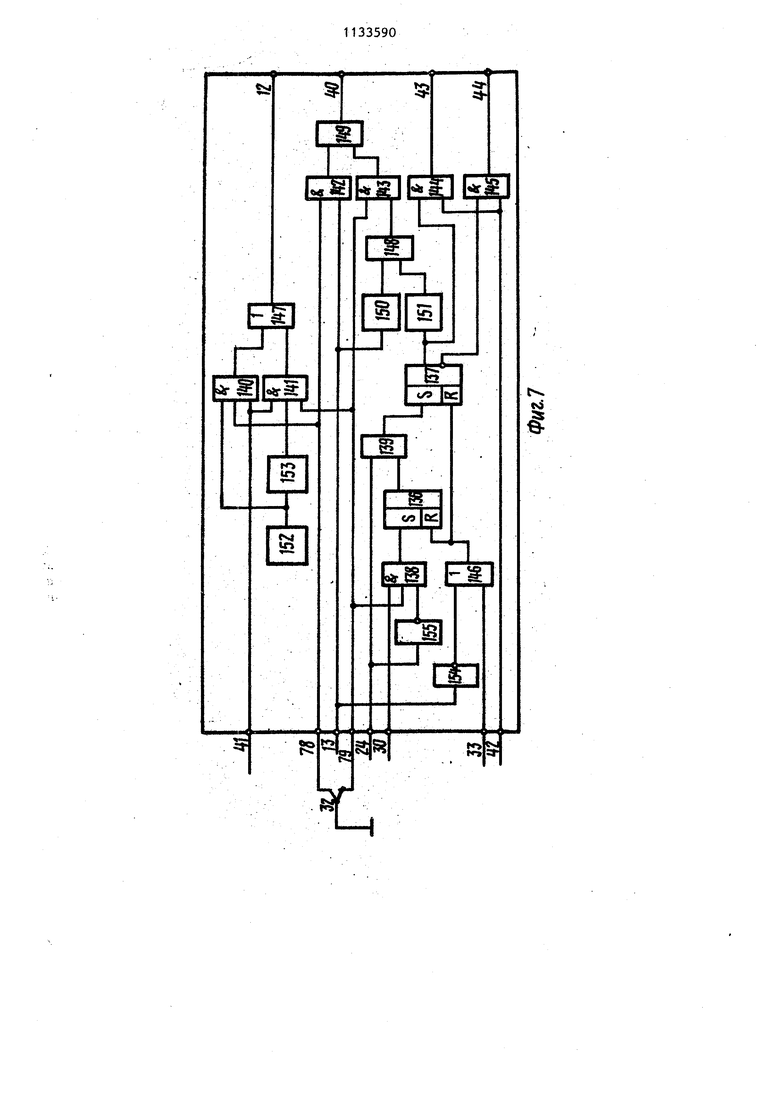

Узел 6 согласования формата данных содержит (фиг.7) триггеры 136 и 137, элементы И 138-145, элементы ИЛИ 146-149, формирователи 150 и 151 импульсов, генератор 152 тактовых импульсов, делитель 153 частоты и элементы НЕ 154 и 155.

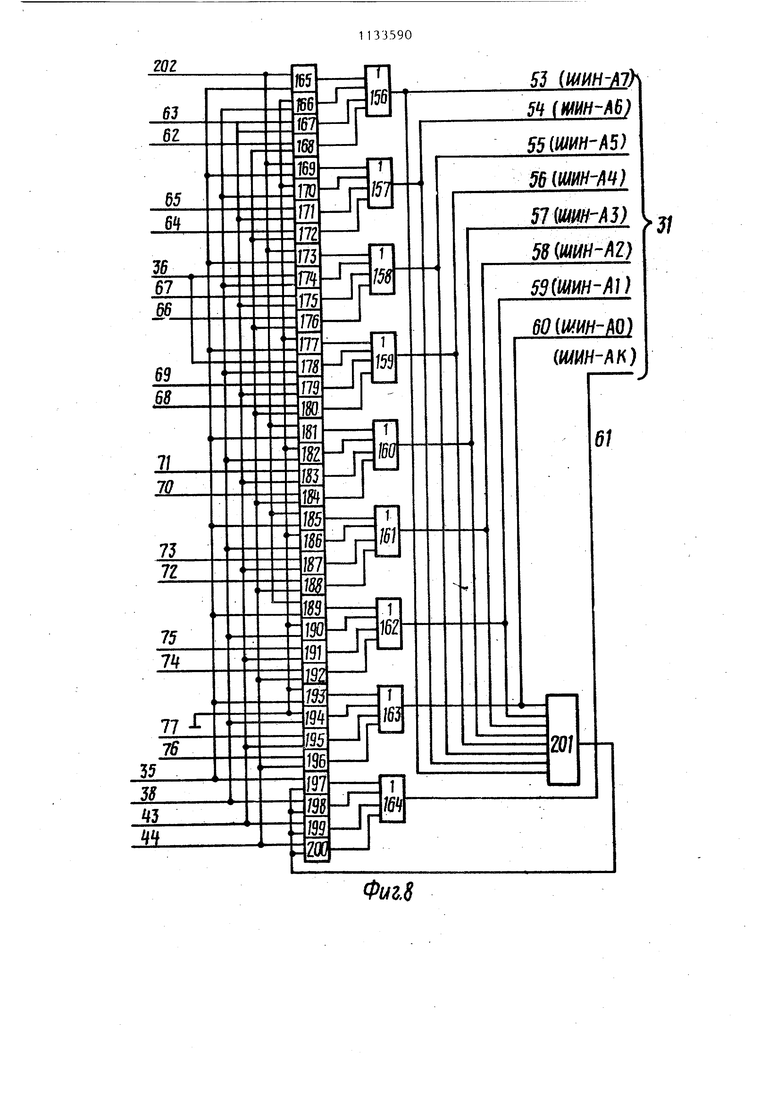

Выходной коммутатор 7 информации содержит (фиг.8) элементы ИЛИ 156164, элементы И 165-200, формирователь 201 контрольного разряда .и шину 202 логической единицы.

Устройство работает следующим образом.

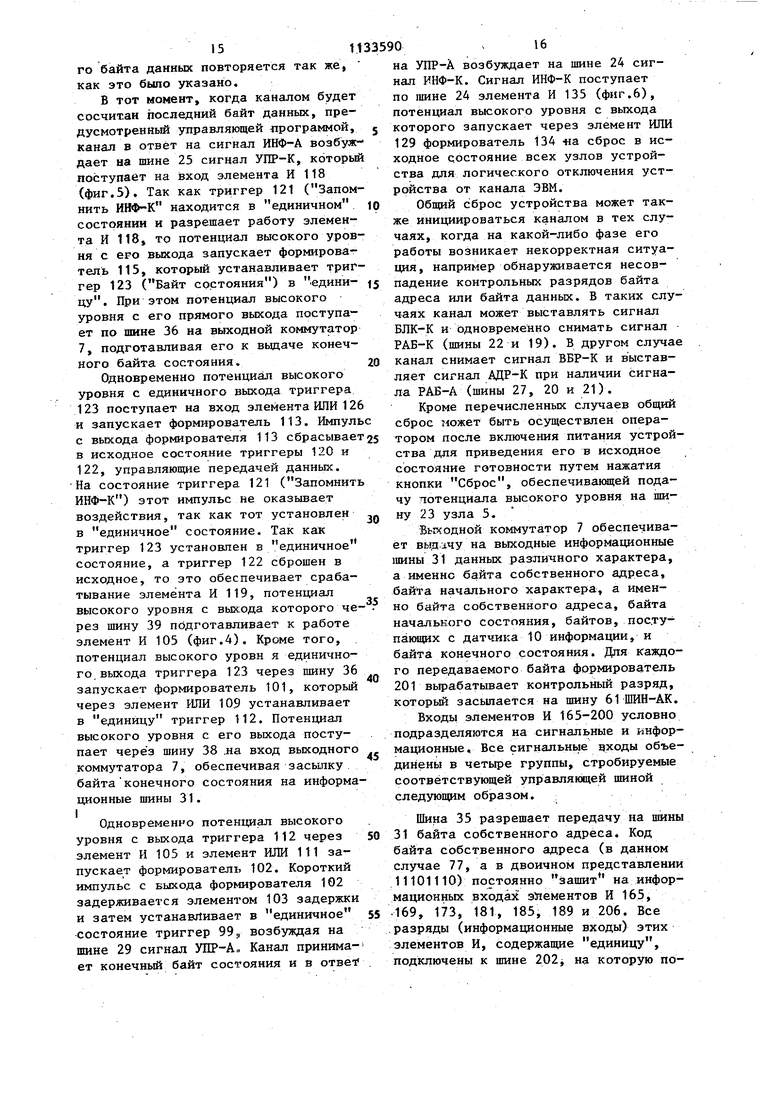

Управляющая программа ЭВМ обеспечивает жесткую схему процедуры передачи данных устройством, включающую три фазы: последовательность начальной выборки, передачу данных, последовательность окончания.

В последовательности сигналов начальной выборки канал ЭВМ выбирает одно определенное внешнее устройство из большого числа устройств, одновременно (параллельно) физически подключенных к каналу, передает ему команду на вьтолнение операции и

принимает от него байт состояния, которьй указывает, может ли данное устройство выполнить операцию передачи данных.

На уровне обмена сигналами эта процедура реализуется следующим образом. Канал возбуждает (т.е. устанавливает логическую единицу) шину 19 РАБ-К (все последующие сигналы имеют смысл лишь при возбужденной шине 19 РАВ-К). Канал помещает на информационные шины 18 (IlttlH-KI ШИН.-КО) адрес внешнего устройства и возбуждает шину 20 АДР-К, Установленные на шинах 18 сигналы становятся доступными для всех внешних устройств, физически подключенных к данному каналу, однако логически .подключается к нему лишь то из них, собственный адрес которого совпадает с адресом, установленным на шинах 18. Устройство, опознавшее себя, блокирует распространение сигнала по шине 21 ВБР-К и как только в следующий момент времени канал возбуждает шину 2 ВБР-К, в ответ внешнее устройство возбуждает и удерживает до конца работы шину 27 РАБ-А, кроме того, помещает на свои выходные информационные шины 31 ШИН-А7-ШИН-АК свой собственный адрес и возбуждает шину 28 АДР-А. I

Канал сбрасывает сигнал АДР-К

на шине 20, проверяет адрес подключившегося внешнего устройства и, если он совпадает с требуемым, то помещает на информационные шины 18 байт команды, после чего возбуждает шину 25 УПР-К.

В ответ на УПР-К внешнее устройство сбрасывает со своих выходных шин предыдущую информацию (адрес и АДР-К), помещает на них начальный байт состояния и возбуждает шину 29 УПР-А.

Получив байт состояния, канал проверяет его и, если во всех разрядах байта нули (т.е. внешнее устройство исправно, не занято и может выполнить операцию), сбрасывает со своих шин предьщущую, информацию и возбуждает шину 24 ИНФ-К. В ответ внешнее устройство сбрасывает байт состояния и сигнал УПР-А.

На этом последовательность начально й выборки заканчивается и начинается процедура передачи данных.

Как только устройство сформировало первый байт данных, поступивший от датчика 1Q, вьфаботав для него контрольный разряд (признак нечетности), оно помещает его на шины 31 (ШИН-А7ШИН-АК) и возбуждает шину 30 ИНФ-А,

Канал снимает сигнал ИНФ-К с шины 24, принимает байт, вьфабатывает контрольный разряд, сравнивает его ;с полученным и при совпадении вновь возбузкдает шину 24 ИНФ-К. В ответ устройство снимает с шины 30 сигнал ИНФ-А, сбрасывйе данные с шин 31 и как только сформируется очередной байт, помещает его на информационные шины 31 и вновь возбуждает шину 30 ИНФ-А. В дальнейшем всякий новьй байт со стороны .устройства сопровождается сигналом ИНФ-А, всякий раз, приняв очередной байт, канал отвечает ИНФ-К.

Программа, управляющая работой устройства, обеспечивает счет переданньк байтов. Сосчитав последний байт,, она извещает об этом канал. Канал, приняв последний байт, возбуждает в ответ на сигнал ИНФ-А шину 25 УПР-К, что означает для устройства в этом случае указание перейти, к процедуре окончания.

В процедуре последовательности окончания устройство сопряжения помещает на выходные информационные шины 31 кбнечньй байт состояния (четвертый и пятьй разряд байта в единице, что означает успешное завершение работы) и возбуждает шину

29 УПР-А.

Канал в ответ на. сигнал УПР-А отвечает сигналом ИНФ-К и снимает сиг- нал ВВР-К. Устройство осуществляет общий сброс и отключается от канала.

Выборка устройства обеспечивается узлом 1. Канал возбуждает сигнал РАБ-К, которьй поступает на шину 19 и подготавливает к работе элемент И 8 (фиг.2).

Вслед за этим канал помещает на информационные шины 18 ШИН-К1 ШИН-КО байт адреса устройства (в нашем случае 77 в двоичном коде 11101110) и .возбуждает шину 20 АДР-К. Код адреса устройства -поступает на шины 18 и далее на вход элемента И 82. При этом разряды кода адреса, содержащие .|нулк, инвертируются элементами НЕ 86 На выходе элемента И 82 устанавливается единица, разрешающая работу

элемента И 83. В тот момент, когда канал возбуждает шину 20, сигнал высокого уровня поступает на вход эле-; мента И 83 и устанавливает в единичное состояние триггер 80. Прямым выходом триггер 80 разрешает работу элемента И 84, а инверсным выходом запрещает работу элемента И 85, блокируя тем самым цепь распространения сигнала ВБР-К к другим внешним устройствам.

В следующий момент времени канал возбуждает сигнал выборки ВБР-К, который поступает на шину 21 и далее на входы элементов И 84 и 85. Так как работа элемента И 85 запрещена инверсным выходом триггера 80, то сигнал ВБР-К дальше не распространяется. Срабатывает лишь элемент И 84 и устанавливает в единичное состояние триггер 81. При этом своим инверсным выходом триггер 81 запрещает работу элемента И 85, а прямым выходом возбуждает шину 27 (сигнал РАБ-А). Сигнал РАБ-А разрешает работу узлов 2-5 устройства и через канальные передатчики узла 9 поступает в канал ЭВМ. В ствет на сигнал РАБ-А канал снимает с шины 20 сигнал АДР-К. При этом логический нуль, установившийся на шине 20, инвертируется элтсементом НЕ 87 и через элемент ИЛИ 88 сбрасывает в исходное состояние триггер 80. При этом триггер 81 остается в едйни 1ном состоянии до окончания процедуры передачи данных. Логический нуль, установившийся после сброса каналом сигнала АДР-К на пине 20, поступает в узел 2 (фиг.З), Проинвертированный на элементе НЕ 91 сигнал АДР-К разрешает работу элемента И 89, к другомувходу которого по шине 27 приложен сигнал высокого уровня РАБ-А. В результате запускается формирователь 94, который устанавливает в единиц-. ное состояние триггер 97. Сигнал высокого уровня с выхода 35 поступает на вход выходного коммутатора 7, обеспечивая помещение на информационные шины 31 байта собственного адреса устройства.

Этот же сигнал запускает формирователь 95. Короткий Ш4пульс, сформированньй им, задерживается элементом 98 задержки, и затем устанавливается в единичное состояние триггер 96, прямой выход которого возбуждает пи НУ 28 АДР-А, извещая канал о том, что на информационных шинах 31 нахо111дится байт собственного адреса устройства. Задержка импульса с выхода формирователя 95 необходима для того, чтобы обеслечкть выработку конт рольного разряда байта собственного адреса формирователем 201 и засылку его на шийу 61 ШИН-АК, прежде чем будет возбужден сигнал АДР-А на шин 28. По сигналу АДР-А канал принимае байт адреса, проверяет, соответству ет ли принятый адрес адресу требуем го устройства, и при успешном резул тате проверки помещает на информационные шины 18 байт команды, после . чего возбуждает сигнал УПР-К. Ввиду того, что данное устройство предназначено только для передачи в ЭВМ данных от внешнего нёноменклатурного датчика информации, например микрофона при речевом вводе, отпадает необходимость дешифрации байта команды и выработки соответствующих управляю щих сигналов, обеспечивающих ее выполнение. Если в ответ на сигнал АДР-А канал отвечает сигналом УПР-К, то в данном случае это является указанием для устройства сообщить, способно ли оно выполнить операцию передачи . данных и, если да, то нача.ть передачу. Сигнал УПР-К поступает по щине 25 в узел 2 на вход элемента И 90. Так как на другой вход его воздействует высокий логический уровень сигнала РАБ-А с шины 27, то на выходе элемента И 90 устанавливается единица, сбрасывающая через элемент ИЛ 93 триггеры 97 и 96. В результате этого с информационных выходов 31 снимается байт собственного адреса и сигнал АДР-А с шины 28. Сигнал с вьгхода элемента И 93 инвертируется на элементе НЕ 92 и подается через выходы 31 на первьй вход элемента И 106, запрещая его работу (фиг.4). В тот момент, когда в результате сброса в исходное состояние триггеро 97 и 96 бьш снят сигнал АДР-А, по шине 28 через элемент НЕ 107 запускается формирователь 100 и через элемент ИЛИ 109 устанавливает в единичное состояние триггер 112. При этом сигнал высокого уровня с его выхода через шину 38 поступает на вход выходного.коммутатора 7 и обеспечивает вьщачу на шину 31 начально го байта состояния. Кооме того, сигнал с выхода триггера 112 поступает на второй вход элемента И 106, на 0 третий вход которого поступает по шине 36 проинвертированный элементом НЕ 108 сигнал с прямого выхода триггера 123,.находящегося в исходном состоянии (фиг.5). После сброса сигнала АДР-А на шине 28 канал снимает на шине 25 сигнал УПР-К, вследствие чего на шине 34 устанавливается потенциал высокого уровня. Элемент И 106 срабатывает и через элемент ИЛИ 111 запускает формирователь 102. Короткий импульс с вьгхода формирователя 102 задерживается элементом 103 задержки, после чего устанавливает в единичное состояние триггер 99. В результате этого на шине 29 возбуждается сигнал УПР-А, извещающий канал о том, что на информационных шинах 31 помещен начальный байт состояния. Канал проверяет его и, если все разряды байта содержат нули, возбуждает сигнал ИНФ-К на шине 24. Сигнал ИНФ-К поступаетна вход элемента И 104 (фиг.4). На первый вход элемента И 104 по шине 27 поступает сигнал РАБ-А, который удерживается до кЬнца передачи данных. Элемент И 104 срабатывает и через элемент ИЛИ 110 осуществляет сброс в исходное состояние триггеров 112 и 99, после чего с шин 28 и 31 снимаются сигнал УПР-А и байт начального состояния. Одновременно сигнал с вьгхода элемента РШИ 110 поступает на шине 37 на вход элемента ИЛИ 126 (фиг.5), который запускает формирователь 113. Импульс с выхода формирователя 113 осуществляет предварительный сброс триггеров 120 и 122, управляющих передачей данных, и через элемент НЕ 124 запрещает работу элемента И 117, Эта мера предосторожности позволяет предотвратить случайный запуск триггера 120 в момент, когда в нем происходят переходные процессы, связанные с его сбросом. Одновременно импульс с выхода фор-О ирователя 113 устанавливает в единичное состояние триггер 121 (заомнить ИНФ-k), выход которого подлючен к входу элемента И 116, разешая в дальнейшем его работу, а акже к шине 41. Потенциал высокого ровня с шины 41 поступает на вход зла 6. Поясним назначение узла 6 соглаования формата данных. Обмен данными между датчиком 10 информации и устройством осуществляется, например, в старт-стопном режиме. Устройство возбуждает сигнал Пуск по шине 12, по которому датчик 10 формирует квант данньк. В течение периода формирования устройство находится в режиме ожидания (стоп-реямм). После того как датчик 10 сформировал квант информации на своем вы- ходнрм регистре (не показан), он возбуждает на шине 13 сигнал Готов который активизирует устройство на считывание запрошенного кванта информации. В следутопщй момент устройство вновь возбуждает сигнал Пуск и т.д. в том случае, если разрядность вы ходного регистра датчика не превышает разрядности канала передачи данных, на каждьш такт запроса со стороны устройства приходится один такт формирования кванта данных. Однако если разрядность выходного регистра датчика вьш1е (например, в 2 раза) разрядности канала передачи, возника ет необходимость организовать на каждьй такт формирования данных дат.чиков 10 два такта.передачи данньк, т.е. согласовать форматы данных. В предлагаемом устройстве предусмотрена возможность работы в однобайтовом и двубайтовом режимах путем установки переключателя 32 (фиг.7). Положение переключателя 32, показанное на фиг.7 соответствует.однобайтовому режиму работы. Итак, потенциал высокого уровня с шины 41 поступает на выходы элементов И 140 и 141, разрешая их работу Однако на второй вход элемента И 14 через шину 77 с переключателя 32 по дан нулевой потенциал, запрещающий его работу, в то время как на второй вход элемента И 140 через шину 76 подан потенциал, эквивалентный высокому уровню. Так как третий вход элемента И 140 подключен к выходу г нератора 152, то импульсы тактовой частоты поступают через элемент ИПИ 147 на шину 12 сигнала Пуск датчи ка 10 информации. Спустя некоторое время после поступления первого импульса Пуск датчик 10 помещает на свой выходной регистр байт информации и возбуждает сигнал Готов, который поступает по шине 13 на вто рой вход схемы И 142. Так как на 113 первый вход элемента И 142 подан через шину 76 потенциал, эквивалентныйвысокому уровню, то элемент И 142 срабатывает, и сигнал с его выхода через элемент ИЛИ 149 и шину 40 запускает формирователь 127 (фиг.5). Короткий импульс с выхода формирователя 127 поступает на вход элемента И 117, на других входах которого приложены потенциалы высокого уровня, (сигнал РАБ-А на шине 27 удерживается до конца передачи данных, триггер 121 установлен в единичное состояние, разрешает работу элемента И 116 по одному входу, тригнаходится в нулевом состоя единица на его инверсном выходе разрешает работу элемента И 116 по другому входу, на выходе формирователя 113 удерживается потенциал . . низкого уровня, который через элемент НЕ 124 также разрешает работу элемента И 117). Импульс с выхода элемента И 117 устанавливает в единичное состояние триггер 120. В результате этого потенциал высокого уровня поступает на ину 42 и дапее на вторые входы элементов И 145 и 144 (фиг.7). Так как при работе в од- нобайтовом режиме передачи триггер 137 находится в исходном, сброшенном состоянии, то потенциал высокого уровня на его инверсном выходе разрешает работу элемента И 145. Единичный сигнал с выхода последнего поступает по шине 44 на адресный вход вы-; ходного коммутатора 7, который обеспечивает передачу данных с выходного регистра датчика 10 на шины 31. Одновременно потенциал высокого уровня на выходе триггера 120 запускает формирователь 114. Короткий импульс с выхода формирователя 1J14 задерживается элементом 125/задеряски, и затем устанавливает в единичное состояние триггер 122. Потенциал вьосокого уровня на его прямом выходе возбуждает в шине 30 сигнал ИНФ-А, который извещает канал о том, что байт данных готов и находится на шинах 31. Канал снимает с шины 24 сигнал ИНФ-К, считывает байт данных, провершяет контрольный разряд и, если он совпадает с контрольным разрядом, вьфаботанным каналом, вновь возбуждает на шине 24 сигнал ИНФ-К, требуя передачи очередного байта. В дальнейшем процедура передачи каждого байта данных повторяется так же, как это было указано. В тот момент, когда каналом будет сосчитан последний байт данных, предусмотренный управляющей программой, канал в ответ на сигнал ИНФ-А возбуж дает на шине 25 сигнал УПР-К, которы поступает на вход элемента И 118 (фиг.5). Так как триггер 121 (Залом нить ИНФ-К находится в единичном состоянии и разрешает работу элемента И 118, то потенциал высокого уров ня с его выхода запускает формирователь 115, который устанавливает триг гер 123 (Байт состояния) в вдиницу. При этом потенциал высокого уровня с его прямого выхода поступает по шине 36 на выходной коммута.тор 7, подготавливая его к вьщаче конечного байта состояния. Одновременно потенциал высокого уровня с единичного выхода триггера 123 поступает на вход элемента ИЛИ 12 и запускает формирователь 113. Импул с выхода формирователя 113 сбрасывает в исходное состояние триггеры 120 и 122, управляющие передачей данных. На состояние триггера 121 (Запомнить ИНФ-К) этот импульс не оказывает воздействия, так как тот установлен в единичное состояние. Так как триггер 123 установлен в единичное состояние, а триггер 122 сброшен в исходное, то это обеспечивает срабатывание элемента И 119, потенциал высокого уровня с выхода которого через шину 39 подготавливает к работе элемент И 105 (фиг.4). Кроме того, потенциал высокого уровн я единичного, выхода триггера 123 через шину 36 запускает формирователь 101, который через элемент ИЛИ 105 устанавливает в единицу триггер 112. Потенциал высокого уровня с его выхода поступает через шину 38 .на вход выходного коммутатора 7, обеспечивая засьшку байтаконечного состояния на информационные шины 31. Одновременно потенциал высокого уровня с выхода триггера 112 через элемент И 105 и элемент ИЛИ 111 запускает формирователь 102. Короткий импульс с выхода формирователя 102 задерживается элементом 103 задержки и затем устанавливает в единичное состояние триггер 99., возбуждая на шине 29 сигнал УПР-А,, Канал принимает коиечньй байт состояния и в ответ на УПР-А возбуждает на шине 24 сигнал ИНФ-К. Сигнал ИНФ-К поступает по шине 24 элемента И 135 (фиг.6), потенциал вьюокого уровня с выхода которого запускает через элемент ИЛИ 129 формирователь 134 -на сброс в исходное состояние всех узлов устройства для логического отключения устройства от канала ЭВМ. Общий сброс устройства может также инициироваться каналом в тех случаях, когда на какой-либо фазе его работы возникает некорректная ситуация, например обнаруживается несовпадение контрольных разрядов байта адреса или байта данных. В таких случаях канал может выставлять сигнал БЛК-К и Одновременно снимать сигнал РАБ-К (шины 22 и 19). В другом случае канал снимает сигнал ВБР-К и выставляет сигнал АДР-К при наличии сигнала РАБ-А (шины 27, 20 и 21). Кроме перечисленных случаев общий сброс может быть осуществлен оператором после включения питания устройства для приведения его в исходное состояние готовности путем нажатия кнопки Сброс, обеспечивакндей подачу потенциала высокого уровня на шину 23 узла 5. Вьгходной коммутатор 7 обеспечивает вьщачу на выходные информационные тины 31 данных различного характера, а именно байта собственного адреса, байта начального характера, а именно байта собственного адреса, байта начального состояния, байтов, поступающих с датчика 10 информации, и байта конечного состояния. Для каждого передаваемого байта формирователь 201 вырабатывает контрольный разряд, который засьшается на шину 61 ШИН-АК. Входы элементов И 165-200 условно подразделяются на сигнальные и информационные. Все сигнгшьные дходы объединены в четыре группы, стробируемые соответствующей управляющей шиной следуюпщм образом. Шина 35 разрешает передачу на шины 31 байта собственного адреса. Код байта собственного адреса (в данном случае 77, а в двоичном представлении 11101110) постоянно зашит на инфорационных входах элементов И 165, 169, 173, 181, 185, 189 и 206. Все азряды (информационные входы) этих лементов И, содержащие единицу, одключены к шине 202 на которую постоянно подается потенциал, эквивалентньй логической единице. Входы i двух разрядов, содержащих нуль, соединены с землей (элементы И 177 и 206).

Шина 38 разрешает, передачу на шины 31 байта начального состояния. Код байта, кроме двух разрядов - четвер-. того и пятого (элементы И 178 и 174), подключенных к шине 36, также постоянно зашит на информационных входах элементов И 166,. 170, 182, 186, 190 и 194, на которые подан потенциал земли. Два разряда, объединенные шиной 36, подключены к единичному выходу триггера 123. (Байт состояния) узла 4 (фиг.5). На фазе вьщачи начального байта состояния триггер 123 сброшен, чем обеспечивается засьтка в 4-й и 5-й разряды байта логическо.го нуля. На фазе вьвдачи конечного байта состояния триггер 123 вводится чем обеспечивается засылка- елиницы в четвертьм и пятый разряды байта, на что указывает сигнал Канал кончил, ВУ кончило. Шины 43 и 44 разрешают передачу данных на шины 31. При .работе в однобайтном режиме передачи активизируется лишь шина 44, подключенная к выходу узла 6 согласования формата данных (фиг.7), разрешая тем самым передачу данных, поступающих с выход ного (однобайтного) регистра датчика 10 (фиг.6) на входы 62, 64, 66, 68, 70, 72, 74 и 76. При работе в двухбайтном режиме в процедуре непосредственной передачи данных узел попеременно активизирует шины 43 и 44, обеспечивая передачу на шины 31 вначале старшего байта данных, находящегося на четных входных шинах 62-76, а затем младшего байта, поступающего с соответствующей части выходного регистра датчика 10 на шины 63, 65, 67, 69, 71, 73, 75 и 77. Установкой переключателя 32 в вер хнее по схеме положение осуществляется перевод устройства в двухбайтный. режим передачи данных. При этом на шину 76 узла подается потенциал зем ли, которьй запрещает работу элемен та И 140. Поэтому сигнал разрешения передачи данных, поступающий на шину 55 41, .активизирует лишь элемент И 141. На второй вход элемента И 1.41 поступают импульсы генератора 152, частота следования которых уменьшена в два раза делителем 153.

Уменьшение в два раза тактовой частоты в двухбайтном режиме передачи данных обусловлено следующими обстоятельствами. В тех случаях, когда длительность процедуры одного такта формирования данных датчиком 10 меньше 2Т, где Т - время одного такта передачи данных от устройства в накал ЭВМ, при двухбайтном режиме передачи возникает ситуация переполнения выходного регистра датчика 10, так как за один такт формирования данных устройство должно осуществить два такта пересылки данных, как указывалось .ранее. Таким образом, с выхода элемента И 141 импульсы тактовой частоты поступают на элемент ИЛИ 147 и далее на выходную шину 12, осуществляя пуск датчика 10 информации. После того, как датчик 10 сформирует квант данных, он возбуждает в шине 13 сигнал Готов, поступающий на вход формирователя 130. Одновременно этот сигнал поступает и на вход элемента И 142 блокированного при помощи переключателя 32.. Кор.откий импульс с выхода формирователя 150 поступает через элемент ИЛИ 148 на вход элемента И 143, открытого потенциалом с переключателя 32. В результате на выхрде элемента И 143 устанавливается единица, которая через элемент ИЛИ 149 и шину 40 обеспечивает выработку сигнала Поместить данные на выходнь е шины, поступакицего через узел 4 на шину 66 и далее на вторые входы элементов И 144 и 145J Но таккак к этому моменту триггер 137 находится в исходном состоянии и на его инверсном выходе удерживается единица, то разрешается работа лишь элемента И 145. В результате потенциал высоко-. го уровня поступает на шину 44 4j да-. лее на вход выходного коммутатора обеспечивая тем самым передачу старшего байта в канал ЭВМ, который сопровождается сигналом ИНФ-А на шине 30. В ответ на сигнал ИНФ-А канал снимает с шины 24 сигнал ИНФ-К, принимает байт и проверяет его контрольный разряд. Сигнал с шины 30 ИНФ-А-поступает на первый вход элемента И 138. На второй вход последнего подается потенциал логической

единицы с переключателя 32, а на третий вход - проинвертнрованный на элементе НЕ 155 шины 24 сигнал ИНФ-К. Так как в данный момент канал снял ИНФ-К, то на выходе элемента НЕ 155 установлена единица В результате устанавливается в единичное состояние триггер 136, подготавливая к работе элемент И 139.

После того, как канал проверит контрольный разряд и результат проверки окажется успешным, он вновь возбуждает в шине 24 сигнал ИНФ-К, указывающий на необходимость передачи очередного байта данных.

Теперь потенциал высокого уровня ИНФ-К с шины 24 поступает на первый вход схемы И 139, и, так как она по второму входу уже подготовлена к работе триггером 136, единица, устанавливающаяся на выходе схемы, вводит в единичное состояние триггер 137.

При этом обеспечивается перекомму тация элементов И 145 и 144, тем соз даются условия для передачи младшего байта, и запускается формирователь 151. Короткий импульс с его выхода поступает через элементы ЮТИ 148, И 143 .и ИЛИ 149 на шину 40, инициируя очередной такт передачи данных, на этот раз - младшего байта. После проверки контрольного разряда байта

канал вновь возбудит сигнал ИНФ-К, но он не сможет инициировать в устройстве очередной такт передачи данных, триггер 137 удерживается в единичном состоянии, а запуск формирователя 151 осуществляется переходом потенциала от низкого уровня к высокому. Поэтому устройство остается в режиме ожидания до тех пор, пока на шину 12 не поступит очередной импульс с генератора 152. Этот импульс осуществляет пуск датчика, который на время, необходимое ему для формирования кванта данных, снимет с шины 13 сигнал Готов. В результате этого потенциал низкого уровня, инвертированный на элементе НЕ 154, осуществляет через элемент ИЛИ 146 сброс в исходное состояние триггеров 136 и 137. Тем самым узел 6 согласования формата данных оказывается приведенным в исходное состояние готовности, и дальнейшая процедура передачи данных повторяется.

Таким образом, предлагаемое устройство при. меньших по сравнению с известным аппаратурных затратах обеспечивает сопряжение ЭВМ с различными датчиками информации, такими как аналого-цифровые преобразователи, измерительные приборы, регистраторы процессов и т.п.

/9 РЛБ-Л

27

5

IL 55

25

Фи,г

35

Z8.

к

J

Фмг.5

Фиг.

Фиг.5

Фиг,6

55 (МИН-А7)

54 ()

55(ШИ//-А5)

5бтН-АЦ)

§7{ит-А5)

58 ШНА2)

53(шт-М} бО(тн-м}

(ШИЯ-ЛК)

Фиг.8

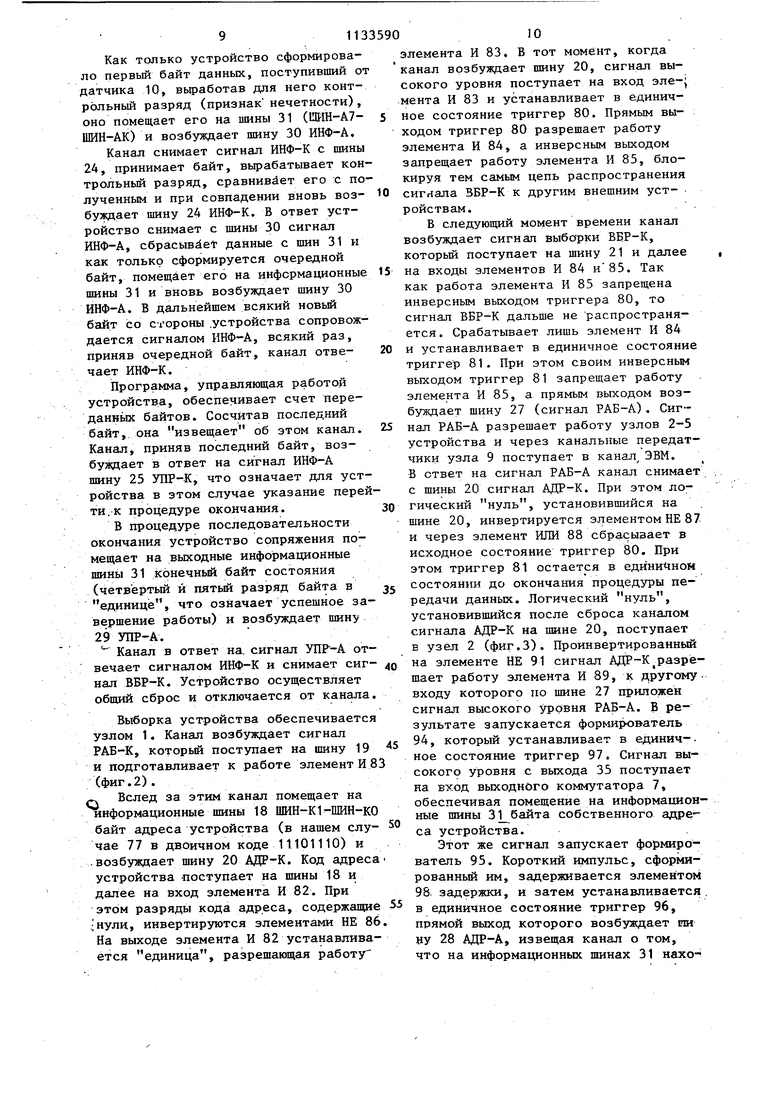

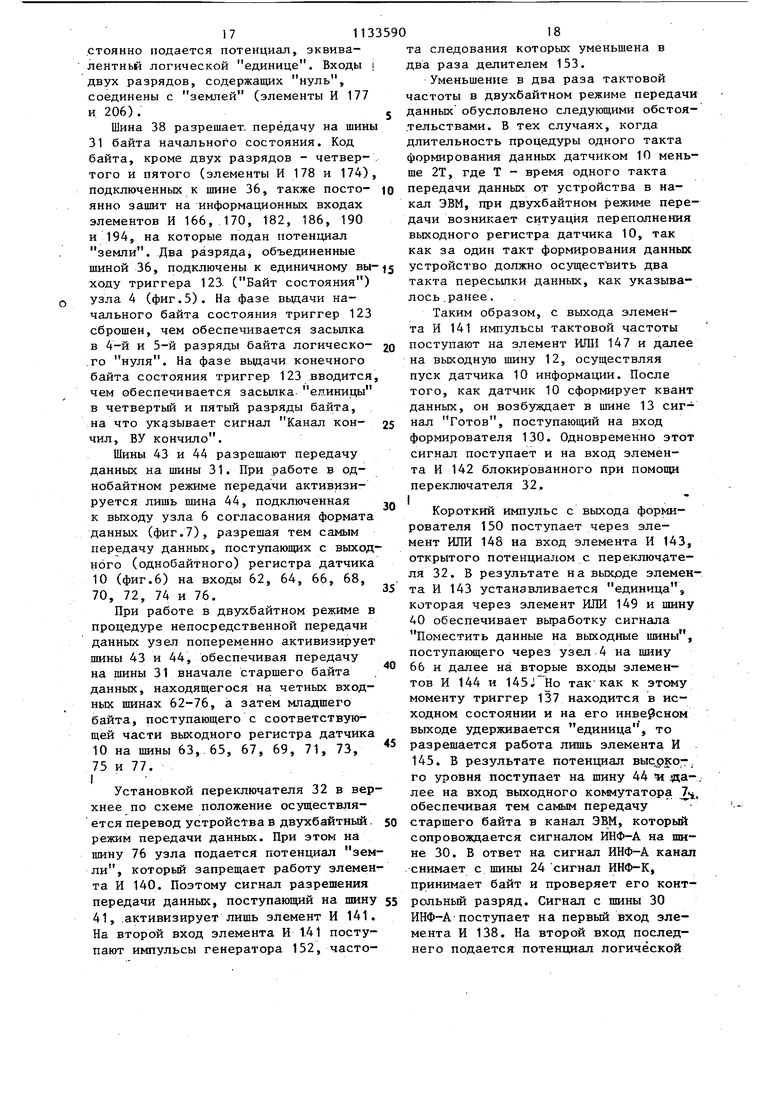

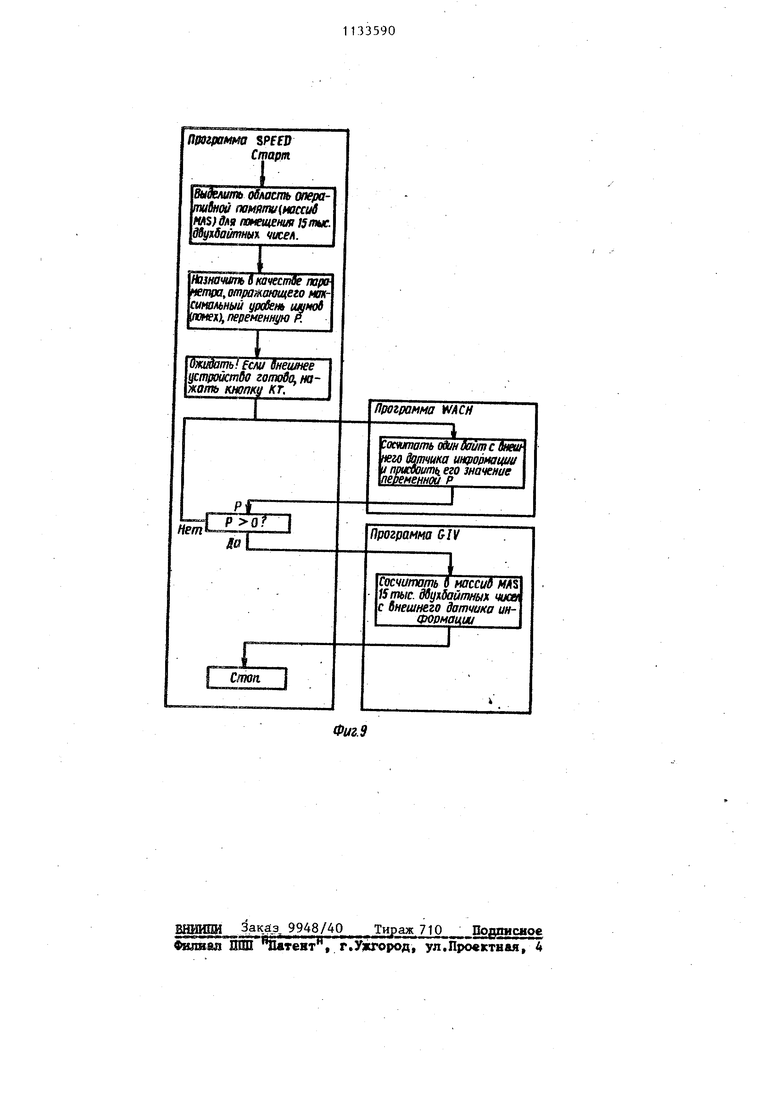

nooifaMMQ 3PffD Старт

Выдешть oSAOcm onepaтбнаа помятциассм MAS) для fmeuwHM 15 тыс. двухбайтные чисел.

Назтшпь В кочестОе пари Петра, мтси юлбный дроВень имнод /юмек), переменн1ро Р.

Ожидать; few внешнее { тройстбУ гоаюво, иажать кнопка кг.

w

ZL

-Ч

/nLc.J.-

Нет

XaL

Программа WACH

i

tacwmamit один байт с Оюш

нею Зйщчика UHqtopwtmu и npuaoumk его значение лекменнои Р

Программа &IV

I

шчитать б иассиб AMS

15 тыс. доулдаитных чисел

с Внешнего датчика ииФормацш

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 477409, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство сопряжения датчика информации с каналом вычислительной машины | 1972 |

|

SU525940A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-07—Публикация

1983-02-18—Подача