(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1981 |

|

SU1002977A2 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1999 |

|

RU2190874C2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

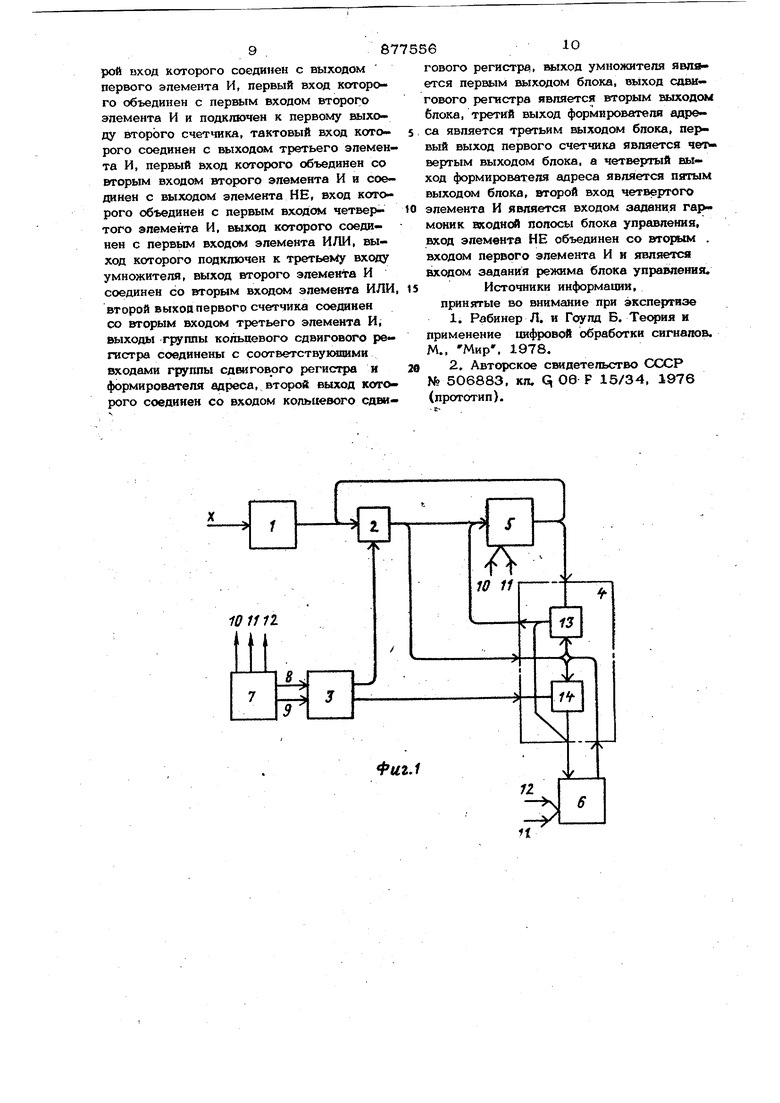

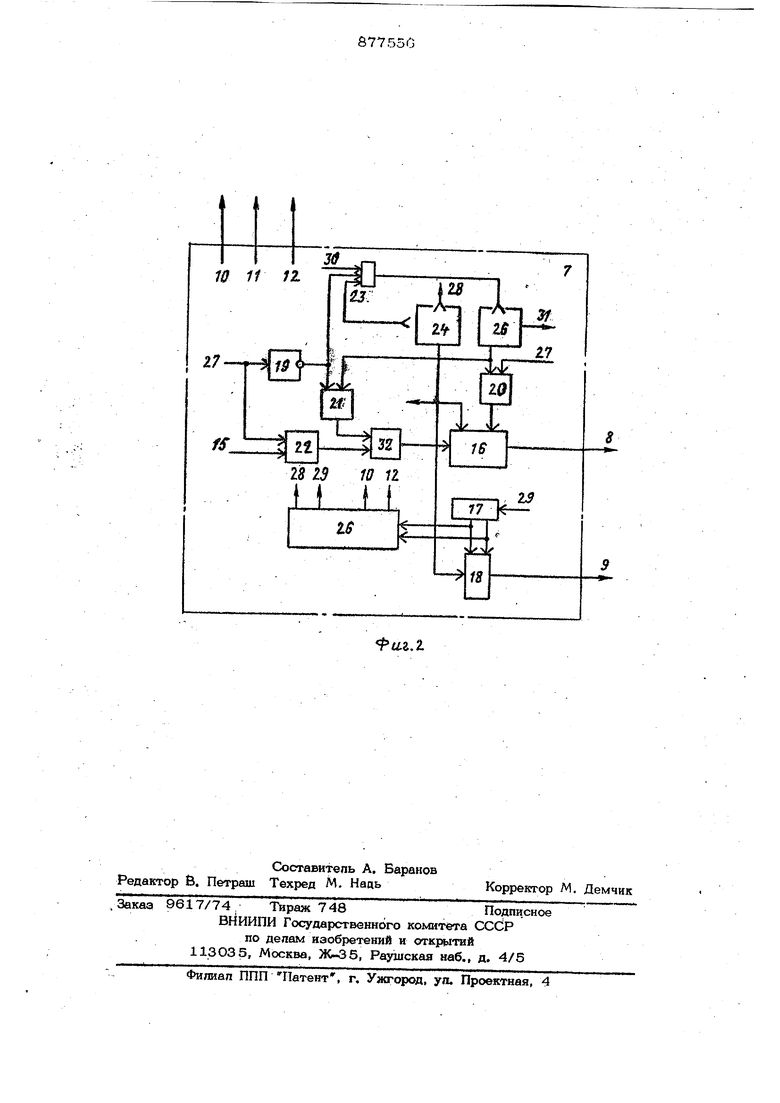

Изобретение относится к вычислительной технике и может быть применено дяя вычисления дискретного преобразования Фурье (ДПФ) в заданной полосе частот спектрй высокого разрешения при решении задач виброакустического контроля технического состояния машин и механизмов. Осуществление вибрационного контро ля связано с измерением в реальном масштабе времени спектров комплексных сигналов 20-50 кГц. Известны цифровые устройства, вычисляющие полные спектры входных сигналов и спектры в заданных полосах частот с использованием методов быстрых преобразований и цифровой фильтрации р-З. Метод цифровой фильтрации позволяет вычислять полные и полосовые спектры, но, во-первых, требует при этом программной перестройки по каждой спектральной дискрете, что приводит к необходимости использования сложного блока прогр 1ммно- го управления. Во-вторых, метод не обладает эффектом быстрого преобразования; вычисление дискрет спектра связано с последовательной N -кратной обработкой входного числового массива. В- ретьих, цифровые фильтры измеряют преимущественно спектры, для вычисления других функций нужно вводить в прибор дополнительные узпы, что нарушает структурную депост- ность прибора. Еичетвертых, цифровой фильтр - одноканальное устройство, и организация обработки составных (кс лппеко« ных) сигналов здесь существенно затруднена. Указанные недостатки устрсЛства Ш1ФРОВОЙ фильтрации являются важными, прежде всего для вибрационного контроля. Методы быстрых преобразований, например, быстрое преобразование Фурье (БПФ), на ипучшим образом удовлетворяют требованиям вибрационного контроля и диагностики. Анализатор, ы топняющий БПФ, обрабатывает информацию по двум каналам в реальном времени до нескольких десятков килогерц частоты входного сигнала с измерением спектральных, корреляционных функций, а также функций распределения вероятностей и т.п. Однако функционадьная жесткость алгоритма БПФ приводит, в свою очередь, к весьма существенному недостатку устройства, который закгаоча ется в том, что алгоритм позволяет вычислять только полные спектры сигналов, т.е. спектры во всем диапазоне частот от О до частоты среза. Это определяет разрешающую способность анализа. Однако часто возникает, необходимость просмот ра спектра с шагом до единиц и долей рерц в некоторой полосе частот, которая тем уже, чем выше разрешение. В таких случаях возможно переходить от вычисления полного спектра к полосовому авали зу. Но в случае БПФ такой переход не может быть выполнен эффективно. Это связано с резким увеличением об.ъема опе ративной памяти до соответствующих разрешению размеров. Наиболее близким по технической сущности к предлагаемому .является устройство для вычисления коэффициентов Фурье, содержащее входной блок памяти, блок умножения, блок памяти тригонометрических . функций, блок инверсной перестановки,блок памяти, арифметический блок и сумматор 2J. Устройство позволяет вычислять неболыиое количество коэффициентов из числа реализуемых методом БПФ. Достигается это ограничением числа выполняемых итераций алгоритма и дополнительным усложнением устройства, которое содержит многоканальный сумматор. Но, как указано выше, такое решение не приводит к ,. технике-экономическому эффекту, поскогйь- ку и в этом случае аппаратур1 ые средства должны быть расчитаны на полное испо1шение алгоритма БПФ. В этом устройстве объем памяти необходимо уве;шчивать пропорционально задаваемому разрешению анализа. Цепь изобретения упрощение устрой- ства. Указанная цель достигается тем, что устройство для вычисления коэффициентов дискретного преобразования Фурье,содержащее входной блок памяти, два умножителя, сумматор, блок памяти подмассива и блок памяти коэффициентов, первый и второй выходы которого подключены к пе ным входам соответственно первого и вт рого умножителей, вход входного бпдка памяти явл.яется входом устройства, а вы ход входного блока памяти соединен со вторым входом второго умножите.ля, выхо которого подключен ко входу блока памяти подмассива, выход которого соединен с первым входом сумматора, выход котоого подключен ко входу блока памяти подмассива, содержит блок управления и блок памяти суммы, выход которого объединен с выходом первого умножителя и подключен ко вторым входам сумматора и второго умножителя, выход которого обтуединен с выходом сумматора и подключен ко входу блока памяти суммы, выход блока памяти подмассива соединен с первым входом первого умножителя, первый и второй выходы блока управления подключены соответственно к первому и второму управляющим входам блока памяти коэффициентов, третий ичетвертый выходь блока управления соединены соответственно i с первым и вторым управляющими входа- ми блока памяти подмассива, а четвертый и пятый выходы блока управления подключены соответственно к первому и второму управлжонщм входам бгрока памяти суммы, вход задания гармоник входной полосы и вход задания режима блока управления являются первым и вторым управляющими входами устройства. Блок управления содержит два счетчика, четыре элемента И, элемент НЕ, элемент ИЛИ, умножитель, кольцевой сдвиговый peniCTp сдвиговый регистр и формирователь адреса, первый выход которогосоединен с тайтовЫм входом первого счет шка, первый выход которого соединен со входом сдвигового регистра и первым входом умножителя, второй вход которого соединен с выходом первого элемента И, первый вход которого объединен с первым входом второго элемента И и подключен к первому выходу второго счетчика, тактовый вход которого соединен с выходом третьего элемента И, первый вход которой го объединен со вторым входом второго элемента И и соединен с выходом элемента НЕ, вход которого объединен с первым входом четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к третьему .входу умножителя, выход второго элемента И соединен со вторым входом элемента ИЛИ, второй выход первого счетчика соединен со вторым входом третьего элемента И, выходы группы кольцевого сдвигового регистра соединены с соответствующими входами группы сдвигового регистра и формирователя адреса, второй выход которого .соединен со.входом кольцевого сдвигового регистра, выход умножителя является первым выходом . блока, выход сдвигового регистра является вторым выходом блока, третий выход формироватепя ацреса является третьим выходом блока, первый выход первого счетчика является четвертым выходом блока, а четвертый выход формирователя адреса является пятым выходом блока, второй вход четвертого элемента И является входом задания гармоник входной полосы блока управления, вход элемента НЕ объединен со вторым входом первого элемента И и является входом задания режима блока управления. На фиг. 1 приведена схема устройства; на фиг. 2 - функциональная схема блока управления. Устройство содержит входной блок 1 памяти, первый умножитель 2, блОк 3 памяти коэффи.циентов, арифметический блок 4, блок 5 памяти суммы, блок 6 памяти подмассива, блок 7 управления, выходы 8-12 блока управления соответственно первый - пятый, сумматор 13 арифметического блока 4, второй умнохдатель 14 арифметического блока 4. Блок 7 управления включает вход 15 задания началь- ной гармоники полосы, умножитель 16, кольцевой сдвиговый регистр 17, сдвиговый регистр 18, элемент НЕ 19, элементы И 20-23 (или несколькоэлементов ИЛИ в соответствии с разрядностью пропускаемых чисел), счетчики 24 и 25, формирователь 26 адреса, вход 27 режима, счетный вход 28 счетчика 24, управляющий вход 29 сдвигового регистра 17, второй счетный вхоц 30 счетчика 24, выхоа 31 переполнения счетчика26, элемент ИЛИ 32. Алгоритм работы предлагаемого устройства следующий: для вычисления спект ра в полосе с частот сигнал предвари-, тельно умножается на начальную гармонику заданной полосы (по теореме переноса спектра), после чего разделяется на подмассивов, для каждого из которых шолняется частичное дискретное преобр зование Фурье (ДПФУ в полных фазах, ре зультаты циклов ДПФ (частичные результаты) умножаются на поворачивающие, векторы ( с фазами, пропорционал ными щирине С}, полосы, номеру i подмассива и порядку г гармоники в полосе относительно начальной, принимаемой условно за нулевую, причем((-13Ij(N)) конечным результатом являются суммы о дельных произведений,соответствующих о ной и той же гармонике по всем циклам Устройство работает следующим образом. В исходном состоят1и все счетчики устройства установлены в нопь, в том числе и счетчик 25 номера подмассива. Входной блок 1 памяти накапливает отсчеты первого подмассива, которые затем переписываются в блока 6-памяти. При этом числа подмассива пропускаются через ум ножитель 2, где умножаются на начальную гармонику полосы с учетом номера подмассива, что соответствует пребраэованию сигнала y(tj в сигнал x(ft -т--}Начальная гармоника полосы вырабатывается блоком 3 в соответствии с текущим значением фазы, подаваемым в блок 3 из блока 7 управления по выходу 8. Режим перезаписи из блока 1 в блок 6 соответствует единичному режиму работы блока 7 управления, определяемому наличием единичного потенциала на шине 27 режима. Фаза начальной гармоники (ее менная часть) Pt получается путем поре- в умножителе 16 номера Р этой гармоники, задаваемого оператором по входу 15 и временного аргумента t, которому соответствует совместный код с выходов счетчиков 24 и 25, причем счетчик 24 объемом дает .младшую часть разрядов коца, сч гчик 25 объёмом ti - старшую часть. В том, что это так, легко убедиться: кЪд счетчика 24 ecnb &i: ; / , а код счет чика 25 равен {f-i), Ц , что дает f lbfflL., значение объединенного кода совпадающее с вьплепринятой подстановкой. Величина Р подается в умножитель 16 через открытый элемент И 21 и элемент ИЛИ 32, а величина t подается непосредственно с выходов счетчика 24 и с выходов счетчика 25 через открытый элемент И 22, этом элемент И 2О зо- перт и не пропускает код с выхода счетчика 25. Счетчик 24 накапливает импульсы, по которым происходит указанная перезапись шсеп, поэтому его состояние, а , и величина фазы, меняется с каж .дым тактом вызова. Счетчик 25 фиксирует, количество обработанных подмассивов (количество 1шклов перезаписи), поэтому его состояние меняется только при смене подмассива, оставаясь неизменным для всех чисел текущего цикла перезаписи. Умноженные на начальную гармонику числа подаются в арифметический блок 4 по четвертому входу одновременно на сумматор 13 и умножитель 14. Сумматор 13 в режиме перезаписи работает на блок 5 памяти, вычисляя общую сумму поступлений. Происходит это следующим образом. Каждому такту вызова из блока 1 соот- Йетствуют два подтакта работы блока G. В первом подтакте из. блока 5 вызывается операнд и суммируется с вновь поступившим числом подмассива. В течение вто рого подтакта полученная сумма заносится Обратно в блок 5. Вызов и запись в блоке 5 осуществляется неизменно по одному и тому же, нулевому, адресу, задаваемсыу по входу 10. Таким образом, в нулевой ячейке блока 5 рециркулярно накапливается сумма отсчетов, соответствующая коэффициенту Фурье начальной гармо ники. Нулевой адрес задается в формирователь 26 адреса. Умножитель 14 работает на блок 6 памяти, умножая поступающие отсчеты (предварительно умноженные на начальную гармоьшку) на кбэффиш1енты - среднюю гармонику полосы. Эта гармоника вырабатывается блоком 3 на его втором выходе. Фаза гармоники задается блоком 7 управления на выходе 9,. являющемся непосредственным выходом сдвигового регистра 18. Он фор мирует фазу путем умножения номера отсчета m (.от счетчика 24) на число J/2. Посколысу q, берется равным целой степени двойки, поэтому умнол ение выполняется обычным сдвигом двоичного кода m на(е.оц;2, с|,) разрядов в сторону старших. С выхода умножителя 14 операнды записываются в блок 6 памяти по адресам входа 11, соответствующим значениям кода счетчика 24. Блок 6 памяти состоит из трех одинаковых секций. Указанная запись производится в первую секцию. Единичный режим блока 7 управления заканчивается с переполнением счетчика 24 и установкой его в ноль. При этом импульс переполнения поступает на вход элемента И 23, но не проходит через него, гак как элемент И 23 заперт нулем с выхода элемента НЕ, инвертирующего единичный потенциал шины 27. После это го на шине 27 появляется нулевой потенциал, подача тактовых импульсов на щину 31 прекращается. В этом, нулевом, режиме блока 7 . управления происходит дальнейшая обработка операндов, записанных в первую секцию блока 6 памяти. Об работка происходит так: по исходному, ну левому.; адресу входа 11; вызывается опе .ранд из первой секции блока 6 и подается одновременно на сумматор 13 и умножитель 14 по третьему входу блока 4 (четвейгь1й вход при этом отключается). Одновременно начинает работать формирователь 2.6, Таким образом, предлагаемое устройтво позволяет находить спектр полосового сигнала в пределах ширины полосы, частот и имеет меньший объем оборудоваия, чем известное. зобретения о р м у л а 1. Устройство для вычисления коэффииентов дискретного преобразования Фурье, одержащее входной блок памяти, два уможителя, сумматор, блок памяти подмас- ива и блок памяти коэффи1щентов, первый и второй выходы Которого подключены к первым входам соответственно первого и второго умножителей, вход входного блока памяти является входом устройства, а выход в}4одного блока памяти соединен со вторым входом второго умножителя, выход которого подключен ко входу блока пам51ти подмассива, кыход которого соединен с первым вхЬдом сумматора, выход которого подключен ко входу блока пам&ти яодмассива, отличающееся тем, что, с целью упрощения, оно содержит блок .управления и блок памяти суммы, выход которого объединен с выходом первого умножителя и подключен ко вторым входам сумматора и второго умножителя, выход которого с ъединен с Быходо1 1 сумматора и подкшочен ко входу блока памяти суммы, выход блока памяти подмассива соединен с первьп входом первого умножителя, первый и второй выходы блока управления подключены со ответственно к первому и второму управляющим входам блока памяти коэффициентов, третий и четвертый блока управления . соединены соответственно с первым и вторым управляющими входами блока памяти подмассива, а четвертый и пятый выходы блока управления подключены соответственно к первому и второму управляющим входам блока памяти суммы, вход задания гармоник входной полосы и вход задания режима блока управления являются первым и вторым управляющими входами устройства. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит два счетчика, четыре элемента И, элемент НЕ, элемент ИЛИ, умножитель, кольцевой Сдвиговый регистр, сдвиговый регистр и формирователь адреса, первый выход которого соединен с тактовым входом первого счетчика, первый выход которого соединен со входом сдвигового регистра и первым входом умножителя, вто987рой вход которого соединен с выходом первого элемента И, первый вход которого объединен с первым входом второго элемента И и подключен к первому выходу второго счетчика, тактовый вход кото рого соединен с выходом третьего элемента И, первый вход которого объединен со вторым входом второго элемента И и соединен с выходом элемента НЕ, вход которого объединен с первым входом четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к третьему входу умножителя, выход второго элемента И соединен со вторым входом элемента ИЛИ второй выход первого счетчика соединен со вторым входом третьего элемента И, выходы группы кольцевого сдвигового регистра соединены с соответствукмдими входами группы сдвигового регистра и формирователя адреса, второй выход которого соединен со входом кольцевого сдви6гового регистра, ныхрд умножителя является первым выходом блока, выход сдвигового репистра является вторым выходом блока, третий выход формирователя адреса является третьим выходом блока, первый выход первого счетчика является чет вертым выходом блока, а четвертый выход формирователя адреса является пятым выходом блока, второй вход четвертого элемента И является входом задания гар МОНИК Екодной полосы блока управления, вход элемента НЕ объединен со вторым . входом первого элемента И и является входом задания режима блока управления. Источники информации, принятые во внимание при экспертизе 1.Рабинер Л, и Гоулд Б. и применение цифровой обработки сигналов. М., Мир, 1978. 2,Авторское свидетельство СССР №506883, кл. q 08 F 15/34, 1976 (прототип).

и.гЛ

Авторы

Даты

1981-10-30—Публикация

1979-12-27—Подача