00

о

ОС

Изобретение о пктситги к вм п:ги - те льнон технике и можпт 6brrii пеня зовано в устройствах отс1брпксм1ия и)«{)ормации с растровсй разисрткгч.

Цель изобретения - iroHi. б.;(: родействия устройства.

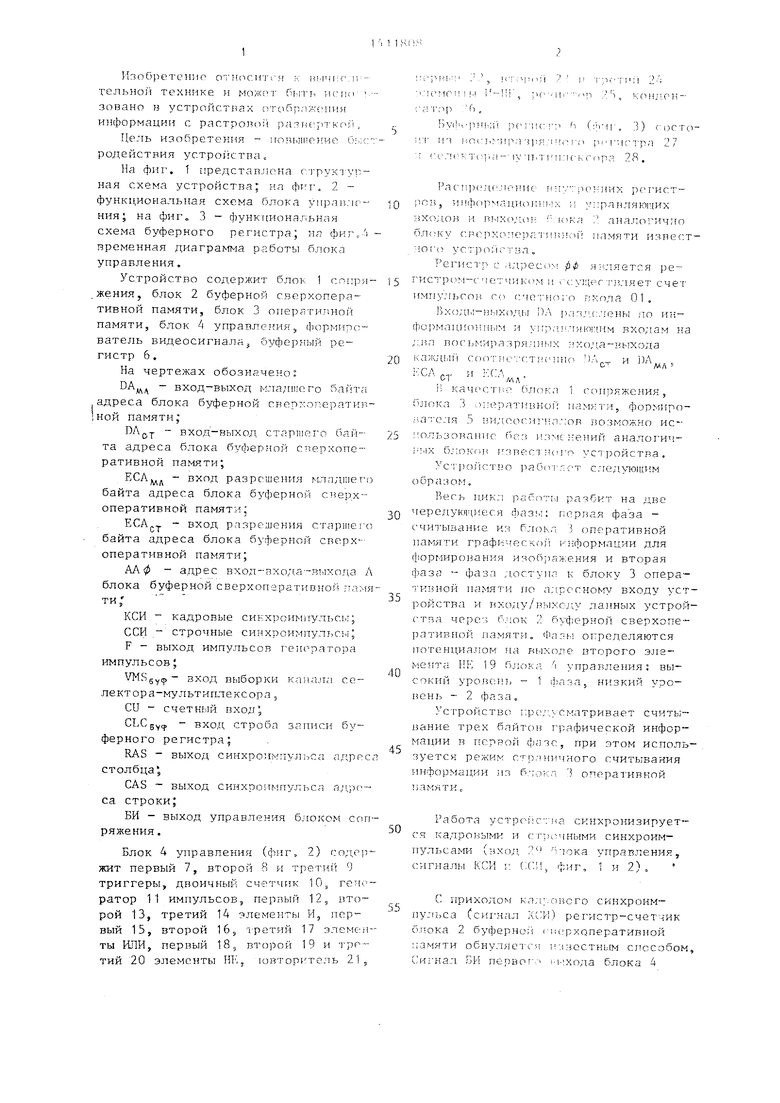

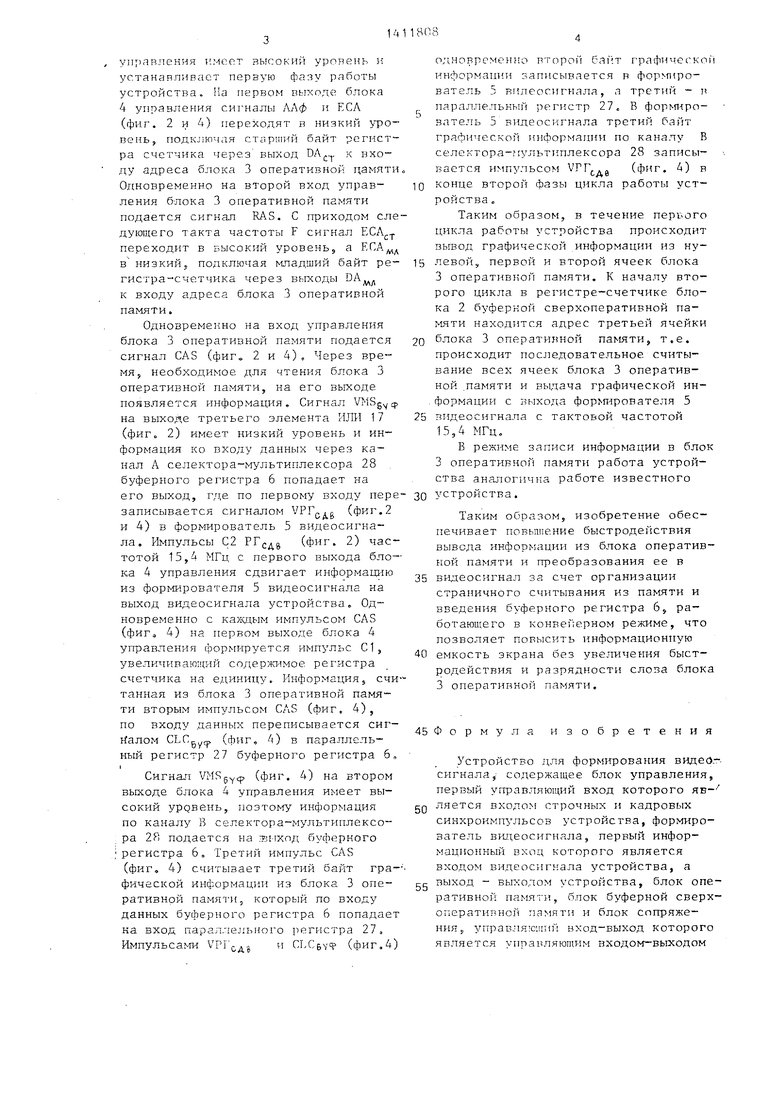

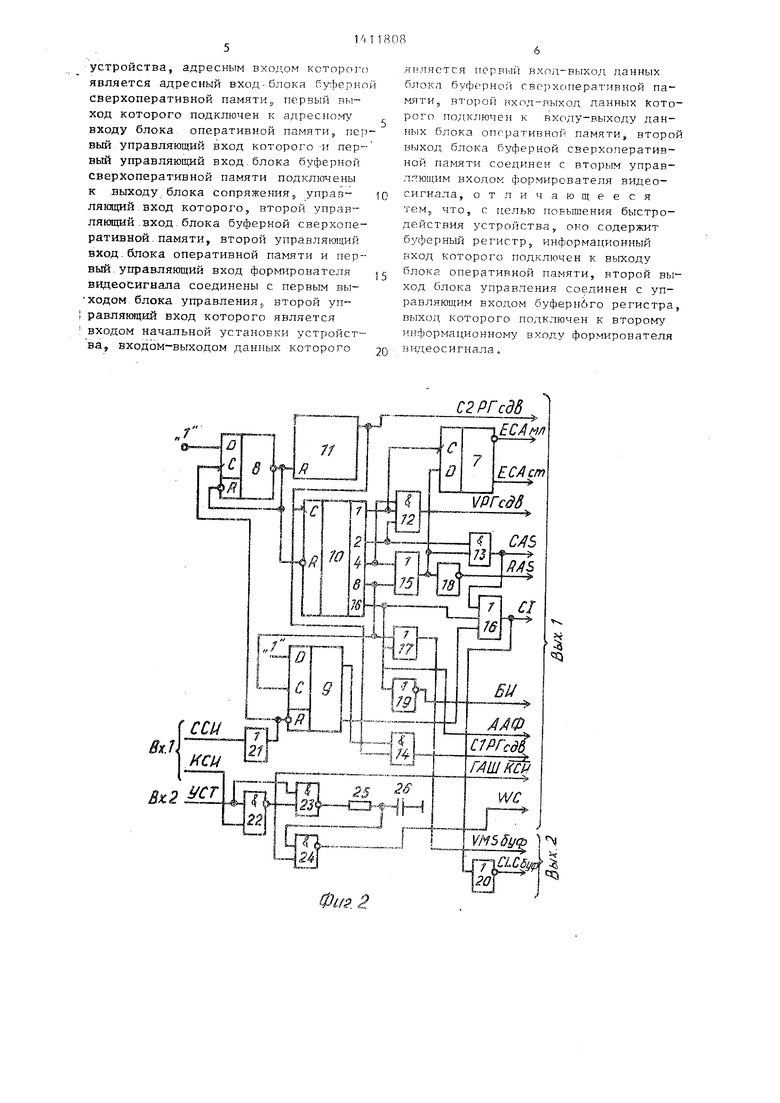

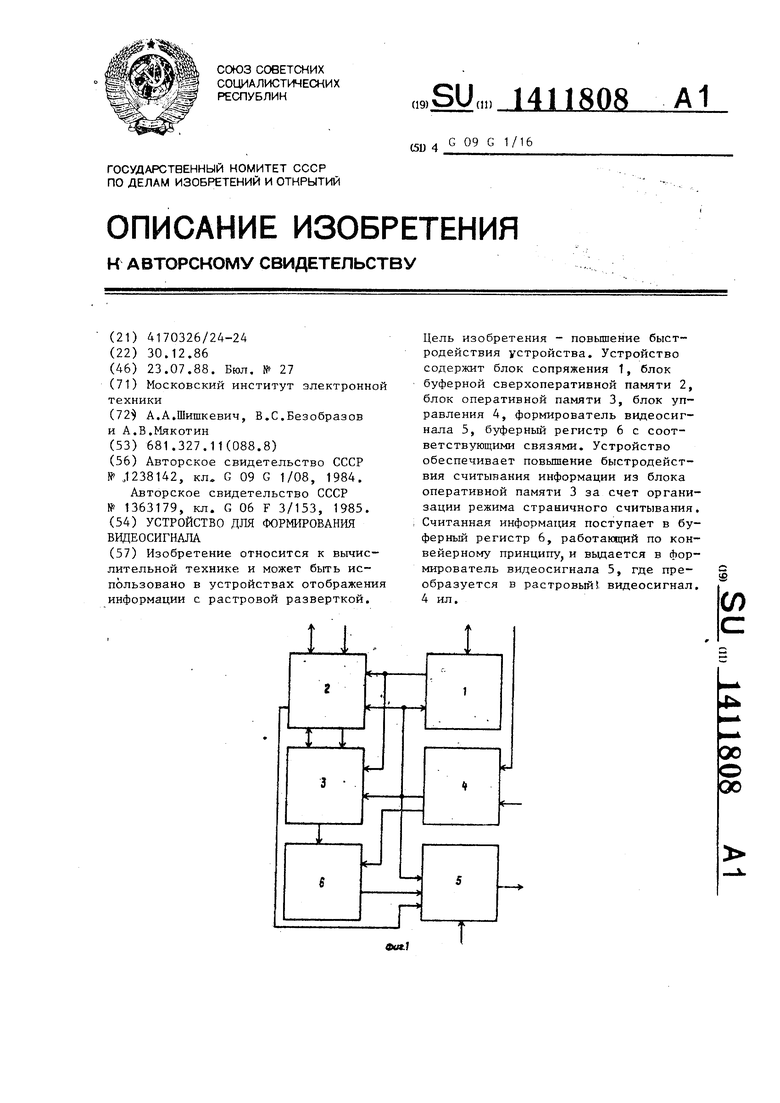

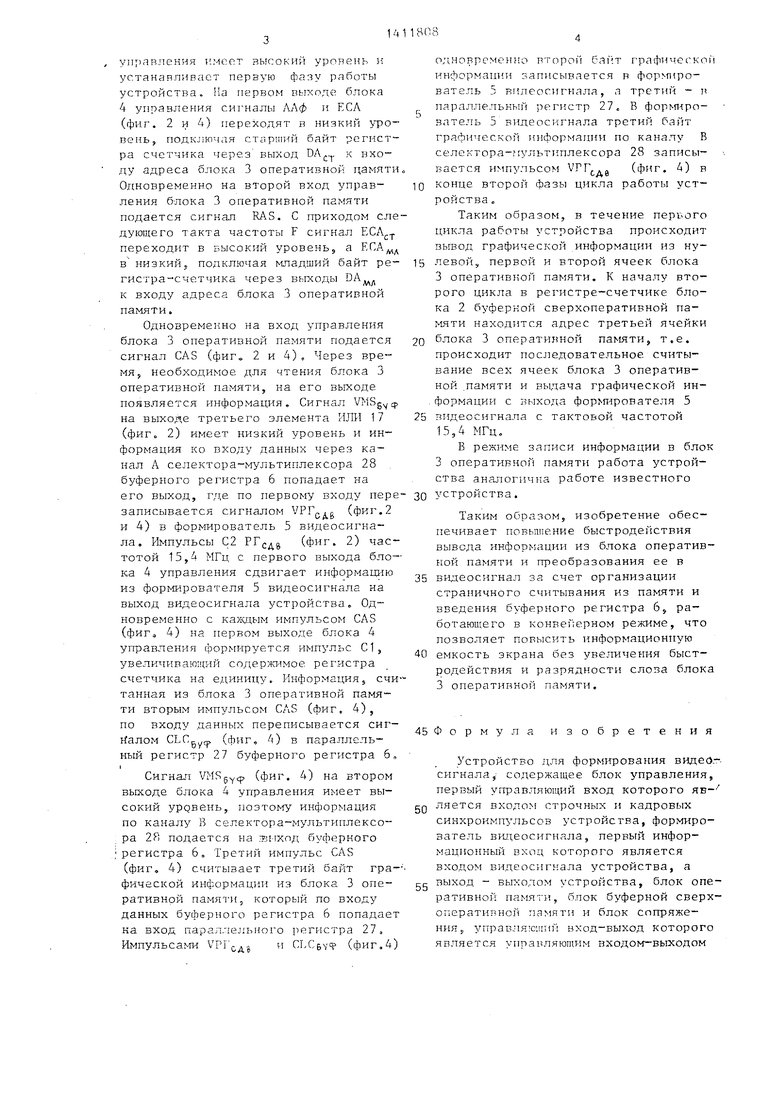

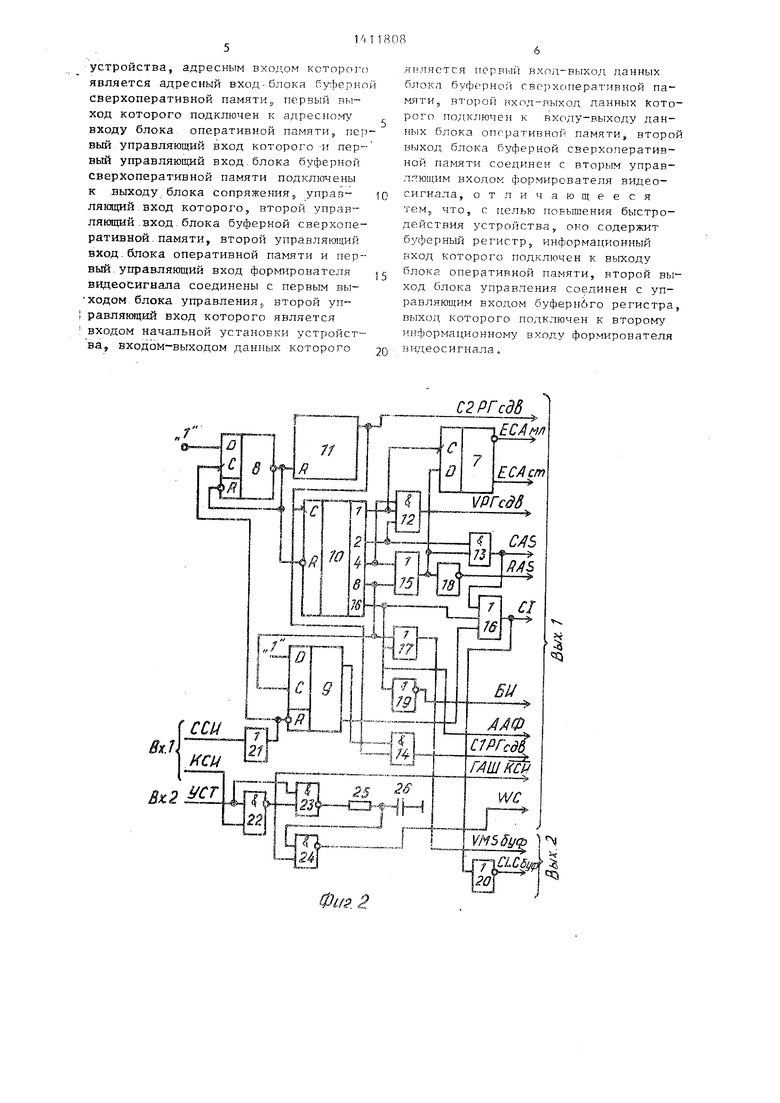

На фиг, 1 гфедстаи.иона п-руктуг- ная схема устройства на фиг-. 2 - функциональная схема блока у11ра1 лг - НИН; на фиг, 3 - функциональная схема буферного регистра; нл фиг.- t временная диаграмма работы блока управления,

Устройство содержит блок 1 сппря- .жения, блок 2 буферной сверхоперативной памяти, блок 3 оперативной памяти, блок 4 управления, формирс - ватель видеосигнала буфер -1ый регистр 6,

На чертежах обозначено: ВА. - вход-выход младшего байта адреса блока буферной сяерг оператир- ной памяти;

DAj, - вход-выход старшего бай- та адреса блока буферной с- ер холе- ративной памяти;

- вход разрешения младшег о байта адреса блока буферной cTiepx- оперативной памяти;

EGA-- - вход разред ения старшегс байта адреса блока буферной сверх-- оперативной памяти;

АА 0 - адрес вход-входа-въГ Сода А блока буферной сверхоперативной памяти,

КСИ - кадровые синхроимпульсы; ССИ .- строчные си;1Хроимпульсь ; F - выход импульсов ге;гс-ратора импульсов;

- ВХОД выборки K;i i;ijia селектора-мультиплексора 5 си - счетный Bxo;j

CLC

БУ

ферного регистра;

RAS - выход синхроимпульса адреса столбца 5

CAS выход синхроимпульса адг)Г -- са строки;

БИ - выход управления блоком сопряжения ,

Блок 4 управления (фиг. 2) содержит первый 7, второй 8 и третий 9 триггеры, двоичный счетчик 10; геис - ратор 11 импульсов, первый 12, нто- рой 13, третий 14 элементы И, первый 15, второй 16, чретий 17 элементы ИЛИ, первый 18, второй 19 и третий 20 элементы НК,

0

5

0

5

0

, aнaлoгiiч; o памяти извес:т45

Pac lpeлi :Ir ИC г н --:-р( регист Ю:, ИИф(lp 1aЦИOl; i :X и :раВЛЯЮ1ЦИХ

;iXo;ioB и RMXCVIOII кж;

блоку CFlfMTXii: e 5fiT IT Hof

ioro ус7-|К1ЙС гва „

Регист; с .1лрес(1 ф является ре г истр(.м-с четчик(1м и v cугцег тн.ляет имг1ул1)Сои С(1 счетИ Ого г;хола 01.

1)Х()лы-иыхо; 1Ы ПА р:1з; .::лень по ин- формаппоппым и укра- . гяюпим входам а ;;iia во(м,миразрял)1ых ; ход а-выход а кажды11 соотнетстнслио Л и 1)Л

ьЛЛ л

ь;сл ,,- и ксл

С-1М л

i; качостие блоки 1 сопряжения, блока 3 ; 1ератииной Т1ам} ти, фор Ягро- л. 5 ви;1;оосигнл. ;ов возможно ис- 1:ользона1П1с без из---и }-:ений аналогич- г,1Х б:;о,ч-()1 извес1Н(Гп ус11 ойства,

ycTi) jiaOnT f T следующим образом.

15есь дик; распты разбит на две чередукпцпеся фаз.:; первая фаза - с читывание из блока оперативной памяти графи-;ескг)1 1--нформации для формирования изображения и вторая фаза - фаза л,оступл к блоку 3 опера- тргвной памяти по ap.pecHONry входу устройства и входу/выходу данных устройства через блок 2 буферной сверхоперативной памяти. )азы определяются потенциалом на выхоле второго элемента НК 19 блокг; . управления; высокий уровевл, - 1 djnsa, низкий уровень - 2 фаза.

Устройство ;рс ;;усматривает счить;- iiaHne трех байтов графической информации в гтервой фазе, при этом используется режим с-1-рпничного считывания инфо1змггции из блокл опег ативной памяти.

0

Ра бота с т и а синхронизируется кадро/: ым г и с гр1-:Чг-1ыми синхроимпульсами (вход, - i-ioKa управления, сигналы КСИ ;i ССМ, фиг, t и 2) .

С приходом кпл .сшого синхроим- пу.чьса Сс} 1 нал КС И) регистр-счет:-.:ик б.пока 2 буферно;-; гмерхоперативной ламяти обнуляется I IHCCTHLW способом, С игнал FjH первог-;- ьмхода блока 4

уп1)авлення и.меет высокий и устанавливает первую фазу работы устройства. На первом выходе блока 4 управления сигналы ЛЛф и ЕСЛ (фиг. 2 и 4) переходят в низкий уровень, подключая старший байт регистра счетчика через выход DA..,, к входу адреса блока 3 оперативной дамятн Одновременно на второй вход управления блока 3 оперативной памяти подается сигнал RAS. С приходом следующего такта частоты F сигнал ЕСЛ. переходит в высокий уровень, а в низкий подключая младший байт регистра-счетчика через выходы DA к входу адреса блока 3 оперативной памяти.

Одновременно на вход управления блока 3 оперативной памяти подается сигнал CAS (фиг 2 и 4), Через время, необходимое для чтения блока 3 оперативной памяти, на его выходе появляется информация. Сигнал VMSgy, на выходе третьего элемента ИЛИ 17 (фиго 2) имеет низкий уровень и информация ко входу данных через канал А селектора-мультиплексора 28 буферного регистра 6 попадает на его выход, где по первому входу перезаписывается сигналом VPF

C(S.6

(фиг.2

и 4) в формирователь 5 видеосигнала. Импульсы С2 РГ(;д (фиг. 2) частотой 15,4 МГц с первого выхода бло ка 4 управления сдвигает информацию из формирователя 5 видеосигнала на выход видеосигнала устройства. Одновременно с каждым импульсом CAS (фига 4) на первом выходе блока 4 управления формируется импульс С1, увели-чивающий содержимое регистра счетчика на единицу. Информация, счи тайная из блока 3 оперативной памяти вторым импульсом CAS (фиг. 4), по входу данных переписывается сиг- (фиг, 4) в параллельный регистр 27 буферного регистра 6, I

Сигнал VMSgYcp (фиг. 4) на втором выходе блока 4 управления имеет высокий уровень, поэтому информация по каналу В селектора-мультиплексора 2Г: подается на ;вмход буферного регистра 6, Третий импульс CAS (фиГф 4) считывает третий байт графической информации из блока 3 оперативной памяти, который по входу данных буферного регистра 6 попадает на вход пapaллeJJьнoгo регистра 27, Импульсами VPГ (дJ и CLCgv (фиг. 4)

одновреме}1но вторО| г бЛ1 .т графической информации записывается в ватель 5 вплеосигнала, а третий - и параллельный регистр 27, В фор№1ро- ватель 5 видеосигнала третий байт графи геской информации по каналу В селектора-пультиплексора 28 записывается ИМПУЛЬСОМ Vrr..., (фиг. 4) в

САИ

g конце второй фазы цикла работы устройства ,

Таким образом, в течение перБого цикла работы устройства происходит вьгвод графической информации из ну-

5 левой, первой и второй ячеек блока 3 оперативной памяти, К началу второго цикла в регистре-счетчике блока 2 буферной сверхоперативной памяти находится адрес третьей ячейки

0 блока 3 оперативной памяти, т,е. происходит последовательное считывание всех ячеек блока 3 оперативной памяти и выдача графической информации с выхода фop fflpoвaтeля 5

5 видеосигнала с тактовой частотой 15,4 МГц,

В режиме записи информации в блок 3 оперативной памяти работа устройства аналогична работе известного

0 устройства.

Таким образом, изобретение обеспечивает повьш1ение быстродействия вывода информации из блока оперативной памяти и преобразования ее в

5 видеосигнал за счет организации страничного считывания из памяти и введения буферного регистра 6, работающего в конвейерном режиме, что позволяет повысить информационную

0 емкость экрана без увеличения быстродействия и разрядности слова блока 3 оперативной памяти.

45 Форму л а изобретения

Устройство для формирования видео-сигнала, содержащее блок управления, первый управляющий вход которого явgg ляется входом строчных и кадровых синхроимпульсов устройства, формирователь видеосигнала, первый информационный вход которого является входом видеосигнала устройства, а

gg выход - выходом устройства, блок оперативной памяти, блок буферной сверх- операти7 ной памяти и блок сопряжения „ управляющий вход-выход которого является управляющим входом-выходом

устройства, адресным входом которого является адресный вход-блока Пуфернор сверхоперативной памяти,, первый выход которого подключен к aдpecнo fV входу блока оперативной памяти, первый управляющий вход которого I первый управляющий вход.блока буферной сверхоперативной памяти подключены к выходу блока сопряжения, .управляющий вход которого, второй управляющий .вход . блока буферной сверхоперативной, памяти, второй управляющий вход.блока оперативной памяти и первый, управляющий вход формирователя видеосигнала соединены с первым вы- ходом, блока управления„ второй уп- равляющий вход которого является входом начальной установки устройства, входом-выходом данных которого

является первый вход-выход данных блока буфефной свез хоперативной памяти, второй вход-пыход данных Которого подключен к входу-выходу данных блока оперативной памяти, второй выход блока буферной сверхоперативной памяти соединен с вторым управляющим входом формирователя видеосигнала 5 отличающееся

тем, что, с целью повышения быстродействия устройства, оно содержит буферный регистр, информадионный вход которого подключен к выходу

блока оперативной памяти, второй выход блока управления соединен с управляющим входом буфернбго регистра, выход которого подключен к второму информационному входу формирователя

}м-1,т;еосигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на экране растрового дисплея | 1985 |

|

SU1363179A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ ЭВМ С ДИСПЛЕЕМ | 1992 |

|

RU2051410C1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для редактирования и контроля управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки | 1986 |

|

SU1451676A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах отображения информации с растровой разверткой. Цель изобретения - повьшение быстродействия устройства. Устройство содержит блок сопряжения 1, блок буферной сверхоперативной памяти 2, блок оперативной памяти 3, блок управления 4, формирователь видеосигнала 5, буферный регистр 6 с соответствующими связями. Устройство обеспечивает повышение быстродействия считывания информации из блока оперативной памяти 3 за счет организации режима страничного считывания. Считанная информация поступает в буферный регистр 6, работающий по конвейерному принципу и выдается в формирователь видеосигнала 5, где преобразуется в растровый, видеосигнал. 4 ил. (Л

в ft

R

2Jf--C3 f -|M

T vfoAI

01/.

J

С2РГсдв

ЕС А cm

МРГсдд

VMSSy

N,

CLCSij 5

Vf1

li

OQ

С L С

Вх. дан

CLC

U0

Фаза 1

ЕСЛсг

МРГМ ВЦ

Редактор С.Патрушева

Составитель О.Цапко Техред Л.Сердюкова

Заказ 3657/А7

Тираж 459

ВНИ11ПИ Государственного комитета СССР

по делам изобретений и открытш 113035, Москва, Ж-35, Раушская наб., д.

v

Щ

А7

2В

8 Вых.

27

-

Фиг.З

IФаза 2

ilJlJT-TLnJUir

Фи2. 4Корректор В.Романенко

Иоллисное

| Авторское свидетельство СССР № ,1238142, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения графической информации на экране растрового дисплея | 1985 |

|

SU1363179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1986-12-30—Подача