с

О1

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор базисных функций | 1987 |

|

SU1503042A2 |

| Генератор базисных функций | 1988 |

|

SU1524036A1 |

| Генератор базисных функций | 1986 |

|

SU1319013A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Устройство для вычисления гиперболических функций | 1977 |

|

SU732888A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Цифровой генератор гармонических сигналов | 2015 |

|

RU2616877C1 |

Изобретение относится к вычислительной технике и может быть использовано для генерирования базисных функций, например, при спектральном анализе случайных процессов. Цель изобретения - расширение функциональных возможностей за счет генерации базисных функций с учетом знака зталона. Поставленная цель достигается за счет введения N/2 одноразрядных сумматоров. В функциональный преобразователь дополнительно введены первый и второй дешифраторы, блок памяти, коммутатор. 1 з.п. ф-лы, 2 ил.

14)

Изобретение относится к вычислительной технике и может быть использовано для генерирования базисных функций, например, при спектральном анализе случайных процессов.

Цель изобретения - расширение функциональных возможностей за счет генерации базисных функций с учетом знака эталона и повышение достовер- ности результата за счет исключения неопределенностей типа х/о и о/о.

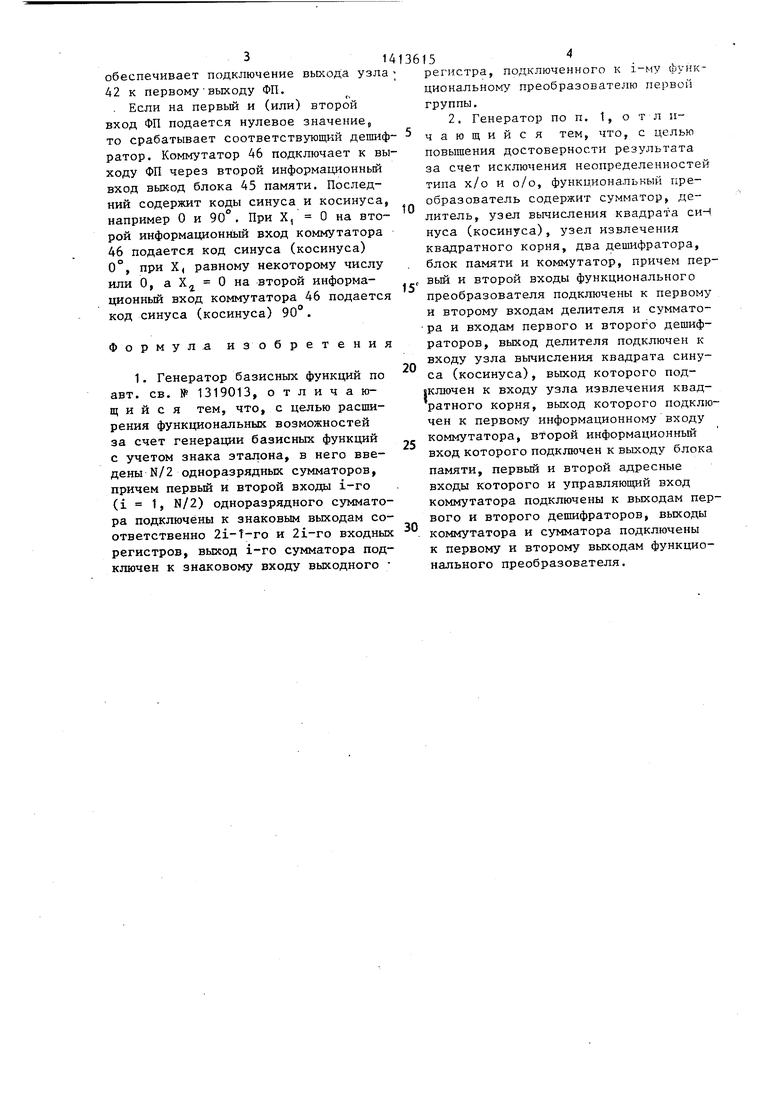

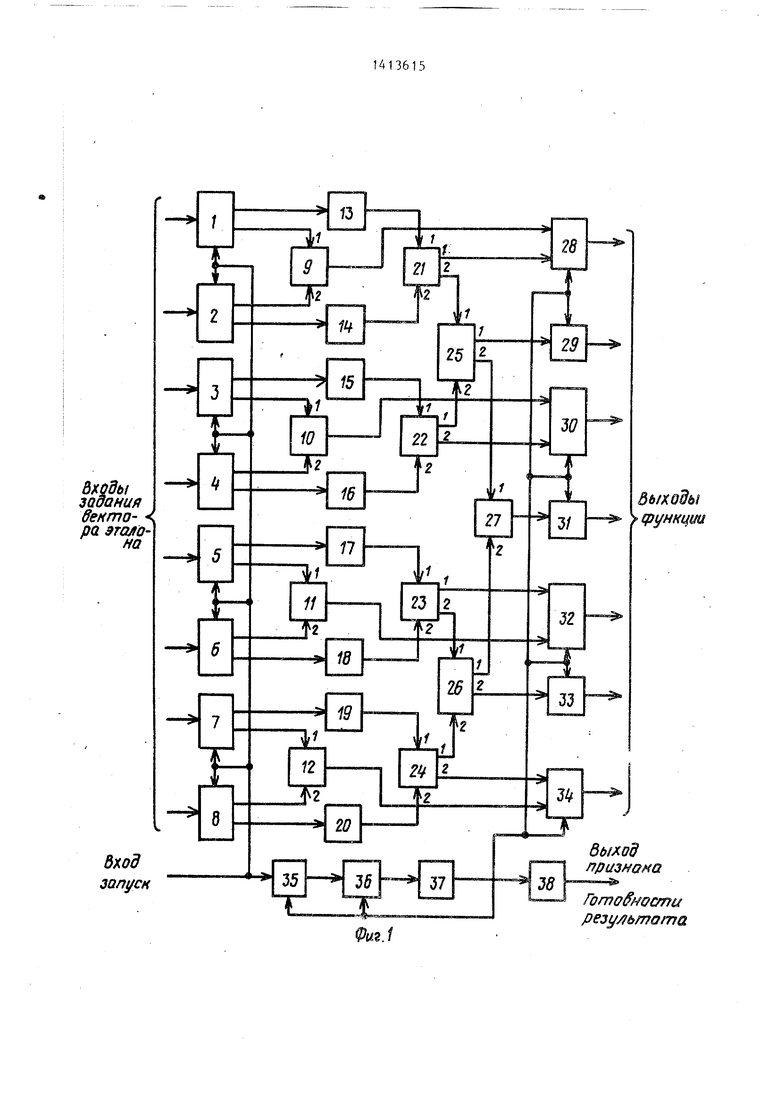

На фиг. 1 приведена структурная схема генератора на фиг. 2 - схема функционального преобразователя.

Генератор базисных функций (ГБФ) содержит (фиг.1) входные регистры 1 - 8, одноразрядные сумматоры 9-1 квадраторы 13 - 20, функциональные преобразователи (ФП) 21 - 27р выход- ные регистры 28 - 34, генератор 35 импульсов (ГИ), счетчик 36, дешифратор 37 и триггер 38. ФП (фиг. 2) содержит сумматор 39, делитель 40, узел 41 вычисления квадрата синуса (косинуса), узел 42 извлечения квадратного корня, дешифраторы 43 и 44, блок 45 памяти и коммутатор 46.

Генератор работает следующим образом.

ГБФ работает аналогично устройству-прототипу. Перед началом работы устройства ГИ 35 выключен, счетчик 36 и триггер 38 установлены в исходное, например, нулевое состояние. При поступлении на вход запуска устройства импульса запуска включается ;ГИ 35 и с входов задания векторов эталона в регистры 1-8 записывается эталон сигнала. Частота импульсов на выходе ГИ 35 и емкость счетчика 36 подбираются так, чтобы время формирования на входе дешифратора ,37 определенной кодовой комбинации было равно времени преобразования эталона в коэффициенты базисной системы функций.

Отсчеты эталона с выходов регистров 1 - 8 подаются через квадраторы 13 - 20 на входы ФП 21 - 27. На входы ФП 22 подаются отсчеты с выходов квадраторов 15 и 16, на входы ФП 21 с выходов квадраторов 13 и 14, на входы ФП 23 - с выходов квадраторов 17 и 18, на входы ФП 24 - с выходов квадраторов 19 и

На первых выходах ФП 21 - 27 формируются коды синусов и косинусов искомой базисной системы функций. Н

,

Q

5

0 5

5

0

5

0

5

0

вторых выходах ФП 21-24 формируются соответственно суммы квадратов отсчетов Х - Ц, Ц. XI, Х2, Ц+Х1. Эти суммы подаются соответственно на первый и второй входы ФП 25, на пер- вьй и второй входы ФП 26.

На вторых выходах ФП 25 и 26 формируются соответственно суммы квадратов отсчетов Х2+ Ц+ Ц+ Ц и Ц+ X|-i- Х|. Эти суммы подаются на первый и второй входы ФП 27. В момонт окончания работы ФП 27 на вход записи выходных регистров 28 - 34 пода- - ется импульс с дешифратора 37 и полученные значения синусов и косинусов базиса записываются в выходные регистры 28 - 34. Одновременно триггер 38 устанавливается в состояние, информирующее о завершении формирования базисной системы функций.

Формирование базисных функций с учетом знака эталона обеспечивается одноразрядными сумматорами 9 - 12, на входы которых подаются потенциалы знаковых разрядов с знаковых выходов входных регистров 1 - 8. На первый и второй входы сумматора 9 подаются потенциалы знаковых разрядов соответственно с знаковых выходов входных регистров 1 и 2, на первый и второй входы сумматора 10 - с знаковых выходов входных регистров 3 и 4, на первый и второй входы сумматора 11- с знаковых выходов входных регистров 5 и 6; на первьй и второй входы сумматора 12 - с знаковых выходов входных регистров 7 и 8. Результат сложения по модулю 2 (, , ) подается с выходов сумматоров 9 - 12 на входы знака синуса соответственно выходных регист оя 28, 30, 32 и 34, в которые запЧ .1ва- ются коды синусов (косинусор р.ж ьей матрицы Гуда. От знака отсчетов эта- ,лона зависит ядро третьей матрицы Гуда.

Принцип работы ФП 21 - 27 состоит в следующем. Входные данные, например Х и Х поступают на первый и второй входы сумматора 39 и делителя 40. Сумма Х + Х с выхода сумматора подается на второй выход ФП. На выходе делителя 40 формируется отношение вида Х /Х, по которому в узле 41 вычисляются значения , и ,. Последние через узел 42 подаются на первьй вход коммутатора 46, который в исходном состоянии

3,

обеспечивает подключение выхода узла 42 к первомувыходу ФП.

. Если на первьй и (или) второй вход ФП подается нулевое значениеs то срабатывает соответствующий дешифратор. Коммутатор 46 подключает к выходу ФП через второй информационный вход выкод блока 45 памяти. Последний содержит коды синуса и косинуса, например О и 90 . При X, О на второй информационный вход коммутатора 46 подается код синуса (косинуса) 0°, при Х( равному некоторому числу или О, а Х О на второй информационный вход коммутатора 46 подается код синуса (косинуса) 90°.

Формула изобретения

to

15

3615

регистра, подключенного к i-му функциональноьту преобразователю первой группы.

2, Генератор по п. 1, о т л п- чающийся тем, что, с целью повышения достоверности результата за счет исключения неопределенностей типа х/о и о/о, функциональный преобразователь содержит сумматор, делитель, узел вычисления квадрата син, нуса (косинуса), узел извлечения квадратного корня, два дешифратора, блок памяти и коммутатор, причем пер- , вый и второй входы функционального преобразователя подключены к первому и второму входам делителя и сумматора и входам первого и второго дешифраторов, выход делителя подключен к входу узла вычисления квадрата синуса (косинуса), выход которого под- |ключен к входу узла извлечения квадратного корня, выход которого подключен к первому информационному входу коммутатора, второй информационный вход которого подключен к выходу блока памяти, первый и второй адресные входы которого и управляющий вход коммутатора подключены к выходам первого и второго дешифраторов, выходы коммутатора и сумматора подключены к первому и второму выходам функционального преобразователя.

0

0

д)(оды

заданий венто- рй эталона

бход запусн

epi/нкцт

резу/}ьтата

39

kO

fiJ

kl

Ml.

h5

if6

Фиг. 2

| Генератор базисных функций | 1986 |

|

SU1319013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-16—Подача