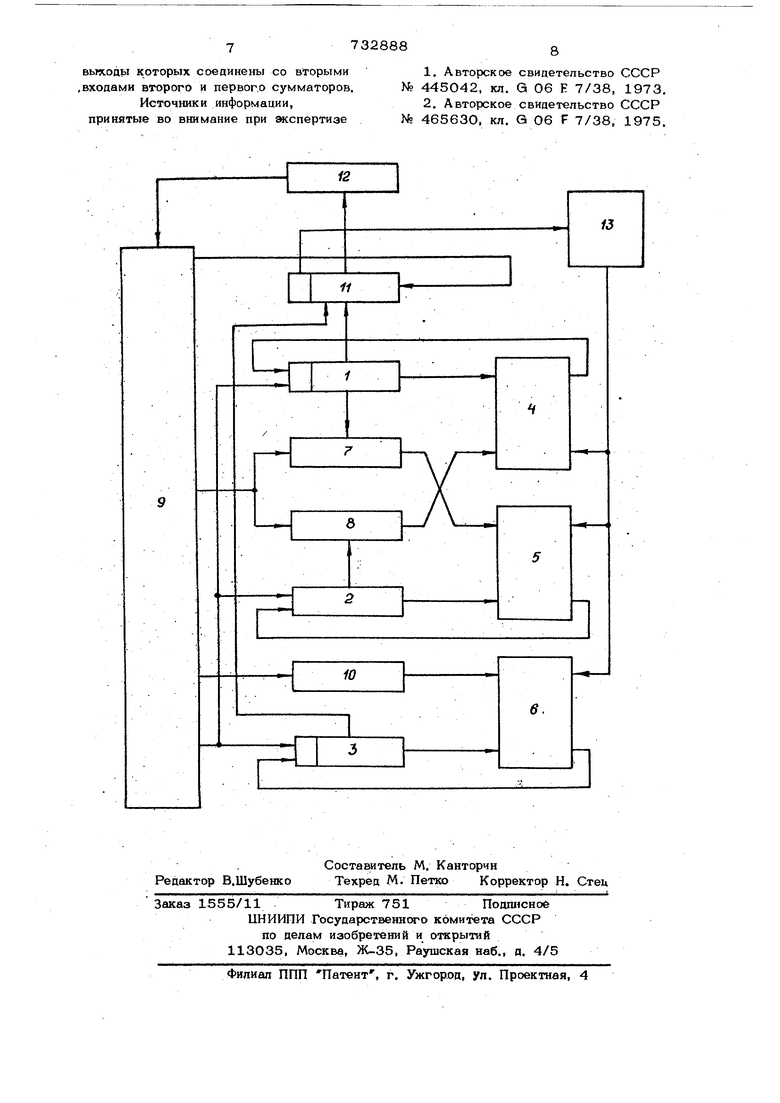

Изобретение относится к цифровой вы- .числительной технике и может найти применение при аппаратурном вычислении эл ментарных функций, в частности в специализированных цифровых вычислительных машинах. (CIIBM), работающих в последо.вательиом двоичном коде с фиксированной запятой. Известно устройство, работающее по алгоритму Волдера и позволяющее вычислять прямые и обратные тригонометрические функции {l . Однако в этом устройстве невозмож но вычислять гиперболические функции,, необходимые при решении ряда задач обработки информации. Известно устройство для вычисления ..обратного гиперболического тангенса (секанса), содержащее три накапливающих сдвигающих регистра, три одноразрядных сумматора, блок псевдочастного, блок памяти,, блок сравнения, блок управления,и два сдвигающих регистра. Выходы младших разрядов первого, второго и третьего накапливающих сдвигающих регистров соединены соответственно с, первым входом первого, второго и третьего сумматоров, выходы которых подключены к входам старших разрядов соответствующих накапливающих регистров. Вход блока псевцочастного соединен со знаковым разрядом первого накапливаюиюго регистра, а выход подключен ко входам управления сумматоров. Разряды мантиссы первого накапливающего регистра соединены со входами блока сравнения, выход которого подключен к входу блока управления. Управляющие входы всех регистров и блока памяти соединены с соответствующими выходами блока управления, а выходы первого и второго сдвигающих регистров подключены к вторым управляемым входам второго и первого сумматоров. Выход блока памяти соединен со вторым управляемым входом третьего сумматора 2 . Недостатком данного устройства является невозможность вычисления гипер37бопического Sli или cli i a также использование сдвигающих регистров в цепи перекрестной связи межау содержимым первого и второго накапливающих сдвигаюших регистров и вторыми входами второго и первого сумматоров соответст венно. Это приводит к тому, что перед каждой итерацией содержимое сдвигающих регистров необходимо последовательно сдвигать вправо на число разрядов, равное номеру итерации, причем сдвиг должен быть модифицированным, что увеличивает время вычисления на Т- I -гч где П - число разряйов. Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства за счет вычисления функций гиперболического синуса, и косинуса. Цель достигается тем, что устройство для вычисления гиперболических фун ций, содержащее, три сдвигаюших регистра, три одноразрядных сумматора, ключ, блок памяти, схему сравнения с константой, блок управления, причем выходы мл ших разрядов первого второго и третьего сдвигающих регистров соединены с первыми входами соответственно первого вт рого и третьего сумматоров, выходы которых соединены со входами старших раз рядов соответствующих сдвигающих регистров, выход ключа соединен со входами управления сумматоров, выход схемы сравнения с константой соединен со входом блока управления, второй вход треть го сумматора соединен с выходом блока памяти, управляющие входы сдвигающих регистров соединены с первым выходом блока управления, управляющий вход бло. ка памяти соединен со вторым выходом блока управления, содержит три коммутатора, управляющие входы которых соединены соответственно с третьим и че1 вертым выходом блока управления, выходы знакового и информационного разрядов первого и третьего сдвигающих ре гистров через первый коммутатор соединены соответственно со входом ключа и группой входов схемы сравнения с кон стантой, информационные выходы разрядов первого и второго сдвигаюших регистров соединены соответственно со вх дами второго и третьего коммутаторов, выходы которых соединены со вторыми в дами второго и первого сумматоров. 8 На чертеже представлена функциональная схема устройства. Устройство состоит из трех рециркуяционных ячеек. В основу каждой из них входит сдвигающий регистр 1 для первой ячейки, сдвигающий регистр 2 для второй ячейки и сдвигающий регистр 3 ля третьей ячейки, выходы этих регистров поданы соответственно на первые входы одноразрядных сумматоров 4, 5 и 6. Выходы сумматоров 4,5 и 6 соединены с последовательными входами сдвигающих регистров 1,2 и 3. Параллельные выходы регистров 1 и 2 подключены к одноименным входам коммутаторов 7 и В. Выход коммутатора 7 соединен совторым входом сумматора 5, а выход коммутатора 8 подключен к второму входу сумматора 4. Управляющие входы коммутаторов 7 и 8 объединены между собой и соединены с выходами блока 9 управления. Выход блока 1О памяти, управляющие входы которого соединены с блсжом 9 управления, подключен к второму входу сумматора 6. . Параллельные выходы регистров 1 и 3 поданы .на информационные входы коммутатора 11, управляющий вход которого подключен к. блоку 9 управления и обеспечивает, в зависимости от вычисляемой фушсции, подключение мантиссы регистров 1 или 3 на входы схемы сравнения с константой 12, а знака на ключ 13. Выход схемы сравнения с константой 12 подключен к входу блока 9 управления. Выход ключа 13 подсоединен к входам yпpaвлe шя сумматоров 4, 5 и 6. Устройство реализует следующие рекуррентные соотношения; ь.(2) N.. ,4.- r- -i«- . где , , - содержимое регистров 1, 2, 3 после вьтолнения i -ой операции;О Slgtt Т - при вычислении ar-fll и sect) или q - sig-n при вычислении и Ct . Перед началом вычислений в регистр 1 записывается аргумент при вычислении аг-ЬЬ и secli а при вычислении Sll и cii устанавливается в нулевое состояние. В регистр 2 записывается единицы. Регистр 3 устанавливается в нулевое состояние при выполнении ar-fch и gecll , а при вьтолнении eti и записывае1х;я аргумент Т. В каждой итерации блок управпедая-9 выдает пачку импульсов на управляющие входы регистров 1, 2 и 3 и блока памяти 10. Количество импульсов в пачке ра но разрядности регистров. Коммутаторы 7 и 8 подключают разряд регистров 1 и 2 с номером, соответ ствующим номеру итерации ко второму входу сумматсров 5 и 4. Если при вычисленииar-thMseclieigny положительный то ключ 13 должен выработать сигналы, позволяющие сумматорам 4 и 5 производить, операцию вычитания, а сумматору 6 операцию сложения. Если eigfH i от рицательный, то ключ 13 должен вьфабоTafb сигналы, позволяющие сумматорам 4 и 5 производить операцию сложения, а сумматору 6 операцию вычитания. При вычитании S-h и c1i ключ 13 вырабатывает сигналы, обеспечивающие выполнение обратных операций сумматорами. Таким образом, в каждой итерации на сумматоре 4 происходит выполнение соотношения (2), на сумматоре 5 - соотношение (З), на сумматоре 6 - соотношение (4). В связи с тем, что сдвигающие регистры 1 и 2 при вьшолнении сложения заполняются одновременно рюзультатом вычисления, а вторые слагаемые соотношений (2) и (З) должны использовать ся с модифицированным сдвигом, то при равенстве кода номера итерации с инверсным кодом номера такта коммутаторы 7 и 8 начинают подавать на второй вход сумматора 5 и 4 знаковый разряд регистров 1 и 2, который в это время оказывается на разряде регистров номером равным номеру итерации и при сле.дующем такте сдвигается вправо, т.е. коммутаторы следят за знаковым разрядом до конца итерации. Тем самым хэбес печивается модифицированный сдвиг. Для устранения зон несходимости сис л.-. . n-if мы базисных функций dPtli необходимо повторять итерации с номерами, опре деляемыми по формуле 1 1 , где И 1, 2, 3 ... После вьтопнения и итераций содержимое, регистра 1 становится равным ну лю при вычислении artli и ,или К) z к ch ; содержимое регис ра 2 становится равным KjiSecVtY или К -ЬЬТ ; а содержимое регистра 3 ст новится равным c irtii Ч при вычислении dirtli и SfeCh или равным нулю при sli и c-h . Для подавляющего большинства значений аргумента процесс сходится на итерации номер которой . При этом в регистрах 1 или 3, в зависимости от выполняемых групп функций, вСе разряды становятся равными нулю, а результаты вычисляемых функций получаются на регистрах 2 и 3 или 1 и 2. Схема сравнения с константой (в данном случае с нулем) выдает сигнал окончания операции. Блок 9 управления по этому сигналу прекращает подачу тактовых импульсов. Этим обеспечивается асинхронный режим. Кроме того, блок 9 управления при итерациях ЗП -f 1 не изменяет номер итерации и она повторяется. Формула изобретения Устройство для вычисления гиперболических функций, содержащее три сдвиговых регистра, три одноразрядных сумматора, ключ, блок памяти, схему сравнения с константой, блок управления, причем выходы младших разрядов первого, второго и третьего сдвигающих регистров соединены с первыми входами соответственно первого, второго и третьего . сумматоров, выходы которых соединены со входами старших разрядов соответствующих сдвигаюших регистров, выход ключа соединен со входами управления сумматоров, выход схемы сравнения с константой соединен со входом блока управления, второй вход третьего сумматора соединен с выходом блока памяти, управляющие входы сди1гающих регистров соединены с первым выходом блока управления, управляющий вход блока памяти соединен со вторым выходом блока управления, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей устройства за счет вычиспения функшй гиперболического синуса и косинуса, оно содержит три коммутатора, управляющие входы которых соединены соответственно с третьим и четвертым выходами блсжа управления, выходы знакового и информационного разрядов первого и третьего сдвигающих регистров через первый коммутатор соединены соответственно со входом ключа и группой BXOUOB схемы сравнения с константой, информационные выходы разрядов первого и второго сдвигающих регистров соединены соответственно со входами второго и третьего коммутаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1462300A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

Авторы

Даты

1980-05-05—Публикация

1977-10-10—Подача