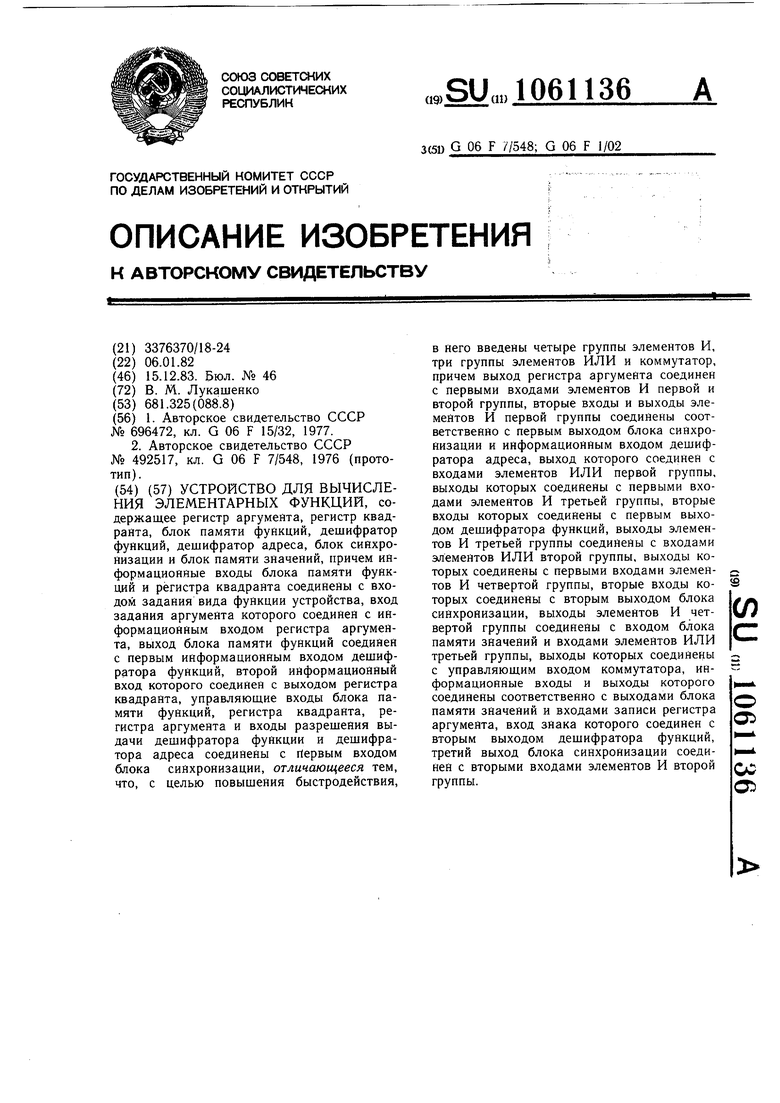

Изобретение относится к вычислительiой технике и предназначено для использования в информационно-измерительных системах, дискретных преобразователях координат, в чистемах, связанных с функциональными преобразователями дискретной информации.

Известно устройство, содержащее блок памяти, регистр, информационные входы которого соединены с информационными входами устройства, выходы регистра через первую группу элементов И соединены с входами блока адресации, а через вторую группу элементов И подключены к входам устройства. Выходы блока адресации подключены к входам первого коммутатора, управляющие входы первой группы и второй элементов И первого коммутатора и регистра соединены с выходом блока управления. Устройство содержит также одну группу элементов ИЛИ, распределительный блок и дополнительные коммутаторы, входы которых соединены с выходами блока адресации, управляющие входы подключены к выходу блока управления, выходы коммутаторов соединены соответственно с входом блока памяти и через группу элементов ИЛИ подключены к управляющим входам распределительного блока. Выходы блока па.мяти через распределительный блок подключены к счетным, входам регистра 1.

Это устройство также воспроизводит только одну элементарную функцию. Однако вычислительный процесс, как правило, не ограничивается вычислением одной функции, поэтому для вычисления некоторого числа элементарных функций потребуется создать для каждой функции свое устройство, каждое из которых будет содержать одинаковые блоки; регистр, блок памяти, два блока элементов И, элементы ИЛИ, распределительный блок, блок дешифровки адреса, коммутаторы. Это устройство имеет больщую потребляе.мую мощность и низкую надежность.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее п-разрядный регистр входного аргумента, однозарядный элемент памяти функционального назначения (sinx/cosx) двухразрядный регистр определения квадрата, выходы п-разрядного регистра подключены к входам мультиплексора непосредственно или через компаратор входа, управляющий вход которого подключен к перво.му выходу дешифратора функционального назначения, первые входы которого соединены с выходами одноразрядного элемента памяти, а вторые входы подключены к выходам двухразрядного регистра определения квадрата, второй выход дещифратора подключен к знаковому входу компаратора выхода, вход которого подключен к входу функционального преобразователя, вход которого соединен с выходом мультиплексора, выходы компаратора выхода подключены к входам регистра косинуса (cosx) и к входам регистра синуса (sinx), выходы регистров cos х, sin х подключены или к выходам устройства вычисления тригонометрических функций от входного угла, или к первым входам схемы разделения подключен выход регистра cos х, вторые входы соединены с выходом регистра sin х, а выходы схемы разделения подключены к выходам

0 устройства, управляющие щины подключены к соответствующим щинам устройства управления.

Кроме того, преобразователь функций содержит регистр входа, четыре блока памяти, каждый из которых состоит из де шифратора адреса и числового блока памяти и сумматора, причем входы регистра входа являются входами преобразователя функции, а соответствующие выходы регистра хода подключены к соответствуюQ щим входам дещифраторов адреса, выходы которых соединены с соответствующими входами числовых блоков памяти, выходы которых подключены к соответствующим входам сумматора, выходы которого являются выходами преобразователя функ5 ции 2. .

Время вычисления тригонометрических функций secx, cosec X, ctgx, tgx в данном устройстве определяется по формуле

(1заБвх + ъы6 + м+t -ft}an-y

+ tдeл,(1)

0 где .BX - время записи входных данных; t - время обработки информации

в мультиплексоре; i-Bbie - время выборки; ijafj.y- время записи значения функций;5t(, - время обработки информации

в компараторе; 1дел- время выполнения операции

деления;

1 - время воспроизведения функQции sinx или cosX.

1ф 21запвх + t, + tct4i(2)

гдеtcM -время выполнения операции суммирования двух п-разрядных слагаемых.

Из формулы (1) видно, что быстродей5 ствие устройства невелико.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для вычисления элементарных

0 функций, содержащее регистр аргумента, регистр квадранта, блок памяти функций, дешифратор функций, дешифратор адреса, блок синхронизации и блок памяти значений, причем информационные входы блока

памяти функций и регистра квадранта соединены с входом задания вида функции устройства, вход задания аргумента которого соединен с информационным входом регистра аргумента, выход блока памяти функций соединен с первым информационным входом дешифратора функций, второй информационный вход которого соединен с выходом регистра квадранта, управляющие входы блока памяти функций, регистра квадранта, регистра аргумента и входы разрешения выдачи дешифратора функции и дешифратора адреса соединены с первым выходом блока синхронизации, дополнительно введены четыре группы элементов И, три группы элементов ИЛИ и коммутатор, причем выход регистра аргумента соединен с первыми входами элементов И первой и второй групп, вторые входы и выходы элементов И первой группы соединены соответственно с первым входом блока синхронизации и информационным входом дешифратора адреса, выход которого соединен с входами элементов ИЛИ первой группы, выходы которых соединены с первыми входами элементов И третьей группы, вторые входы которых соединены с первым выходом дешифратора функций, выходы элементов И третьей группы соединены с входами элементов ИЛИ второй группы, выходы которых соединены с первыми входами элементов И четвертой группы,, вторые входы которых соединены с вторым выходом блока синхронизации, выходы элементов И четвертой группы соединены с входом блока памяти значений и входами элементов ИЛИ третьей группы, выходы которых соединены с управляюшим входом коммутатора, информационные входы и выходы которого соединены соответственно с выходами блока памяти значений и входами записи регистра аргумента, вход знака которого соединен с вторым выходом дешифратора функций.

третий выход блока синхронизации соединен с вторыми входами элементов И второй группы.

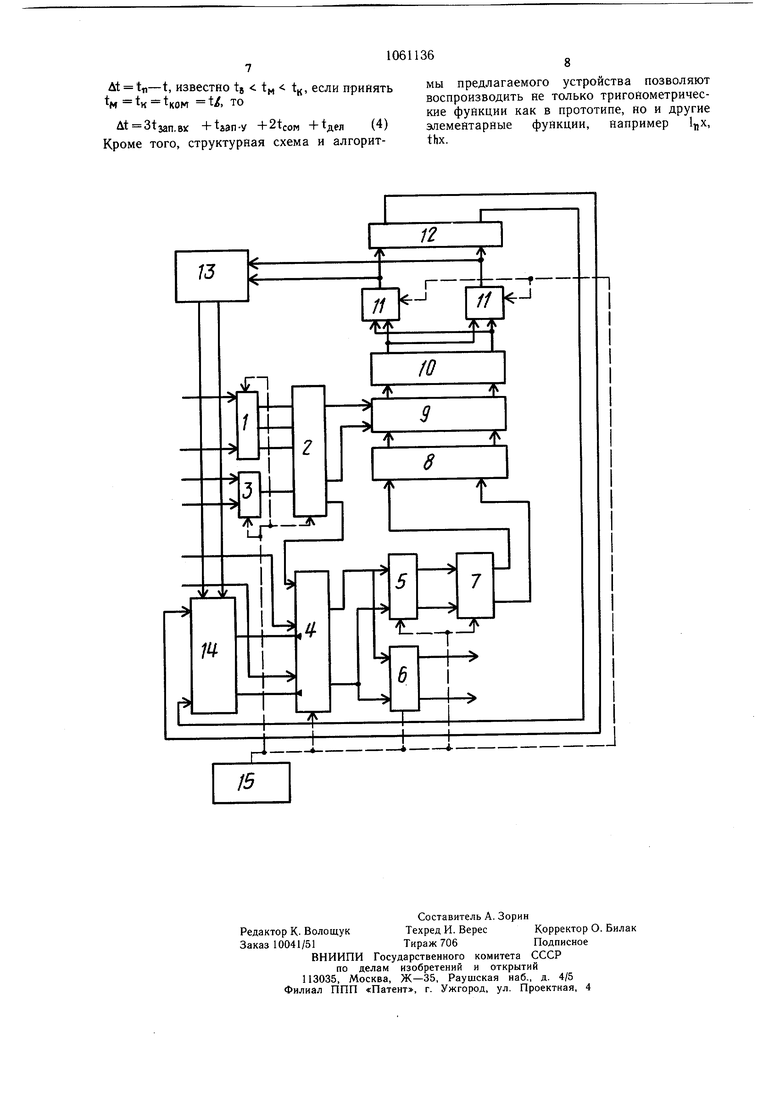

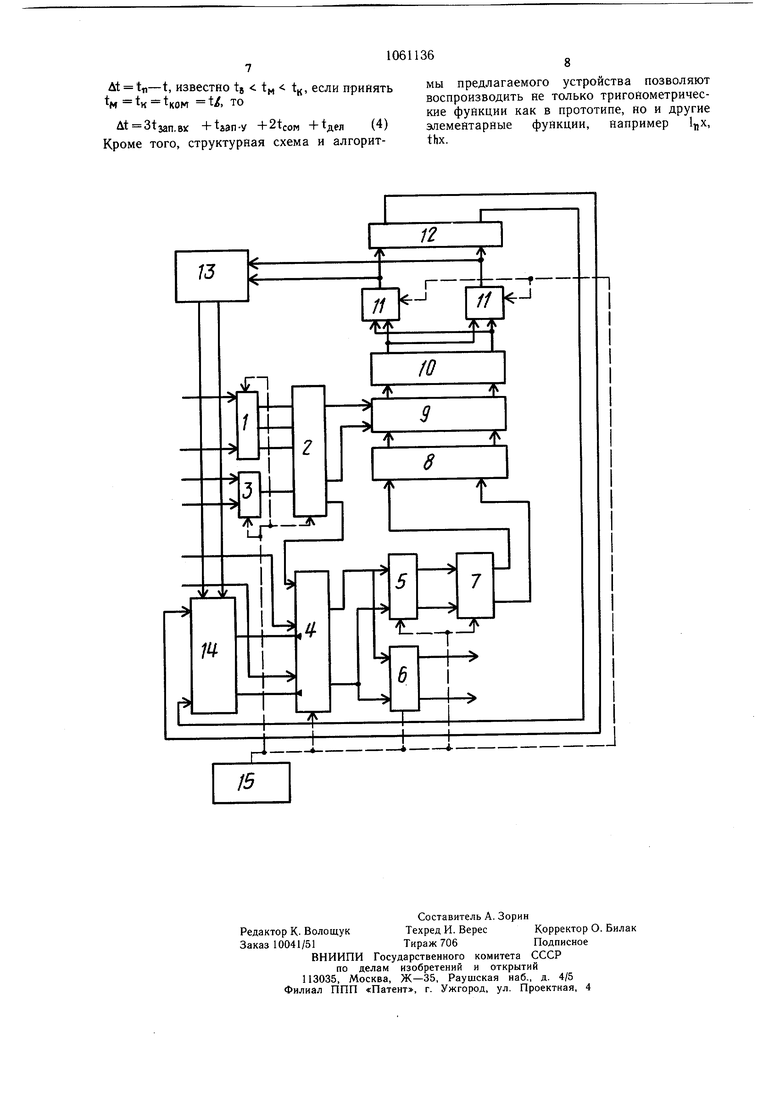

На чертеже представлена блок-схема устройства.

Устройство для вычисления элементарных функций содержит блок 1 памяти функций, дешифратор функций 2, регистр квагранта 3, регистр 4 аргумента, группы элементов И 5 и 6, дешифратор адреса 7, груп0 пу элементов ИЛИ 8, группу элементов И 9 группу элементов ИЛИ 10, группу элел;«нтов И 11, блок памяти значений 12, группу элементов ИЛИ 13, коммутатор 14 и блок синхронизации i5.

Особенность алгоритма устройства за5 ключается в том, что используя способ ст пенчатой аппроксимации функции, где величина ступени определяется допустимой величиной погрешности воспроизведения функций, определяется сложение по модулю 2 кода входного аргумента и констан0ты к нему, хранимой в блоке памяти значений 12, причем константа представляет собой значение, определенное суммой по модулю 2 кода входного аргумента и соответствующего кода значения функции.

5 В табл. 1 для одного значения аргумента X определены константы Д к различным функциям.

Кроме того, обработка входной кодовой

последовательности аргумента ведется по

группам в каждой группе по п/с разрядов,

где п - разрядность кода аргумента; с -

число групп.

В табл. 2 приведены примеры значений корректирующих констант по группам для функций sin X, tgx, thx, х, е 0,2-0,3.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функций | 1977 |

|

SU696472A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Устройство для вычисления синуса и косинуса угла табличным методом | 1986 |

|

SU1348830A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ, содержащее регистр аргумента, регистр квадранта, блок памяти функций, дешифратор функций, дешифратор адреса, блок синхронизации и блок памяти значений, причем информационные входы блока памяти функций и регистра квадранта соединены с входом задания вида функции устройства, вход задания аргумента которого соединен с информационным входом регистра аргумента, выход блока памяти функций соединен с первым информационным входом дешифратора функций, второй информационный вход которого соединен с выходом регистра квадранта, управляющие входы блока памяти функций, регистра квадранта, регистра аргумента и входы разрешения выдачи дешифратора функции и дешифратора адреса соединены с первым входом блока синхронизации, отличающееся тем, что, с целью повышения быстродействия. в него введены четыре группы элементов И, три группы элементов ИЛИ и коммутатор, причем выход регистра аргумента соединен с первыми входами элементов И первой и второй группы, вторые входы и выходы элементов И первой группы соединены соответственно с первым выходом блока синхронизации и информационным входом дешифратора адреса, выход которого соединен с входами элементов ИЛИ первой группы, выходы которых соединены с первыми входами элементов И третьей группы, вторые входы которых соединены с первым выходом дешифратора функций, выходы элементов И третьей группы соединены с входами элементов ИЛИ второй группы, выходы которых соединены с первыми входами элеменi тов И четвертой группы, вторые входы которых соединены с вторым выходом блока (Л синхронизации, выходы элементов И четвертой группы соединены с входом блока памяти значений и входами элементов ИЛИ третьей группы, выходы которых соединены с управляющим входом коммутатора, информационные входы и выходы которого соединены соответственно с выходами блока памяти значений и входами записи регистра 05 аргумента, вход знака которого соединен с вторым выходом дешифратора функций, третий выход блока синхронизации соединен с вторыми входами элементов И второй ОС группы. о

Приме н и е. Знак ®

два.

:начает сложение по модулю Примечание. Устройство работает следующим образом. Код аргумента с выхода регистра 4 через группу 5 элементов И поступает йа дешифратор адреса 7, дешифруется и через группу 8 элементов ИЛИ поступает на входы группы 9 элементов И, на управляющие входы которых приходит импульс с выходов дешифратора 2 функций, на выходы которого по импульсу с блока сийхронизации 15 подается код функции, с выхода регистра 3 появляется сигнал, соответствующий знаку в квадранте воспроизводимой функции, который записывает эту информацию в знаковую ячейку регистра 4. По приходу сигнала с дешифратора 2 на соответствующие входы группы 9 элементов И выходная информация о выборе соответствующих элементов И 11 проходит через группу 10 элементов ИЛИ. Управляющий импульс, поступающий с блока синхронизации 15, коммутирует выходные импульсы соответствующего на входы блока памяти значений 12 и через группу 13 элементов ИЛИ поступает на управляющие входы комТаблица2Группы разбиваются от запятой по 4 разряда; значения хранятся в блоке памяти 12 мутатора 14, при этом на его информационные входы приходят сигналы с выходов блока памяти значений 12, в котором хранятся константы для соответствующих аргумента и функции. Выходные сигналы коммутатора 14 поступают на входы записи регистра 4. В регистре установилось значение соответствующей функции для входного аргумента. По разрешающему импульсу с блока синхронизации, поступившему на вторые входы группы элементов И 6 на выходах устройства появляется код значения функции. Время воспроизведения функций tgx, ctgx, secx и др. равно: : эап.бх +61выб .(3) где -время прохождения информации через коммутатор; 1пт время переброса триггера из одного состояния в другое. Из сопоставления быстродействия прототипа (1) и быстродействия предлагаемого устройства (3) для воспроизведения функций tgx, ctgx,-cosecx видно, что быстродействие предлагаемого выше на величину 78

At tfl-t, известно te t t, если принять i предлагаемого устройства позволяют м к tuflf, i, товоспроизводить не только тригонометричесДт 3тзап.вх +taan-y +2teoM +1дел (4)элементарные функции, например Цх,

Кроме того, структурная схема и алгорит-thx.

1061136

кие функции как в прототипе, но и другие

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функций | 1977 |

|

SU696472A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения 1-/ -аминофенил/-3 -/ -аминофенил/-7н-пирмдо-/2,3-с/карбазола | 1974 |

|

SU492517A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-15—Публикация

1982-01-06—Подача