Изобретение относится к вычислительной технике и может быть использовано для управления обменом информацией в режиме прямого доступа к памяти между ЭВМ, имеющими единый ка- нал обмена информации, например ЭВМ Элект{)сника-60, и внешними устройствами пользователя.

Цель изобретения - сокращение аппаратурных затрат устройства

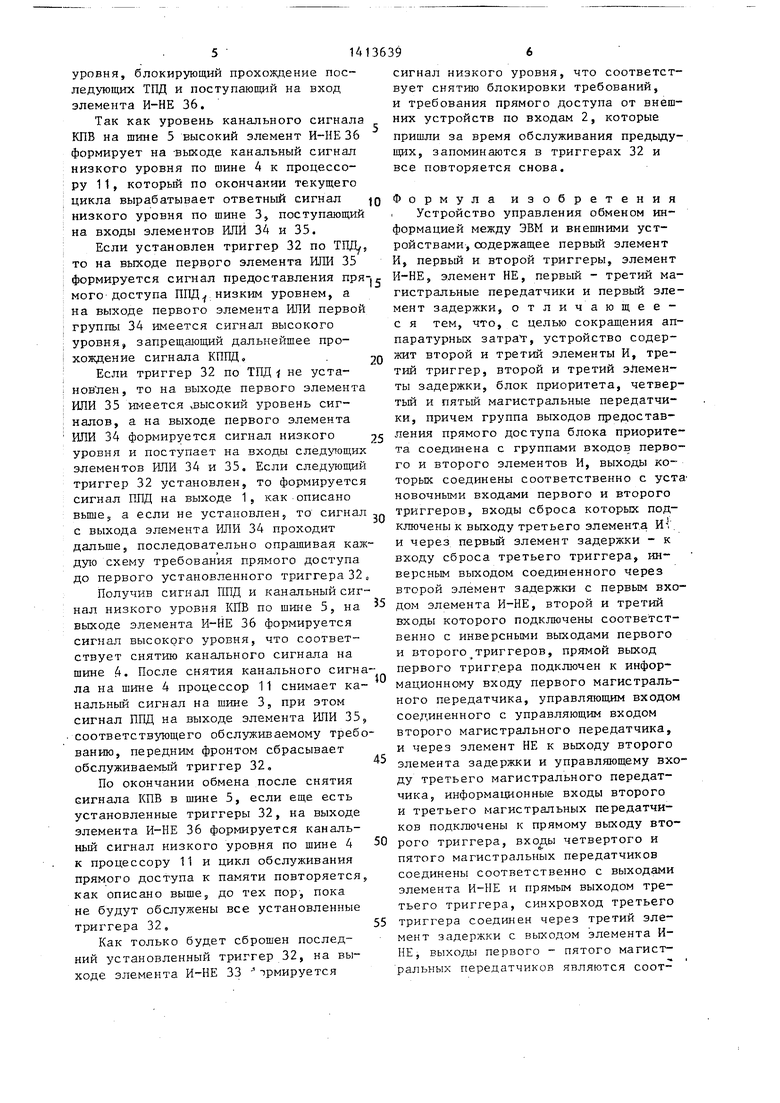

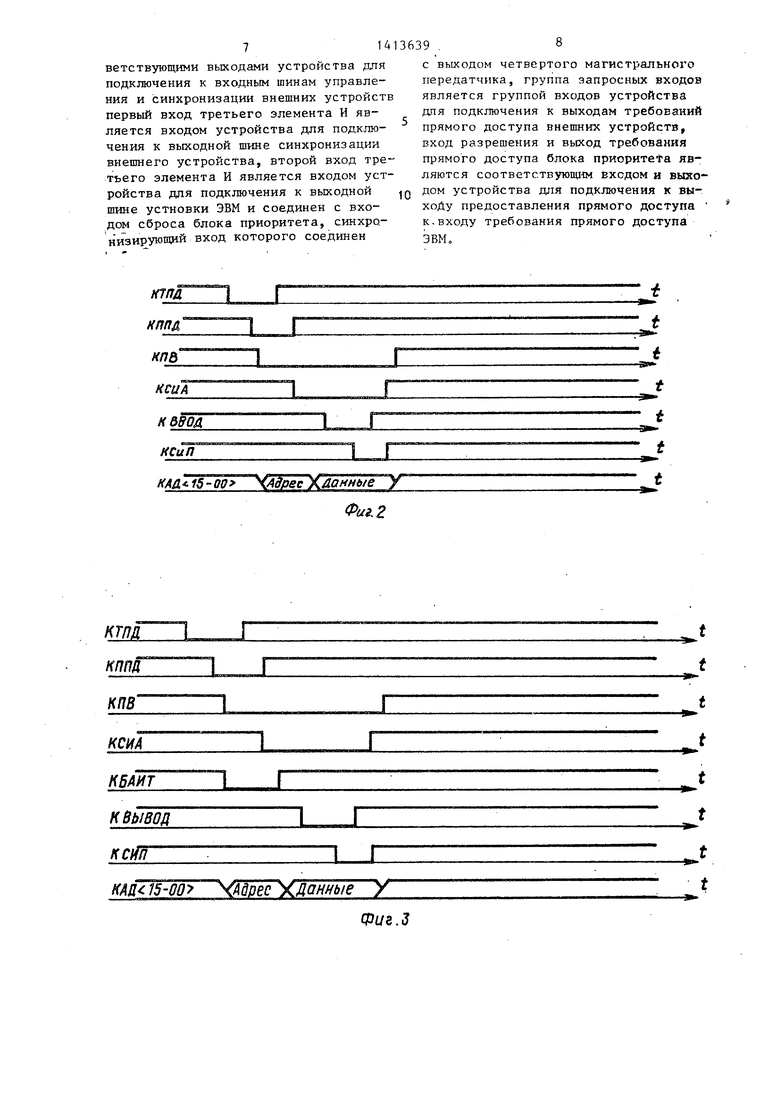

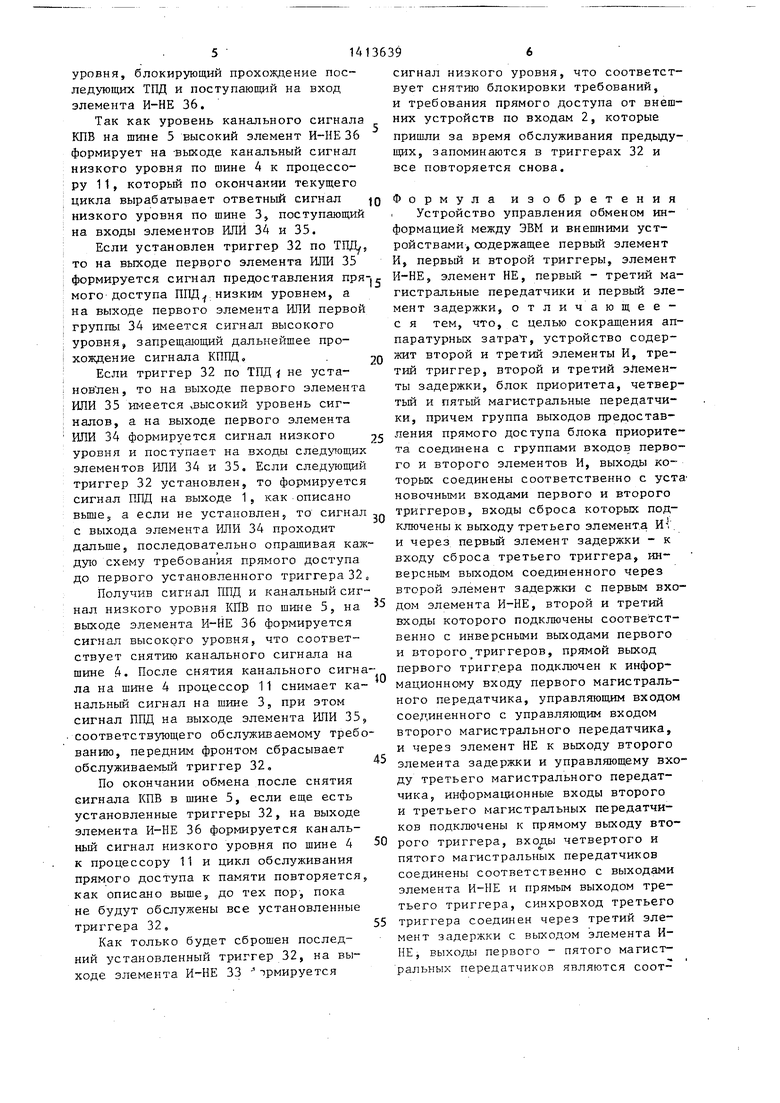

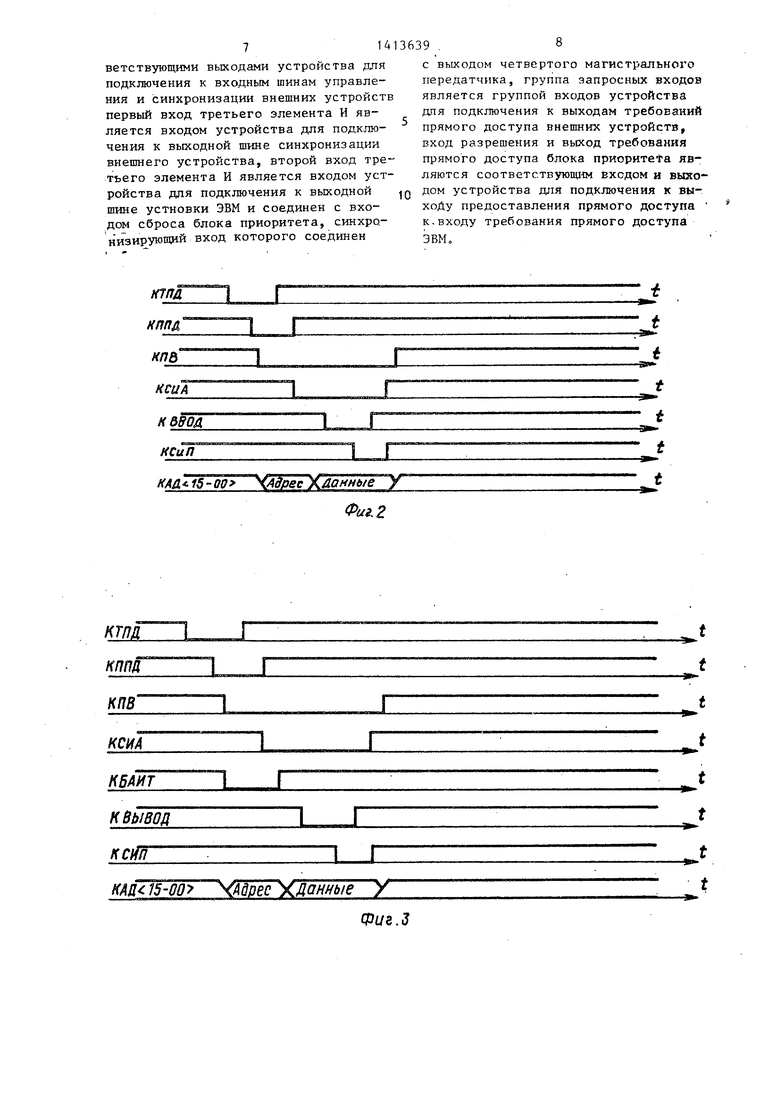

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма работы устройства в режиме Ввод на фиг, 3 - временные диаграммы работы устройства в режиме Вьшод ; на фиг. 4 и 5 - функциональная схема блока приоритета и временные диаграммы его работы,

Устройство содержит выходы 1 пре

доставления прямого доступа к памяти () , входы 2 требований прямого досту па к памяти (, шину 3 предоставления прямого доступ к памяти (КППД), щину 4 требования прямого доступа к памяти (КТПД), шин 5 подтверждения выбора (КПВ) ,, шину 6 установки (КУСТ)5 блок 7 приоритета, элементы И 8-10, процессор 11, триггеры 12 , элемент И-НЕ 14, эле- мен гы 15 и 16 задержкИ; элемент НЕ 17, триггер 18, элемент 19 задержки, первый 20 - третий.22, пятый 23 и четвертый 24 передатчики, шину 25 ввода данных (КВБОД), шину 26 вывода данных (КВЫВОД), шину. 27 вывода бай- та (КБАЙТ), шину 28 синхронизации активного устройства (КСИА), шину 29 синхронизации пассивного устройства (КСИП), группу 30 шин адрес-данные (КА/Д).

Блок 7 приоритета содержит группы элементов ШШ 31 и триггеров 32,элемент И-НЕ 33, группы элементов ИЛИ 34 и 35 и элемент И-НЕ 36,

Устройство работает следукицим об- разом.

Обмен данными происходит в режиме прямого доступа к памяти, при которо внешнее устройство запросившее прямо доступ к памяти и получившее предос- тавление прямого доступа к памяти, является активным устройством и бере управление кангшом на себя, т.е. должно формировать канальные сигналы: КПВ, КСИА, КВВОД или КВЫВОД, KBAflT. При этом порядок выполнения операций должен быть следующим: - устройство запрашива канал, вырабатывая сигнал:КТПД;

5

10

15

,20

25

35 40

45

о 55

-полле завершения текущего канала процессор вырабатьшает сигнал КППД, , запрещая выработку следующего процессорного цикла канала;

-устройство получает сигнал КППД, вырабатывает сигнал КПВ и снимает сигнал КТПД;

-процессор снимает сигнал КППД,ожидает завершения циклов Ввод или Вывод ;

-устройство получает канал и вьшол- няет требуемые циклы Ввод или Вывод .

Когда передача данных заканчивается, устройство снимает сигнал КПВ и возвращает управление каналом процессору.

Если каждое внешнее устройство формирует управляющие канальные сигналы, это приводит к увеличению аппаратурных затрат.

Устройство управления обменом информации между ЭВМ и внешними устройствами формирует канальные сигналы гфи обслуживании прямого доступа, а также определяет последовательность обслуживания запросов от внешних устройств.

По включении питания процессор 11 вырабатывает сигнал низкого уровня по.шине 6, который устанавливает в начальное состояние блок 7 и через элемент И 10 триггеры 12, 13 и 18, ,

При поступлении от внешнего устройства по входам 2 сигнала ТПД блок 7 формирует канальный сигнал низкого уровня по шине 4 к процессору 11, который по окончании текущего цикла вырабатыва:ет ответный сигнал низкого уровня по шине 3, Блок 7 формирует на выходах 1 сигнал низкого уровня ППД тому внешнему устройству, чье требование обслуживается, при этом сигнал поступает на вход элемента И 8, если происходит считывание из ОЗУ, т.е. режим Ввод, или на вход элемента И 9, если происходит запись данных в ОЗУ, т,е, режим Вывод., Распределение сигналов ППД между элементами И 8, 9 производится пользователем,

В режиме Ввод сигнал ППД, пройдя элемент И 8, взводит триггер 12, сигнал низкого уровня с инверсного выхода ,которого поступает на вход элемента И-НЕ 14, формирующего на выходе сигнал высокого уровня, поступающий на входы магистрального передатчика 24,При этом на выходе этого передат10

15

20

314

чика 24 формируется канальный сигнал низкого уровня, поступающий по шине 5 и в процессор 11.

Сигнал с выхода элемента И-НЕ 14 поступает также на вход элемента 16 задержки и через определенное время, необходимое для подачи в канал кода адреса ОЗУ по шинам 30, поступает на синхровход триггера 18, устанавливая его в единичное состояние. Сигнал с прямого выхода триггера 18 поступает на входы магистрального передатчика 23, формирующего на выходе канальный сигнал низкого уровня КСИА по шине 28, по которому запоминается адрес в ОЗУ.

Сигнал НИЗКОГО уровня с инверсного выхода триггера 18 поступает на вход элемента 19 задержки и через определенное время, необходимое для снятия адреса с канальных шин 30, проходит через элемент НЕ 17, поступает высоким уровнем на вход магистрального передатчика 20, на другом входе кото-25 рого также имеется сигнал высокого уровня с прямого выхода триггера 12,

На выходе этого передатчика формируется сигнал низкого уровня КВВОД, посылаемый по шине 25 в процессор 11, По этому сигналу в ОЗУ считываются данные и по канальным шинам 30 посылаются внешнему устройству, где запоминаются по канальному сигналу КСИП в щине 29, который вырабатьшает процессор 11.

Сигнал КСИП, пройдя через элемент И 10, сбрасывает триггер 12 и через определенное время, задаваемое элементом 15 задержки, триггер 18 при этом последовательно снимаются сигна

лы в шинах 25 и 28.

Сигнал высокого уровня с инверсно- го выхода триггера 18 через элемент 19 задержки поступает на вход элемента И-НЕ 14, на остальных входах одного элемента также имеется высокий уровень, следовательно, на выходе формируется сигнал низкого уровня, поступающий на входы магистрального передатчика 24, при этом снимается каналь ный сигнал в шине 5. На этом режим Ввод заканчивается и управление каналом передается процессору 11.

При режиме Вывод сигнал ППД,пройдя элемент И 9, взводит триггер 13, 55 сигнал высокого уровня с прямого выхода этого триггера поступает на вход магистрального передатчика 22, форми30

35

,-40

45

,-50

3639

10

15

20

25

,

руьй55о30

35

40

45

,-50

руя канальный сигнал КБАПТ, поступающий по шине 27 в процессор 11. Сигнал КБАЙТ необходимо формировать в адресной части режима Вьшод.

Канальные сигналы в шинах 5 и 28 формируются, как бьшо описано в ре- TiCHwe Ввод. Внешнее устройство по сигналу КПВ выставляет код адреса в канальные шины 30, который запоминается в ОЗУ по сигналу КСИА, а за- тем на канальные шины 30 внешнее ройство выставляет данные.

Сигнал низкого уровня с инверсного выхода триггера 18 через элемент 19 задержки поступает на вход магистрального передатчика 21, снимая канальный сигнал КБАЙТ, и через элемент НЕ 17 на входы магистрального передатчика 21 и 20. При этом на выходе магистрального передатчика 22 формируется канальный сигнал КВЫВОД по шине 26, по которому в ОЗУ записываются данные от внешнего устройства.

Когда данные будут записаны, процессор 11 выдает сигнал КСИП по шине 29, по которому снимаются канальные сигналы КВЫВОД, КСИА, КПВ, как быпо описано в режиме Ввод,

Обмен данными по инициативе внешнего устройства может выполняться при прямом доступе К памяти и в режиме прерывания.программы.

Обмен данными в режиме прерывания программы - это выполнение программы обслуживания по требованиям внепшего устройства. Процессор при этом приостанавливает вполнение текущей программы, чтобы обслужить запрашивающее устройство. По завершении выполнения программы обслуживания продест сор возобновляет выполнение прерванной программы с того места, где она была прервана.

Блок 7 приоритета работает следующим образом.

Сигнал низкого уровня по шине 6 сбрасывает триггеры 32, при этом на выходе элемента И-НЕ 33 появляется сигнал низкого уровня, разрешающий прохозкдение по входам 2 ТПД,

При поступлении ТПД по входам 2 на выходах элементов ИЛИ 31 формируются сигналы низкого уровня, которые по S-входу устанавливают соответствующие триггеры 32. Сигналы с нулевых выходов триггеров 32 поступают на входы элемента И-НЕ 33, на выходе которого формируется сигнал высокого

5 14

уровня, блокирующий прохождение последующих ТПД и поступающий на вход элемента И-НЕ 36.

Так как уровень канального сигнала КПВ на шине 5 высокий элемент И-НЕ 36 формирует на -выходе канальный сигнал низкого уровня по шине А к процессору 1 1 , который по окончании текущего цикла вырабатывает ответный сигнал низкого уровня по шине 3, поступающий на входы элементов ИЛИ 34 и 35.

Если установлен триггер 32 по ТГЦЬ, то на выходе первого элемента ИЛИ 35

сигнал низкого уровня, что соответствует снятию блокировки требований, и требования прямого доступа от внешних устройств по входам 2, которые пришли за время обслуживания предыдущих, запоминаются в триггерах 32 и все повторяется снова.

Формула изобретения Устройство управления обменом информацией между ЭВМ и внешними устройствами, содержащее первый элемент И, первый и второй триггеры, элемент

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения двух ЭВМ с общим внешним устройством | 1986 |

|

SU1365089A1 |

| Электронная вычислительная машина с прямым доступом в память | 1987 |

|

SU1529240A1 |

| Устройство управления доступом к магистрали ЭВМ | 1984 |

|

SU1242952A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления обменом информацией в режиме прямого доступа к памяти между ЭВМ и внешними устройствами. Целью изобретения является сокращение аппаратурных затрат. УстройстКППА во содержит выходы 1 предоставлений прямого доступа к памяти, входы 2 требований прямого доступа к памяти, шину 3 предоставления прямого доступа к памяти, шину 4 требования прямого доступа к памяти, шину 5 подтверждения выбора, шину 6 установки, блок 7 приоритета, три элемента И 8, 9, 10, процессор 11, два триггера 12, 13, элемент И-НЕ 14, две линии задержки 15, 16, элемент НЕ 17, триггер 18, линию задержки 19, пять магистральных передатчиков 20-24, шину 25 ввода , данных, шину 26 вывода данных, шину 27 вывода байта, шину 28 синхронизации активного устройства, шину 29 синхронизации пассивного устройства, группу шин 30 адрес-данные. Устройство обеспечивает управление вводом и выводом данных между группой внешних устройств и ЭВМ в режиме прямого доступа к памяти. 5 ил. S (Л СЬгГ А ff.- fU fJil:1 l Cf fffo

формируется сигнал предоставления пря-,с И-НЕ, элемент НЕ, первый - третий мамого доступа ПЩ низким уровнем, а на выходе первого элемента ИЛИ первой группы 34 имеется сигнал высокого уровня, запрещающий дальнейшее прохождение сигнала КПЦЦ, . -;Q

Если триггер 32 по ТЩ не уста- нов лен, то на выходе первого элемента ИЛИ 35 имеется ,высокий уровень сигналов, а на выходе первого элемента ИЛИ 34 формируется сигнал низкого 25 уровня и поступает на входы следующих элементов ИЛИ 34 и 35. Если сп&ц, триггер 32 установлен, то формируется сигнал ППД на выходе 1, как описано Bbmiej а если не установлен, то сигнал с выхода элемента ИЛИ 34 проходит дальше, последовательно опрашивая каждую схему требования прямого доступа до первого установленного триггера 32 ,

Получив сигнал ППД и канальный сигнал низкого уровня КПВ по шине 5, на выходе элемента И-НЕ 36 формируется сигнал высокого уровня, что соответствует снятию канального сигнала на

30

гистральные передатчики и первый элемент задержки, отличающее- с я тем, что, с целью сокращения аппаратурных затраТ, устройство содержит второй и третий элементы И, третий триггер, второй и третий элементы задержки, блок приоритета, четвер- тьй и пятый магистральные передатчики, причем группа выходов предоставления прямого доступа блока приоритета соединена с группами входов первого и второго элементов И, выходы которых соединены соответственно с уста новочными входами первого и второго триггеров, входы сброса которых подключены к выходу третьего элемента И- ,, и через первьм элемент задержки - к входу сброса третьего триггера, инверсным выходом соединенного через второй элемент задержки с первым входом элемента И-НЕ, второй и третий входы которого подключены соответственно с инверсными выходами первого и второго триггеров, прямой выход первого триггера подключен к информационному входу первого магистрального передатчика, управляющим входом соединенного с управляющим входом второго магистрального передатчика, и через элемент НЕ к выходу второго элемента задержки и управляющему входу третьего магистрального передатчика, информационные входы второго и третьего магистральных передатчиков подключены к прямому выходу вто рого триггера, входы четвертого и пятого магистральных передатчиков соединены соответственно с выходами элемента И-НЕ и прямым выходом третьего триггера, синхровход третьего триггера соединен через третий элемент задержки с выходом элемента И- НЕ, выхода первого - пятого магистральных передатчиков являются соотшине 4. После снятия канального сигнала на шине 4 процессор 11 снимает канальный сигнал на шине 3, при этом сигнал ППД на выходе элемента ИЛИ 35, соответствующего обслуживаемому требованию, передним фронтом сбрасывает обслуживаемый триггер 32.

По окончании обмена после снятия сигнала КПВ в шине 5, если еще есть установленные триггеры 32, на выходе элемента И-НЕ 36 формируется канальный сигнал низкого уровня по шине 4 к процессору 11 и цикл обслуживания прямого доступа к памяти повторяется, как описано выше, до тех пор-, пока не будут обслужены все установленные триггера 32,

Как только будет сброшен последний установленный триггер 32, на выходе элемента И-НЕ 33 - -армируется

Q

5

0

5

0

5

гистральные передатчики и первый элемент задержки, отличающее- с я тем, что, с целью сокращения аппаратурных затраТ, устройство содержит второй и третий элементы И, третий триггер, второй и третий элементы задержки, блок приоритета, четвер- тьй и пятый магистральные передатчики, причем группа выходов предоставления прямого доступа блока приоритета соединена с группами входов первого и второго элементов И, выходы которых соединены соответственно с уста новочными входами первого и второго триггеров, входы сброса которых подключены к выходу третьего элемента И- ,, и через первьм элемент задержки - к входу сброса третьего триггера, инверсным выходом соединенного через второй элемент задержки с первым входом элемента И-НЕ, второй и третий входы которого подключены соответственно с инверсными выходами первого и второго триггеров, прямой выход первого триггера подключен к информационному входу первого магистрального передатчика, управляющим входом соединенного с управляющим входом второго магистрального передатчика, и через элемент НЕ к выходу второго элемента задержки и управляющему входу третьего магистрального передатчика, информационные входы второго и третьего магистральных передатчиков подключены к прямому выходу вто рого триггера, входы четвертого и пятого магистральных передатчиков соединены соответственно с выходами элемента И-НЕ и прямым выходом третьего триггера, синхровход третьего триггера соединен через третий элемент задержки с выходом элемента И- НЕ, выхода первого - пятого магистральных передатчиков являются соответствующими выходами устройства для подключения к входным шинам управления и синхронизации внешних устройств первый вход третьего элемента И является входом устройства для подключения к выходной шине синхронизации внешнего устройства, второй вход третьего элемента И является входом устройства для подключения к выходной шине устновки ЭВМ и соединен с входом сброса блока приоритета, синхронизирующий вход которого соединен

Фи.2

с выходом четвертого магистрального передатчика, группа запросных входов является группой входов устройства для подключения к выходам требований прямого доступа внешних устройств, вход разрешения и вькод требования прямого доступа блока пpиopитeta являются соответствующим входом и выходом устройства для подключения к вы- хоДу предоставления прямого доступа к.входу требования прямого доступа ЭВМ,

Фиг.З

2 ,

5

кпв

-3&-

Фив. 5

| Авторское свидетельство СССР № 1154674, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Зеркальный стереовизир | 1922 |

|

SU382A1 |

| ТО | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

Авторы

Даты

1988-07-30—Публикация

1986-08-08—Подача