Изобретение относится к вычислительной технике и может быть использовано при обмене информацией в режиме прямого доступа к памяти ЭВМ серии Электроника и внешними устройствами.

Цель изобретения - упрощение устройства.

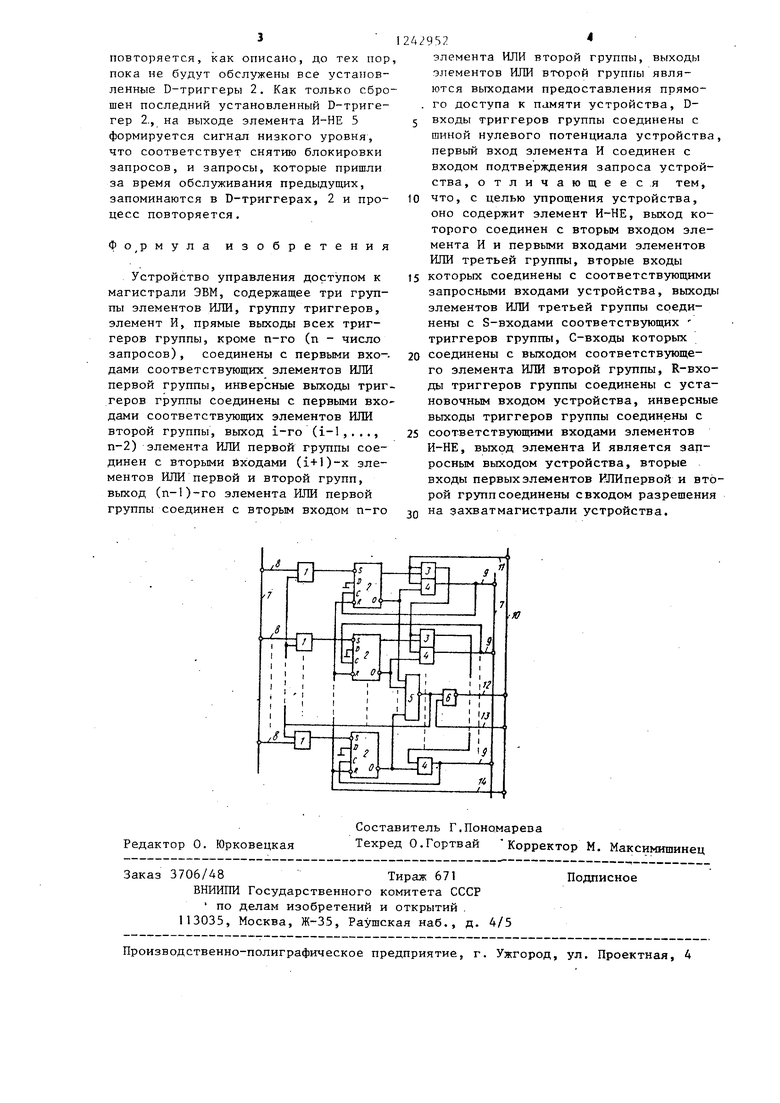

На чертеже представлена блок-схем предлагаемого устройства.

Устройство содержит п элементов ИЖ 1 третьей группы, N триггеров 2 группы, (п-1) элементов ИЛИ 3 первой группы, N элементов ИЛИ 4 второй группы, элемент И-НЕ 5, элемент И 6, шину 7 запросов прямого доступа к памяти, запросные входы 8, выходы 9 представления прямого доступа к памяти, магистральную шину. 10 управления вход 11 разрешения на захват магистрали, запросный выход 12, вход 13 подтверждения запроса и установочный вход 14.

Устройство работает следующим образом.

В момент включения питания D-триг г-еры 2 сбрасываются в нулевое состояние магистральным сигналом установки О с входа 14, при этом выход элемента И-НЕ 5 и Блокировка запросов также устанавливается в нулевое состояние и разрешает прохождение входных сигналов запросов прямого доступ по входу 8. При поступлении запросов прямого доступа по входу 8 от внешни устройств на входы элементов ИЛИ 1, на выходах этих элементов формируются сигналы нулевого уровня, которые по S-входу устанавливают соответствующие D-триггеры. Сигналы с нулевых выходов D-триггеров 2 поступают на входы элемента И-НЕ 5, на выходе которого формируется высокий уровень сигнала, блокирующий прохождение последующих запросов прямого доступа и поступаюш 1й на вход элемента И 6. Так как уровень магистрального сигнала подтверждения запроса на входе 13 высокий, на выходе элемента И 6 появляется сигнал запроса магистрали на выходе 12 низкого уровня. Если магистраль в этот момент занята выполнением текущего цикла, то после завершения этого цикла центральный процессор вырабатывает сигнал раз- решения на захват магистрали на входе II низким уровнем, который поступает на входы первых элементов ИЛИ 3

и.4. Если D-триггер 2 по первому запросу установлен, на выходе первого элемента ИЛИ 4 формируется сигнал предоставления прямого доступа к памяти на выходе 9 низким уровнем, а на выходе первого элемента ИЛИ 3 остается сигнал высокого уровня, и дальнейшее прохождение сигнала разрешения на захват магистрали на входе

11 прекращается. Если D-триггер 2 по первому запросу не установлен, на выходе первого элемента ИЛИ 4 остается высокий уровень сигнала, а на выходе первого элемента ИЛИ 3 формируется сигнал нулевого уровня и поступает на входы следующих элементов ИЛИ 3 и 4. Если следуюший D-триггер 2 установлен, то формируется сигнал предоставления прямого доступа на

выходе 9, как описано, а если не установлен, то сигнал с выхода элемента ИЛИ 3 проходит дальше,последовательно опрашивая каждую схему запроса до первого установленного Dтриггера 2. Внешнее устройство, получив сигнал Предоставление прямого доступа к памяти на выходе 9, формирует сигнал Подтверждение захвата на выходе 13 низкого уровня, который, поступая на вход элемента И 6, на. выходе формирует сигнал высокого уровня, что соответствует снятию магистрального сигнала запроса магистрали на выходе 12. После снятия запроса магистрали на выходе 12 центральный процессор снимает сигнал разрешения на захват магистрали на входе i1. При этом сигнал Предоставление прямого доступа к памяти

на выходе 9 КПИ 4, соответствующего обслуживаемому запросу, становится высокого уровня и передним фронтом по С-входу сбрасывает обслуживаемый D-триггер 2.

,, „

Внешнее устройство, получившее

сигнал Предоставление прямого доступа на выходе 9,берет управление магистралью на себя и проводит обмен информацией с-ОЗУ. По окончании обмена внешнее устройство снимает сигнал Подтверждение запроса на входе 13,, т.е. он становится высокого уровня, при этом, если есть еще установленные D-триггеры 2, на выходе элемента И 6 формируется сигнал низкого уровня, что соответствует установке сигнала запроса магистрали на выходе 12. Цикл обслуживания запроса

повторяется, как описано, до тех пор пока не будут обслужены все установленные D-триггеры 2. Как только сброшен последний установленный D-триге- гер 2., на выходе элемента И-НЕ 5 формируется сигнал низкого уровня, что соответствует снятию блокировки запросов, и запросы, которые пришли за время обслуживания предыдупщх, запоминаются в D-триггерах, 2 и процесс повторяется,

Ф мула изобретения

Устройство управления доступом к магистрали ЭВМ, содержащее три группы элементов ИЛИ, группу триггеров, элемент И, прямые выходы всех триггеров группы, кроме п-го (п - число запросов), соединены с первыми входами соответствующих элементов ИЛИ первой группы, инверсные выходы триггеров группы соединены с первыми вхо дами соответствующих элементов ИЛИ второй группы, выход i-ro (i-1,..., n-2) элемента ИЛИ первой группы соединен с вторыми йходами (i+l)-x элементов ИЛИ первой и второй групп, выход (n-l)-ro элемента ИЛИ первой группы соединен с вторым входом п-го

242952

элемента ИЛИ второй группы, выходы элементов ИЛИ второй группы являются выходами предоставления прямого доступа к памяти устройства, D5 входы триггеров группы соединены с шиной нулевого потенциала устройства, первый вход элемента И соединен с входом подтверждения запроса устройства, отличающееся тем,

10 что, с целью упрощения устройства, оно содержит элемент И-НЕ, выход которого соединен с вторым входом элемента И и первыми входами элементов ИЛИ третьей группы, вторые входы

15 которых соединены с соответствующими запросными входами устройства, выходы элементов ИЛИ третьей группы соединены с S-входами соответствующих триггеров группы, С-входы которых

20 соединены с выходом соответствующего элемента ИЛИ второй группы, R-BXO- ды триггеров группы соединены с установочным входом устройства, инверсные выходы триггеров группы соединены с

25 соответствующими входами элементов И-НЕ, выход элемента И является запросным выходом устройства, вторые входы первыхэлементов ИЛИпервой и второй групп соединены ОБХОДОМ разрещения

3Q на захватмагистрали устройства.

Редактор 0. Юрковецкая

Заказ 3706/48Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель Г.Пономарева

Техред О.Гортвай Корректор М. Максимишинец

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления обменом информацией между ЭВМ и внешним устройством | 1986 |

|

SU1413639A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство приоритета | 1989 |

|

SU1705826A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2023293C1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| Многоканальное устройство приоритета | 1990 |

|

SU1772803A1 |

Изобретение относится к вычислительной технике и может быть использовано при обмене информацией в режиме прямого доступа памяти ЭВМ серии Электроника и внешними устройствами. Цель изобретения -.упрощение устройства. Цель изобретения достигается за счет введения в уст- . ройство элемента И-НЕ с соответству- Ю1ЦИМИ функциональньми связяь4и между ним и известными блоками устройства. 1 ил. (Л с w 1C СП ГО

| Устройство для управления доступом к магистрали | 1980 |

|

SU935961A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритета | 1984 |

|

SU1196869A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-10-17—Подача