Изобретение относится к вычислительной технике и может быть использовано в системах для обработки информации.

Цель изобретения - повьш1ение быстродействия за счет обеспечения возможности передачи за один цикл прямого доступа в память нескольких слов информации.

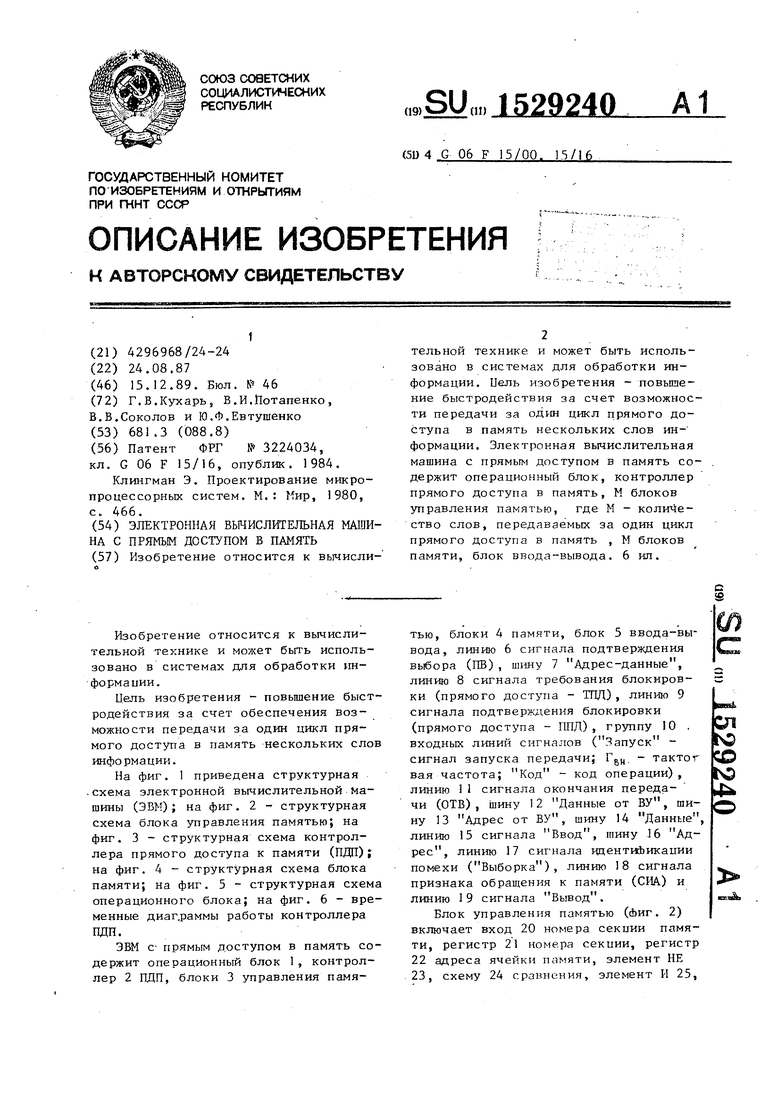

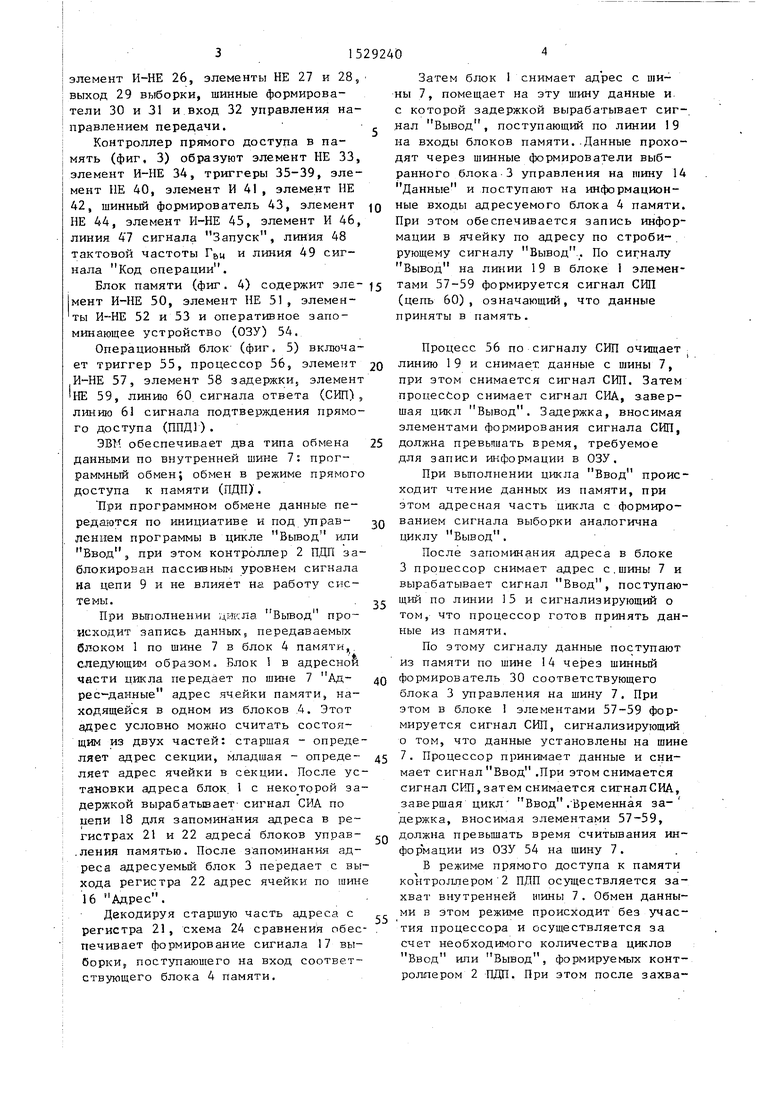

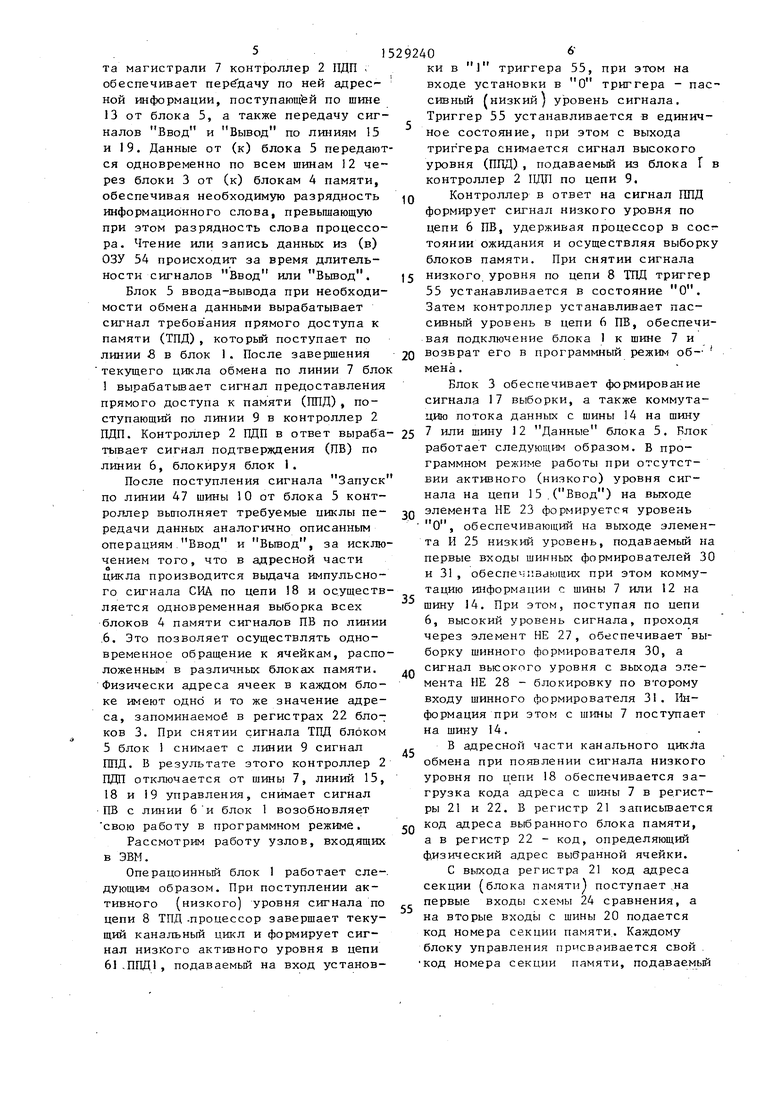

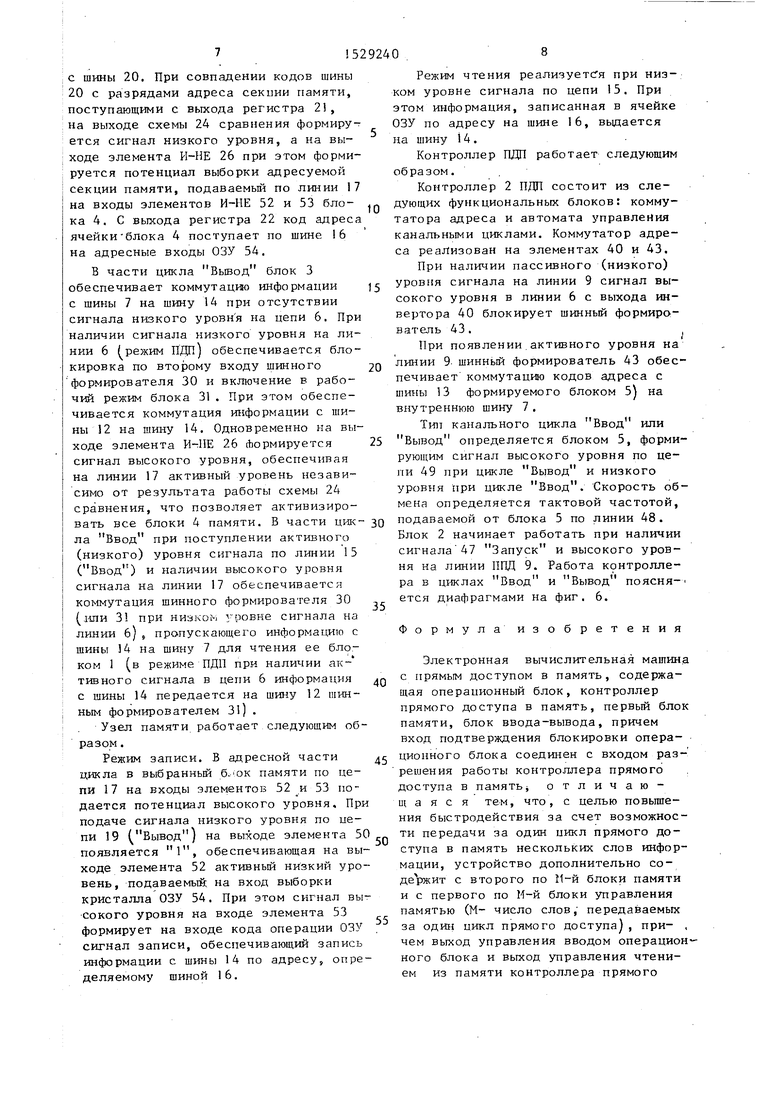

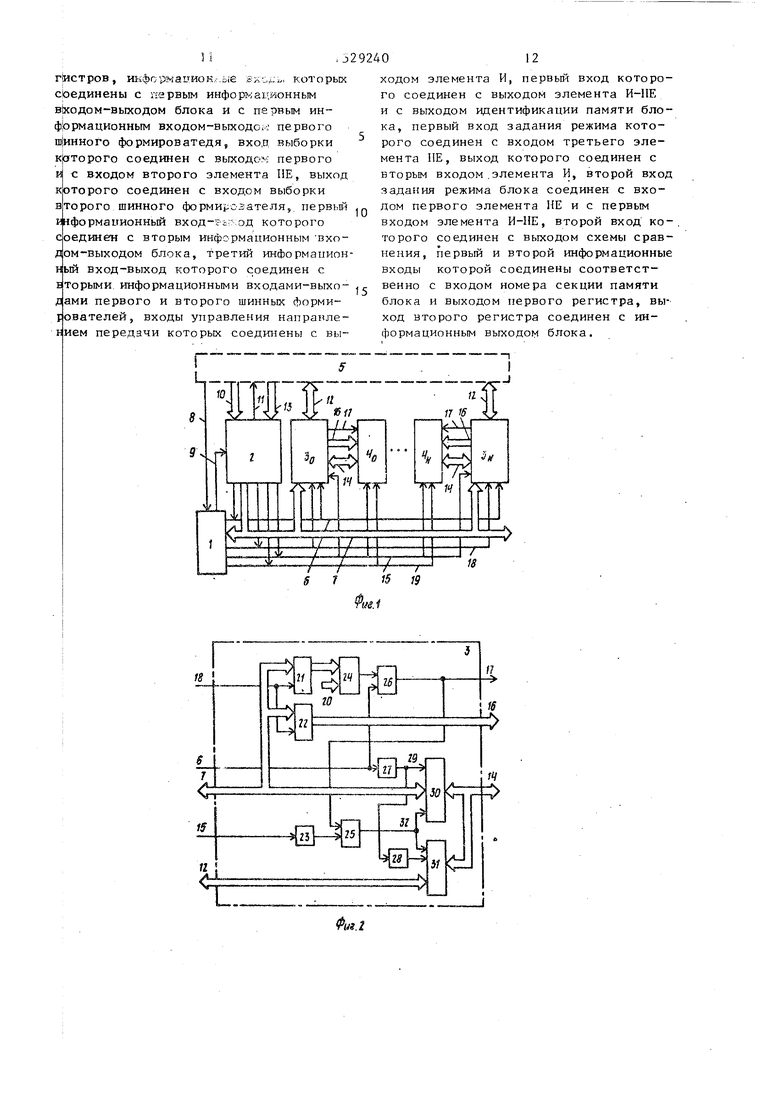

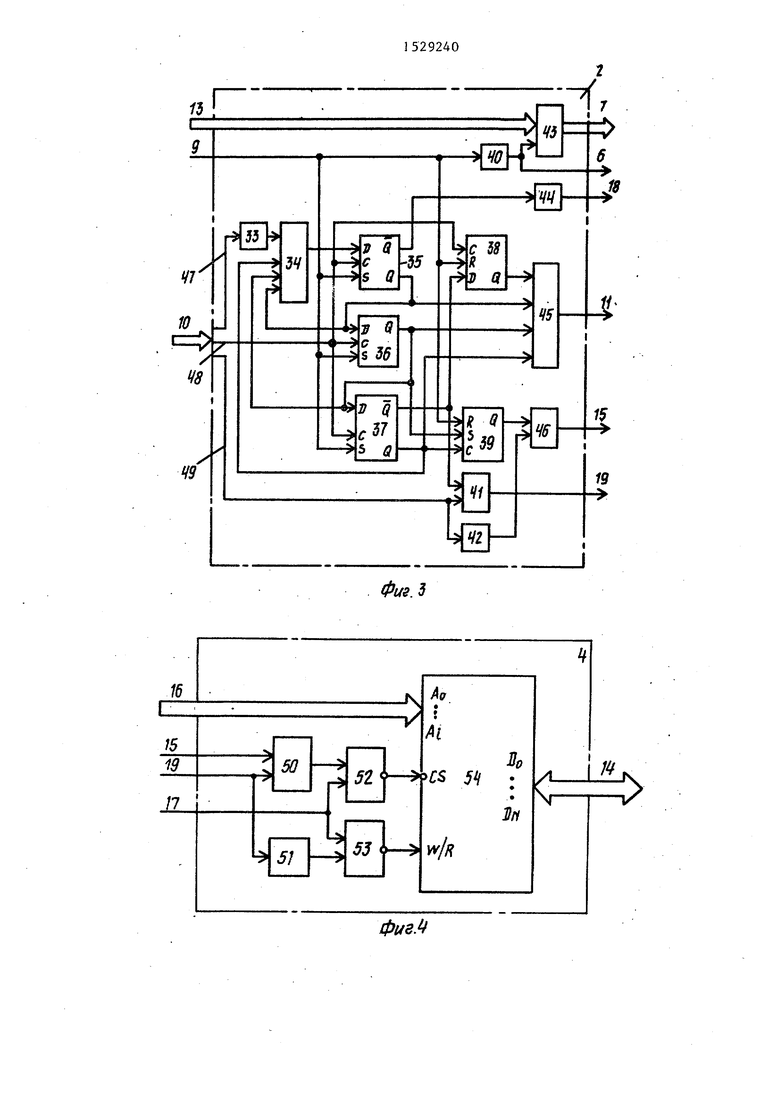

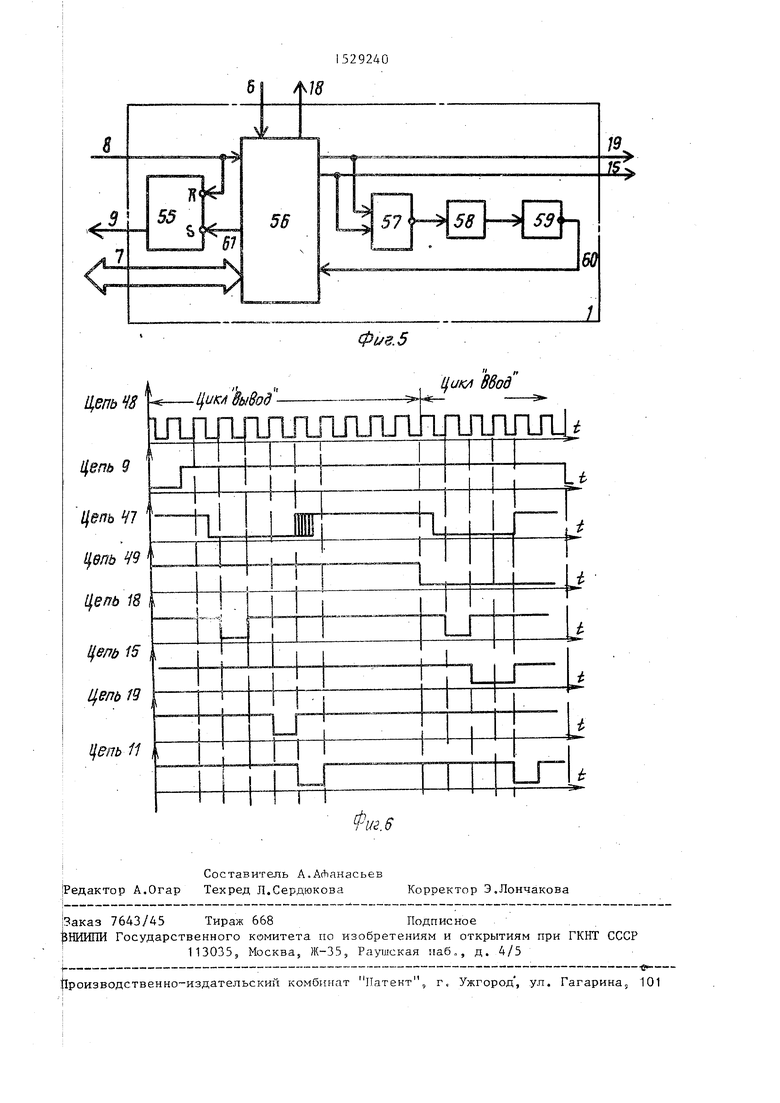

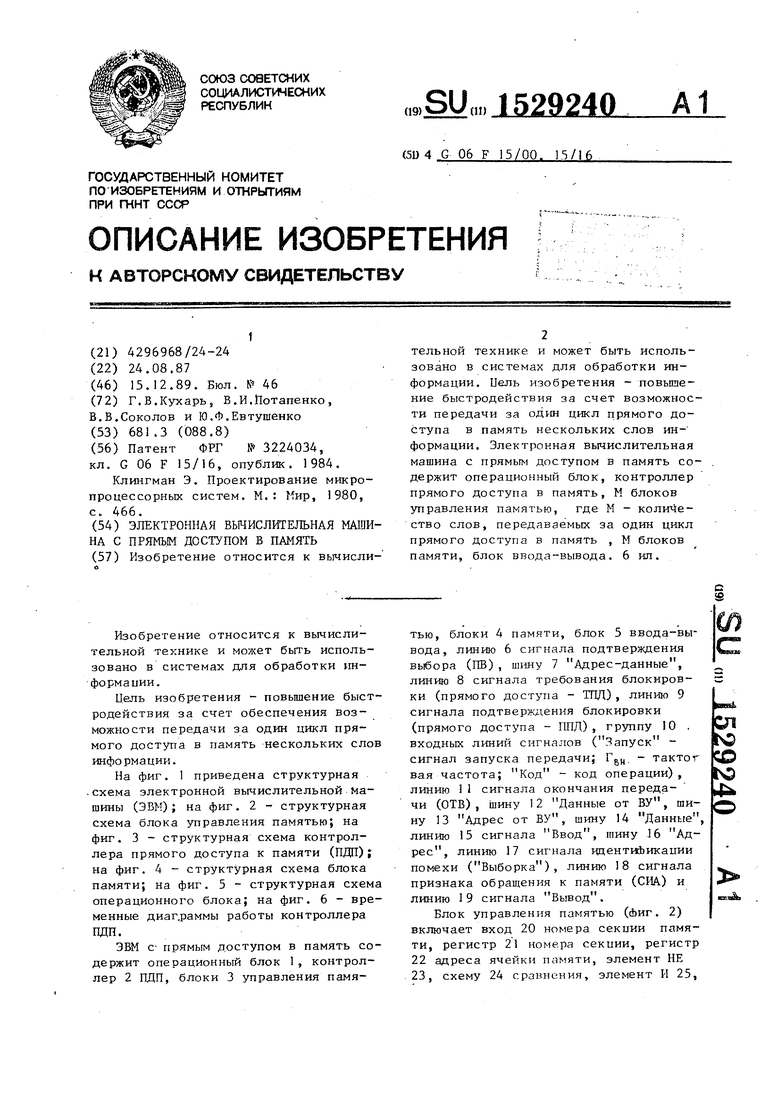

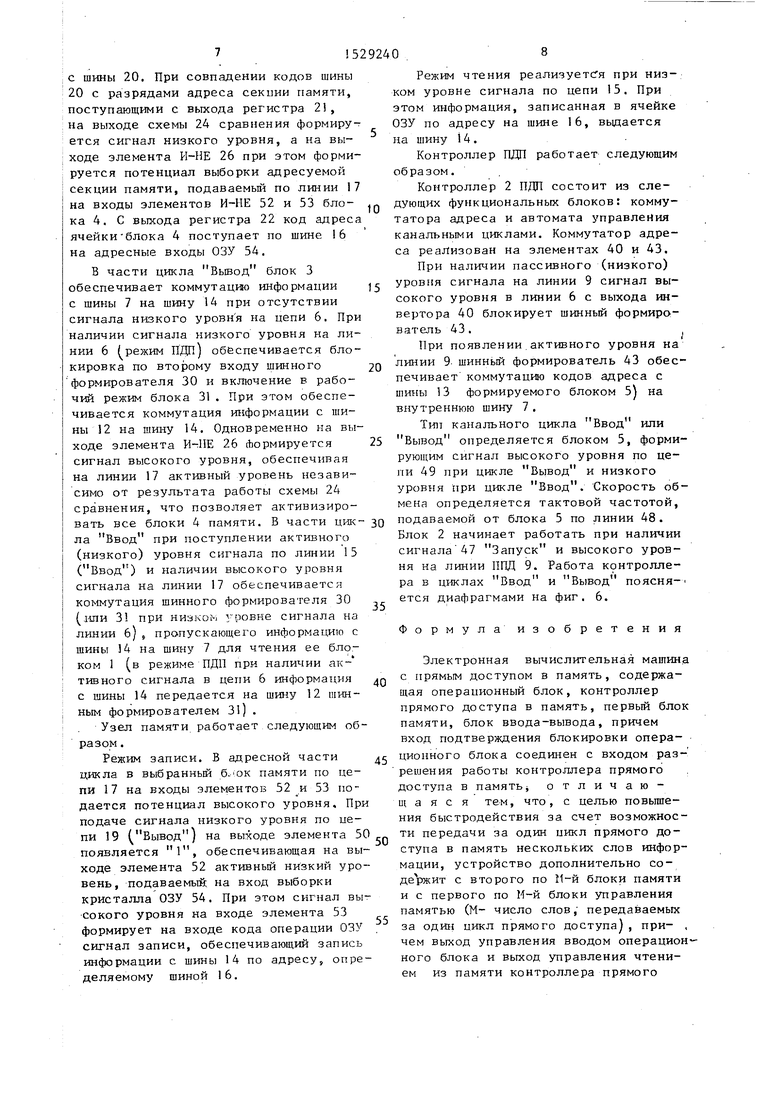

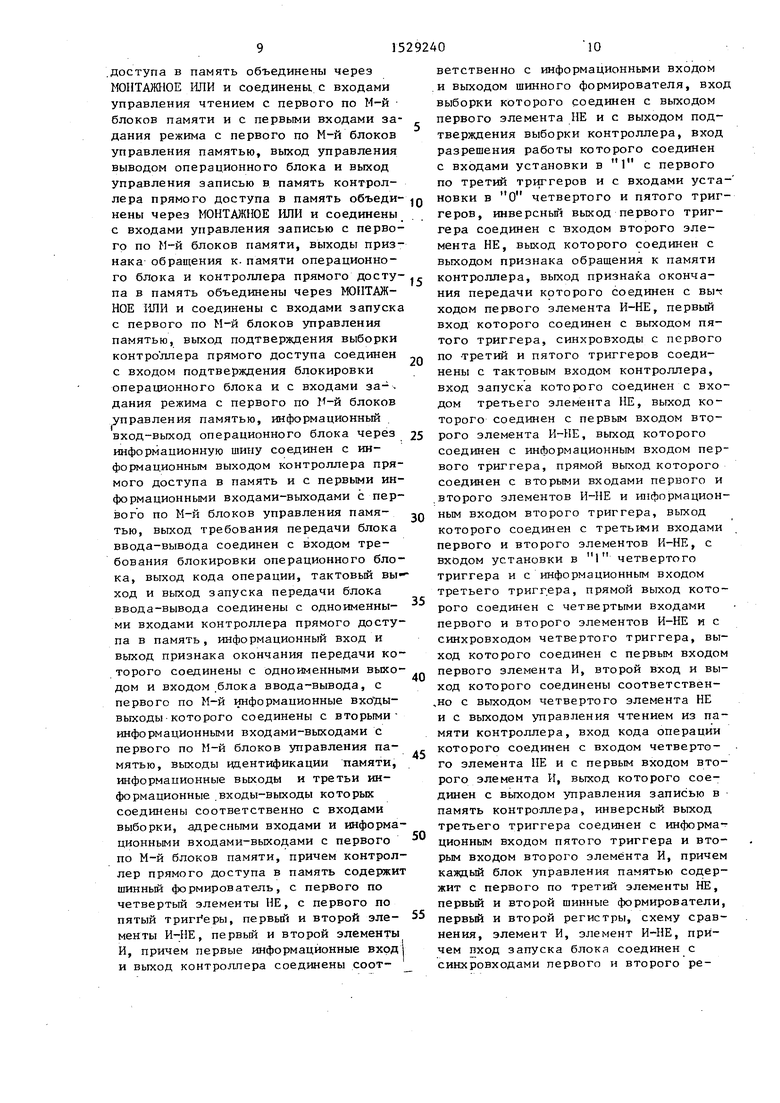

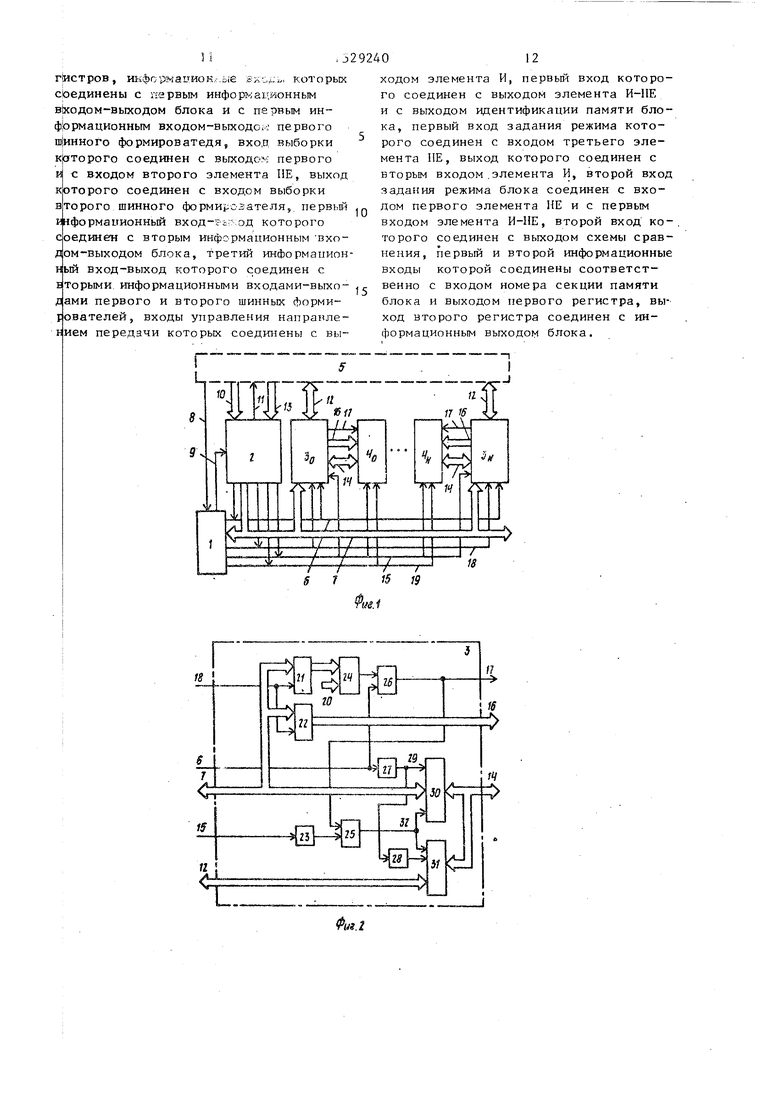

На фиг. 1 приведена структурная -Схема электронной вычислительной машины (ЭВМ); на фиг. 2 - структурная схема блока управления памятью; на фиг. 3 - структурная схема контроллера прямого доступа к памяти (ПДП); на фиг. 4 - структурная схема блока памяти; на фиг. 5 - структурная схема операционного блока; на фиг. 6 - временные диаг.раммы работы контроллера ПДП.

ЭВМ с- прямым доступом в память содержит операционный блок 1, контроллер 2 ПДП, блоки 3 управления памятью, блоки 4 памяти, блок 5 ввода-вывода, линию 6 сигнала подтверждения выбора (ПВ), шину 7 Адрес-данные, линию 8 сигнала требования блокировки (прямого доступа - ТПД), линию 9 сигнала подтверждения блокировки (прямого доступа - ППД), группу 10 . входных линий сигналов (Запуск - сигнал запуска передачи; . - тактог вая частота; Код - код операции), линию 11 сигнала окончания передачи (ОТВ), шину 12 Данные от ВУ, шину 13 Адрес от ВУ, шину 14 Данные, линию 5 сигнала Ввод, шину 16 Адрес, линию 17 сигнала идентификации помехи (Выборка), линию 18 сигнала признака обращения к памяти (СИА) и линию 19 сигнала Вывод.

Блок управления памятью (Фиг. 2) включает вход 20 номера секции памяти, регистр 21 номера секции, регистр 22 адреса ячейки памяти, элемент НЕ 23, схему 24 сравнения, элемент И 25,

СП

ю

;О

Ю

элемент И-НЕ 26, элементы НЕ 27 и 28, выход 29 выборки, шинные формирователи 30 и 31 и вход 32 управления направлением передачи.

Контроллер прямого доступа в память (фиг, 3) образуют элемент НЕ 33, элемент И-НЕ 34, триггеры 35-39, элемент НЕ 40, элемент И 41, элемент НЕ 42, шинный формирователь 43, элемент НЕ 44, элемент И-НЕ 45, элемент И 46, линия 47 сигнала Запуск, линия 48 тактовой частоты Ген и линия 49 сигнала Код операции.

Блок памяти (фиг. 4) содержит эле- мент И-НЕ 50, элемент НЕ 51, элементы И-НЕ 52 и 53 и оперативное запоминающее устройство (ОЗУ) 54.

Операционный блок (фиг. 5) включает триггер 55, процессор 56, элемент И-НЕ 57, элемент 58 задержки, элемент НЕ 59, линию 60 сигнала ответа (СИП), линию 61 сигнала подтверждения прямого доступа (ППД1).

ЭВМ обеспечивлет два типа обмена данными по внутренней шине 7: программный обмен; обмен в режиме прямого доступа к памяти (ПДП).

При программном обмене данные пе- редалотся по инициативе и под управ- лением программы в цикле Вывод или Ввод, при этом контроллер 2 ПДП заблокирован пассивным уровнем сигнала на цепи 9 и не влияет на работу системы..

При выполнении щ-жла Вьгоод происходит запись данных 5 передаваемых бЛ-оком 1 по шине 7 в блок 4 памяти,, следующим образом. Блок 1 в адресной части цикла передает по шине 7 Ад- рес-данные адрес ячейки памяти, находящейся в одном из блоков .4. Этот адрес условно можно считать состоящим из двух частей: старшая - определяет адрес секции, младшая - опреде- ляет адрес ячейки в секции. После установки адреса блок 1 с некоторой задержкой вырабатьшает- сигнал СИА по цепи 18 для запоминания адреса в регистрах 21 и 22 адреса блоков управ- .ления памятью. После запоминания адреса адресуемьш блок 3 передает с выхода регистра 22 адрес ячейки по шине 16 Адрес.

Декодируя старшую часть адреса с

регистра 21, схема 24 сравнения обеспечивает формирование сигнала 17 вы боркИу поступающего на вход соответ ствующего блока 4 памяти.

5

0 5 Q

5

Затем блок 1 снимает адрес с шины 7, помещает на эту шину данные и с которой задержкой вырабатывает сигнал Вывод, поступающий по линии 19 на входы блоков памяти..Данные проходят через шинные формирователи выбранного блока 3 управления на шину 14 Данные и поступают на информационные входы адресуемого блока 4 памяти. При этом обеспечивается запись информации в ячейку по адресу по строби-. рующему сигналу Вывод.. По сигналу Вывод на линии 19 в блоке 1 элементами 57-59 формируется сигнал СИП (цепь 60), означающий, что данные приняты в память.

Процесс 56 по сигналу СИП очищает линию 19 и снимает данные с шины 7, при этом снимается сигнал СИП. Затем процессор снимает сигнал СИА, аавер- шая цикл Вывод. Задержка, вносимая элементами формирования сигнала СИП, должна превьпиать время, требуемое для записи информации в ОЗУ.

При выполнении цикла Ввод происходит чтение данных из памяти, при этом адресная часть цикла с формированием сигнала выборки аналогична циклу Вывод.

После запоминания адреса в блоке 3 процессор снимает адрес с,шины 7 и вырабатывает сигнал Ввод, поступающий по линии 15 и сигнализирующий о том, что процессор готов принять данные из памяти.

По этому сигналу данные поступают из памяти по шине 14 через шинный формирователь 30 соответствующего блока 3 управления на шину 7. При этом в блоке 1 элементами 57-59 формируется сигнал СИП, сигнализирующий о том, что данные установлены на шине 7. Процессор принимает данные и снимает сигнал Ввод .При этом снимается сигнал СИП, затем снимается сигнал СИА, завершая ЦИКЛ Ввод . Временная за- держка, вносимая элементами 57-59, должна превышать время считывания ин- фор мации из ОЗУ 54 на шину 7.

В режиме прямого доступа к памяти контроллером 2 ПДП осуществляется захват внутренней шины 7 . Обмен даннь - ми в Этом режиме происходит без участия процессора и осуществляется за счет необходимого количества циклов Ввод или Вывод, формируемых контроллером 2 ПДП. При этом после захва10

15

20

та магистрали 7 контроллер 2 11ДП . обеспечивает передачу по ней адресной информации, поступающей по шине 13 от блока 5, а также передачу сигналов Ввод и Вывод по линиям 15 и 19. Данные от (к) блока 5 передаются одновременно по всем шинам 12 через блоки 3 от (к) блокам 4 памяти, обеспечивая необходимую разрядность информационного слова, превышающую при этом разрядность слова процессора. Чтение или запись данных из (в) ОЗУ 54 происходит за время длительности сигналов Ввод или Вьтод.

Блок 5 ввода-вывода при необходимости обмена данными вырабатывает сигнал требов ания прямого доступа к памяти (ТПД), который поступает по инии 8 в блок 1. После завершения текущего цикла обмена по линии 7 блок 1 вырабатьюает сигнал предоставления рямого доступа к памяти (ППД), поступающий по линии 9 в контроллер 2 ДП. Контроллер 2 ЦЦП в ответ выраба- 25 тывает сигнал подтверждения (ПВ) по инии 6, блокируя блок 1.

После поступления сигнала Запуск по линии 47 шины 10 от блока 5 контроллер выполняет требуемые циклы передачи данных аналогично описанным операциям Ввод и Вьшод, за исключением того, что в адресной части цикла производится выдача импульсного сигнала СИЛ по цепи 18 и осуществяется одновременная выборка всех блоков 4 памяти сигналов ПВ по линии 6. Это позволяет осуществлять одновременное обращение к ячейкам, расположенным в различных блоках памяти. Физически адреса ячеек в каждом блоке имеют одно и то же значение адреса, запоминаемое в регистрах 22 блоков 3. При снятии сигнала ТПД блоком 5 блок 1 снимает с линии 9 сигнал ППД. В результате этого контроллер 2 ПДП отключается от шины 7, линий 15, 18 и 19 управления, снимает сигнал ПВ с линии 6 и блок 1 возобновляет свою работу в программном режиме.

Рассмотрим работу узлов, входящих в ЭВМ.

Операцоинньм блок 1 работает еле-, дующим образом. При поступлении активного (низкого уровня сигнала по цепи 8 ТПД -процессор завершает текущий канальный цикл и формирует сигнал низкого активного уровня в цепи 61,ППД1, подаваемый на вход установ30

35

40

45

50

55

10

15

20

25

529240

ки в 1

630

35

40

45

50

55

триггера 55, при этом на входе установки в О триггера - пас- сивный (низкий) уровень сигнала. Триггер 55 устанавливается в единичное состояние, при этом с выхода триг гера снимается сигнал высокого уровня (ППД), подаваемый из блока Г в контроллер 2 ПДП по цепи 9.

Контроллер в ответ на сигнал ППД формирует сигнал низкого уровня по цепи 6 ПВ, удерживая процессор в сосг- тоянии ожидания и осуществляя выборку блоков памяти. При снятии сигнала низкого, уровня по цепи 8 ТПД триггер 55 устанавливается в состояние О. Затем контроллер устанавливает пассивный уровень в цепи 6 ПВ, обеспечивая подключение блока 1 к шине 7 и возврат его в программный режим об- мена.

Блок 3 обеспечивает формирование сигнала 17 выборки, а также коммутацию потока данных с шины 14 на шину 7 или шину 12 Данные блока 5. Блок работает следующим образом. В программном режиме работы при отсутствии активного (низкого) уровня сигнала на цепи 15. (Ввод) на выходе элемента НЕ 23 формируется уровень О, обеспечивающий на выходе элемента И 25 низкий уровень, подаваемый на первые входы шинных формирователей 30 и 31, обеспечлвающих при этом коммутацию информации с шины 7 или 12 на шину 14. При этом, поступая по цепи 6, высокий уровень сигнала, проходя через элемент НЕ 27, обеспечивает выборку шинного формирователя 30, а сигнал высокого уровня с выхода элемента НЕ 28 - блокировку по второму входу шинного формирователя 31. Информация при этом с шины 7 поступает на шину 14.

В адресной части канального цикла обмена при появлении сигнала низкого уровня по цепи 18 обеспечивается загрузка кода адреса с шины 7 в регистры 21 и 22. В регистр 21 записьшается код адреса выбранного блока памяти, а в регистр 22 - код, определяющий ф,Изический адрес выбранной ячейки.

С выхода регистра 21 код адреса секции (блока памяти поступает ,на первые входы схемы 24 сравнения, а на вторые входы с шины 20 подается код номера секции памяти. Каждому блоку управления присваивается свой , код номера секции памяти, подаваемый

71529240

шины 20. При совпадении кодов шины

к э н

10

15

20 с разрядами адреса секции памяти, поступающими с выхода регистра 21, на выходе схемы 24 сравнения формиру-г ется сигнал низкого уровня, а на выходе элемента И-НЕ 26 при этом формируется потенциал выборки адресуемой секции памяти, подаваемый по линии 17 на входы элементов И-НЕ 52 и 53 блока 4 , С выхода регистра 22 код адреса ячейки блока 4 поступает по шине 6 на адресные входы ОЗУ 54.

В части цикла Вьюод блок 3 обеспечивает коммутацию информации с шины 7 на шину 14 при отсутствии сигнала низкого уровня на цепи 6. При наличии сигнала низкого уровня на линии 6 (режим ПДП) обеспечивается блокировка по второму входу шинного 20 формирователя 30 и включение в рабочий режим блока 31 . При этом обеспечивается коммутация информации с шины 2 на шину 14. Одновременно на выходе элемента И-:ПЕ 26 Формируется сигнал высокого уровня, обеспечивая на линии 17 активный уровень незави симо от результата работы схемы 24 сравнения, что позволяет активизироРежим чтения реализуетсгя при низ ком уровне сигнала по цепи 15. При этом информация, записанная в ячейк ОЗУ по адресу на шине 16, выдается на шину 14.

Контроллер ПДП работает следующи образом.

Контроллер 2 ПДП состоит из следующих функциональных блоков: комму татора адреса и автомата управления канальными циклами. Коммутатор адре са реализован на элементах 40 и 43.

При наличии пассивного (низкого) уровня сигнала на линии 9 сигнал вы сокого уровня в линии 6 с Выхода ин вертора 40 блокирует шинный формиро ватель 43.

При появлении активного уровня н линии 9. шинный формирователь 43 обе печивает коммутацию кодов адреса с шины 13 формируемого блоком 5) на внутреннюю шину 7.

Ти7 канального цикла Ввод или 25 Вывод определяется блоком 5, форм рующим сигнал высокого уровня по це пи 49 при цикле Вывод и низкого уровня при цикле Ввод. Скорость о мена определяется тактовой частотой

35

40

вать все блоки 4 памяти. В части цик ЗО подаваемой от блока 5 по линии 48. ла Ввод при поступлении активного (низкого) уровня сигнала по линии 15 (Ввод) и наличии высокого уровня сигнала на линии 17 обеспечивается коммутация шинного формирователя 30 (j-ши 3 при низком уровне сигнала на линии б)5 пропускающего информацию с щины 14 На шину 7 для чтения ее блоком 1 (в режиме ПДП при наличии ак- тивного сигнала в цепи 6 информация с шины 14 передается на шину 12 шинным формирователем 31) . . Узел памяти работает следующим образом .

Режим записи. В адресной части цикла в выбранный б.ок памяти по цепи 17 на входы элементов 52 и 53 подается потенциал высокого уровня. При подаче сигнала низкого уровня по ие- ци 19 (Вывод) на выходе элемента 50 появляется 1, обеспечивающая на выходе элемента 52 активный низкий уровень, подаваемый на вход выборки кристалла ОЗУ 54. При этом сигнал высокого уровня на входе элемента 53 формирует на входе кода операции ОЗУ сигнал записи, обеспечивающий запись информации с шины 14 по адресу, определяемому шиной 16.

45

55

Блок 2 начинает работать при наличи сигнала 47 Запуск и высокого уров ня на линии ППД 9. Работа контролле ра в циклах Ввод и Вывод поясня ется диафрагмами на фиг. 6.

Формула изобретени

Электронная вычислительная маши с прямым доступом в память, содержа щая операнионный блок, контроллер прямого доступа в память, первьм бл памяти, блок ввода-вывода, причем вход подтверждения блокировки опера ционного блока соединен с входом ра решения работы контроллера прямого доступа в памятьj отличаю- щ а я с я тем, что, с целью повьше ния быстродействия за счет возможно ти передачи за один цикл прямого до ступа в память нескольких слов инфо мации, устройство дополнительно содержит с второго по М-й блоки памят и с первого по М-й блоки управления памятью (М- число слов, передаваемы за ОДШ1 цикл прямого доступа) , причем выход управления вводом операци ного блока и выход управления чтени ем из памяти контроллера прямого

8

Режим чтения реализуетсгя при низком уровне сигнала по цепи 15. При этом информация, записанная в ячейке ОЗУ по адресу на шине 16, выдается на шину 14.

Контроллер ПДП работает следующим образом.

Контроллер 2 ПДП состоит из следующих функциональных блоков: коммутатора адреса и автомата управления канальными циклами. Коммутатор адреса реализован на элементах 40 и 43.

При наличии пассивного (низкого) уровня сигнала на линии 9 сигнал высокого уровня в линии 6 с Выхода инвертора 40 блокирует шинный формирователь 43.

При появлении активного уровня на линии 9. шинный формирователь 43 обеспечивает коммутацию кодов адреса с шины 13 формируемого блоком 5) на внутреннюю шину 7.

Ти7 канального цикла Ввод или Вывод определяется блоком 5, формирующим сигнал высокого уровня по цепи 49 при цикле Вывод и низкого уровня при цикле Ввод. Скорость обмена определяется тактовой частотой.

5

0

О подаваемой от блока 5 по линии 48.

5

5

Блок 2 начинает работать при наличии сигнала 47 Запуск и высокого уровня на линии ППД 9. Работа контроллера в циклах Ввод и Вывод поясня- ется диафрагмами на фиг. 6.

Формула изобретения

Электронная вычислительная машина с прямым доступом в память, содержащая операнионный блок, контроллер прямого доступа в память, первьм блок памяти, блок ввода-вывода, причем вход подтверждения блокировки операционного блока соединен с входом раз- решения работы контроллера прямого доступа в памятьj отличаю- щ а я с я тем, что, с целью повьше- ния быстродействия за счет возможности передачи за один цикл прямого доступа в память нескольких слов информации, устройство дополнительно содержит с второго по М-й блоки памяти и с первого по М-й блоки управления памятью (М- число слов, передаваемых за ОДШ1 цикл прямого доступа) , при , чем выход управления вводом операцион- ного блока и выход управления чтением из памяти контроллера прямого

.доступа в память объединены через МОНТАЖНОЕ ИЛИ и соединены с входами управления чтением с первого по М-й блоков памяти и с первыми входами задания режима с первого по М-й блоков управления памятью, выход управления выводом операционного блока и выход управления записью в память контроллера прямого доступа в память объединены через МОНТАЖНОЕ ИЛИ и соединены с входами управления записью с первого по М-й блоков памяти, выходы признака обращения к. памяти операционного блока и контроллера прямого доступа в память объединены через МОНТАЖНОЕ 11ПИ и соединены с входами запуск с первого по М-й блоков управления памятью, выход подтверждения выборки контроллера прямого доступа соединен с входом подтверждения блокировки операционного блока и с входами за-. Дания режима с первого по М-й блоков управления памятью, информационный вход-выход операционного блока через информационную шину соединен с информационным выходом контроллера прямого доступа в память и с первыми информационными входами-выходами с первого по М-й блоков управления памятью, выход требования передачи блока ввода-вывода соединен с входом требования блокировки операционного блока, выход кода операции, тактовый выход и выход запуска передачи блока ввода-вывода соединены с одноименны ми входами контроллера прямого доступа в память, информационный вход и выход признака окончания передачи которого соединены с одноименными выходом и входом .блока ввода-вывода, с первого по М-й информационные вхо ды- выходыкоторого соединены с вторыми- информационньми входами-выходами с первого по М-й блоков управления памятью, выходы идентификации памяти, информационные выходы и третьи информационные .входы-выходы которых соединены соответственно с входами выборки, адресными входами и информационными входами-выходами с первого по М-й блоков памяти, причем контроллер прямого доступа в память содержит шинньй формирователь, с первого по четвертый элементы НЕ, с первого по пятый тригг еры, первьп и второй эле- менты И-НЕ, первый и второй элементы И, причем первые информационные вход и выход контроллера соединены соот

л-

10

15

20

25 55

30

35

40

45

ветственно с информационными входом .и выходом шинного формирователя, вход выборки которого соединен с вьгходом первого элемента НЕ и с выходом подтверждения выборки контроллера, вход разрешения работы которого соединен с входами установки в 1 с первого по третий триггеров и с входами уста- новки в О четвертого и пятого триггеров, ииверсньй выход первого триггера соединен с входом второго элемента НЕ, выход которого соединен с выходом признака обращения к памяти контроллера, выход признака окончания передачи которого соединен с выг ходом первого элемента И-НЕ, первый вход которого соединен с выходом пятого триггера, синхровходы с первого по -третий и пятого триггеров соединены с тактовым входом контроллера, вход запуска которого соединен с входом третьего элемента НЕ, выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с информационным входом первого триггера, прямой вьгход которого соединен с вторыми входами первого и .второго элементов И-НЕ и информационным входом второго триггера, выход которого соединен с третьими входами первого и второго элементов И-НЕ, с входом установки в 1 четвертого триггера и с информационным входом третьего тригг.ера, прямой выход которого соединен с четвертыми входами первого и второго элементов И-НЕ и с синхровходом четвертого триггера, выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединены соответствен- ,но с выходом четвертого элемента НЕ и с вьгходом управления чтением из памяти контроллера, вход кода операции которого соединен с входом четвертого элемента НЕ и с первым входом второго элемента И, выход которого соединен с выходом управления записью в память контроллера, инверсный вьгход третьего триггера соединен с информа- ционным входом пятого триггера и вторым входом второго элемента И, причем казвдый блок управления памятью содержит с первого по третий элементы НЕ, первый и второй шинные формирователи, первьй и второй регистры, схему сравнения, элемент И, элемент И-НЕ, причем пход запуска блока соединен с синхровходами первого и второго реи

rJHCTpoB, икфор чаииоКл ьге вк ,/..1., котор соединены с первым информационным в|ходом-выходом блока и с первым ин- фЬрмационным входом-выходом первого ш|инного формироватедя, вход выборки которого соединен с выходом первого

И с входом второго элемента НЕ, выход которого соединен с входом выборки второго шинного формирозателя,, первый ииформаиионный вход- - -- од которого соединен с вторым инфс-рмационным входом-выходом блока, третий информаиион ный вход-выход которого соединен с вторыми информационными входами-выхо- ами первого и второго шинных форми- Гователей, входы управления напраиле- 11Ием передачи которых соединены с вы

12

венно

ходом элемента И, nepBbtfi вход которого соединен с выходом элемента И-ИЕ и с выходом идентификации памяти блока, первый вход задания режима которого соединен с входом третьего элемента НЕ, выход которого соединен с вторым входом .элемента И, второй вход задания режима блока соединен с входом первого элемента НЕ и с первым входом элемента И-НЕ, второй вход которого соединен с выходом схемы сравнения, первый и второй информационные входы которой соединены соответст- с входом номера секции памяти блока и выходом первого регистра, выход второго регистра соединен с информационным выходом блока.

Физ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для ввода информации от аналоговых датчиков | 1988 |

|

SU1578706A1 |

| Устройство сопряжения с памятью | 1985 |

|

SU1262515A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство для сопряжения ЭВМ с селекторным каналом | 1986 |

|

SU1401472A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах для обработки информации. Цель изобретения - повышение быстродействия за счет возможности передачи за один цикл прямого доступа в память нескольких слов информации. Электронная вычислительная машина с прямым доступом в память содержит операционный блок, контроллер прямого доступа в память, M блоков управления памятью, где M - количество слов, передаваемых за один цикл прямого доступа в память, M боков памяти, блок ввода-вывода. 6 ил.

фигМ

/(ш У

У7 V9 18

5 19

llffffbfl

Ф&/з.5

| Патент ФРГ № 3224034, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Клингман Э | |||

| Проектирование микропроцессорных систем, М.: Мир, 1980, с | |||

| Электромагнитное реле | 1922 |

|

SU466A1 |

Авторы

Даты

1989-12-15—Публикация

1987-08-24—Подача