TVOJ

Од С0

sl

0ies.f

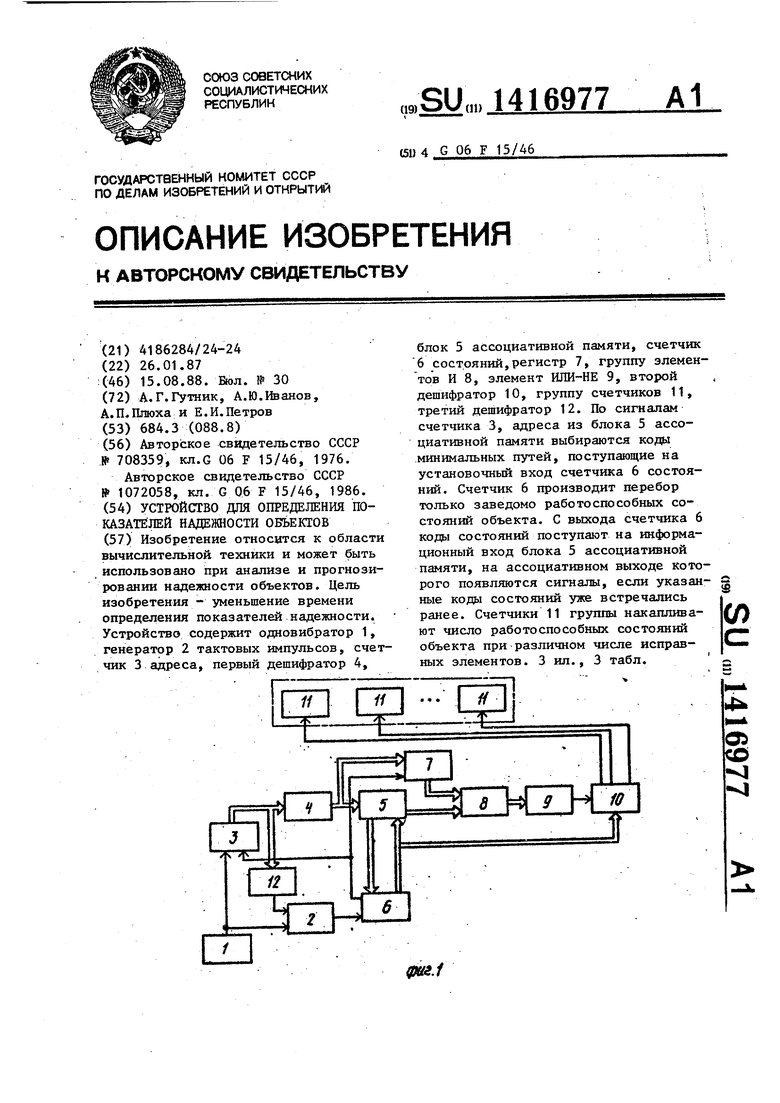

Изобретение относится к вычислительной технике и может быть использовано при анализе и прогнозировании надежности объектов.

Цель изобретения - повышение быстродействия устройства.

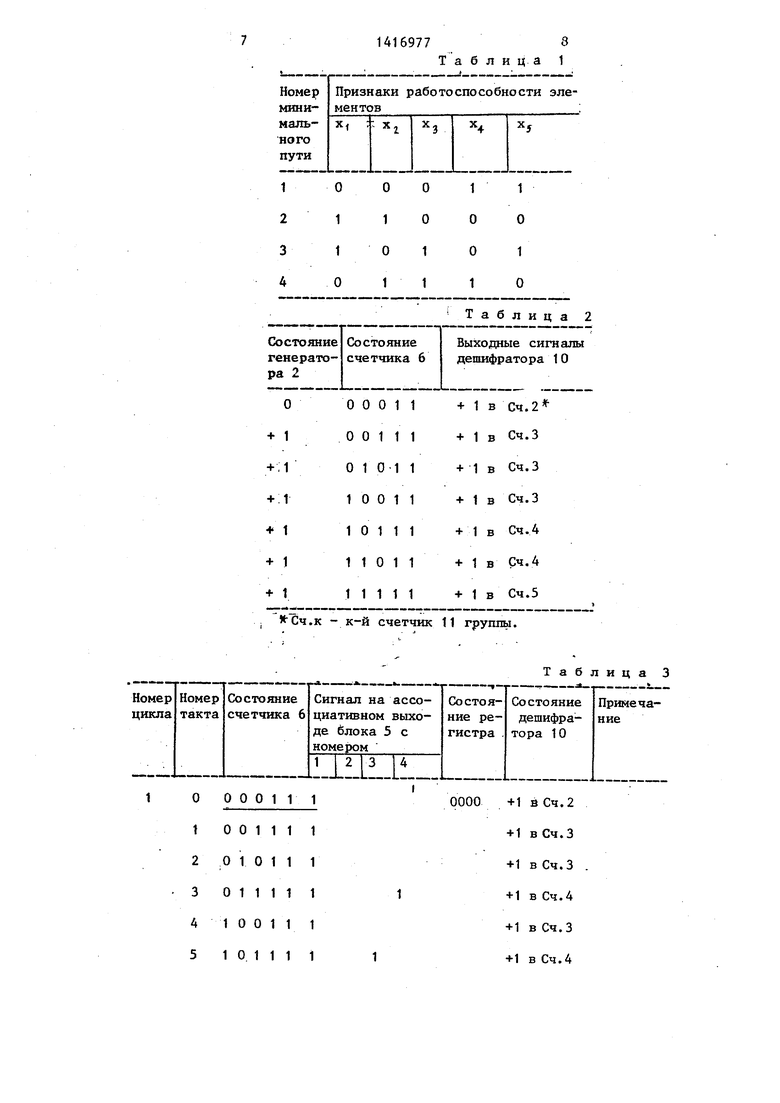

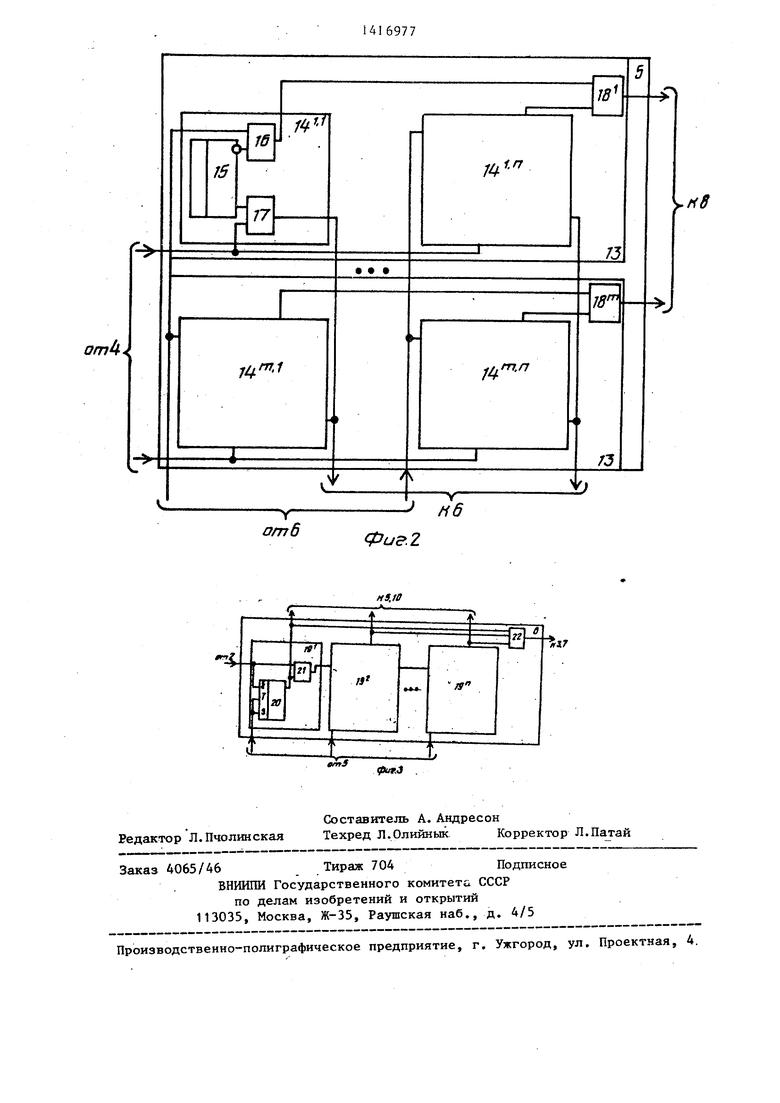

На фиг. 1-3 представлена схема устройства для определения показателей надежности объектов.

Устройство для определения показателей надежности объекта содержит одновибратор 1, генератор 2 тактовых импульсов, счетчик 3 адреса, первый дешифратор 4, блок 5 ассоциативной памяти, счетчик 6 состояний, регистр ; 7, группу 8 элементов И, элемент :ИЛИ-НЕ 9, второй дешифратор 10, гуп- пу счетчиков 11, третий дешифратор ;12, ячейки 13 блока 5 ассоциативной памяти, разряды 14 ячейки, элементы 15 памяти, элемент ИЛИ 16, элементы И 17 и 18, разряды 19 счетчика состояний, счетные триггеры 20 и элементы И 21 и 22.

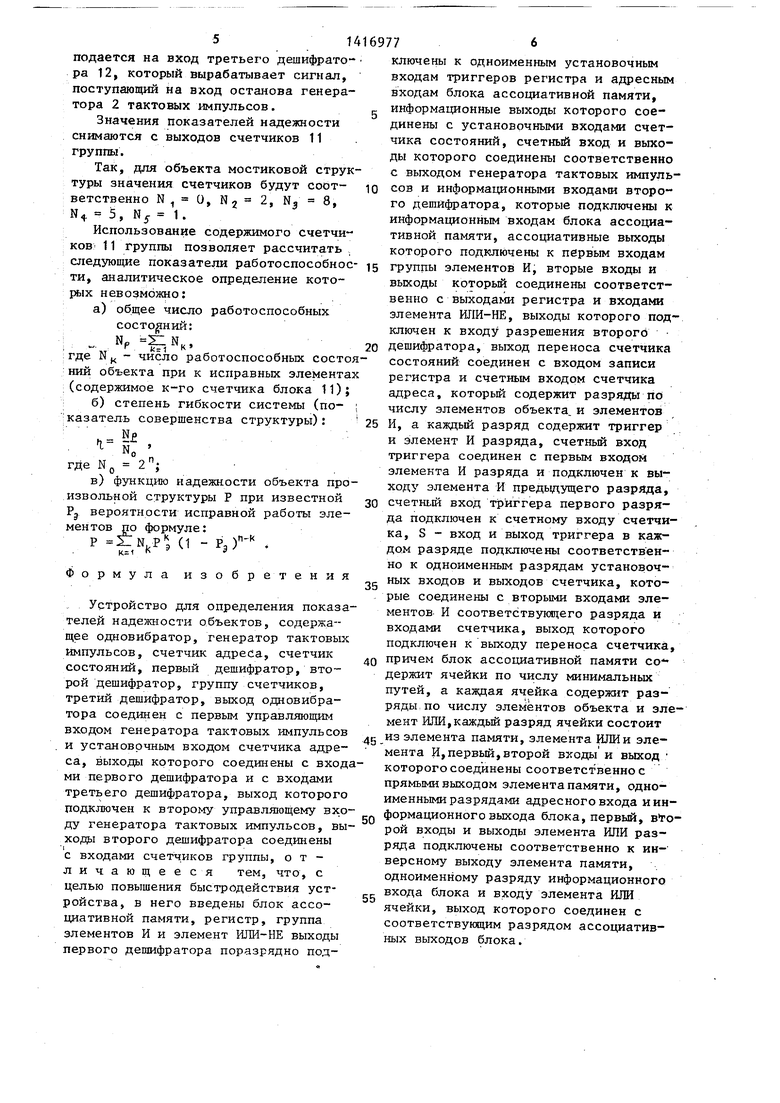

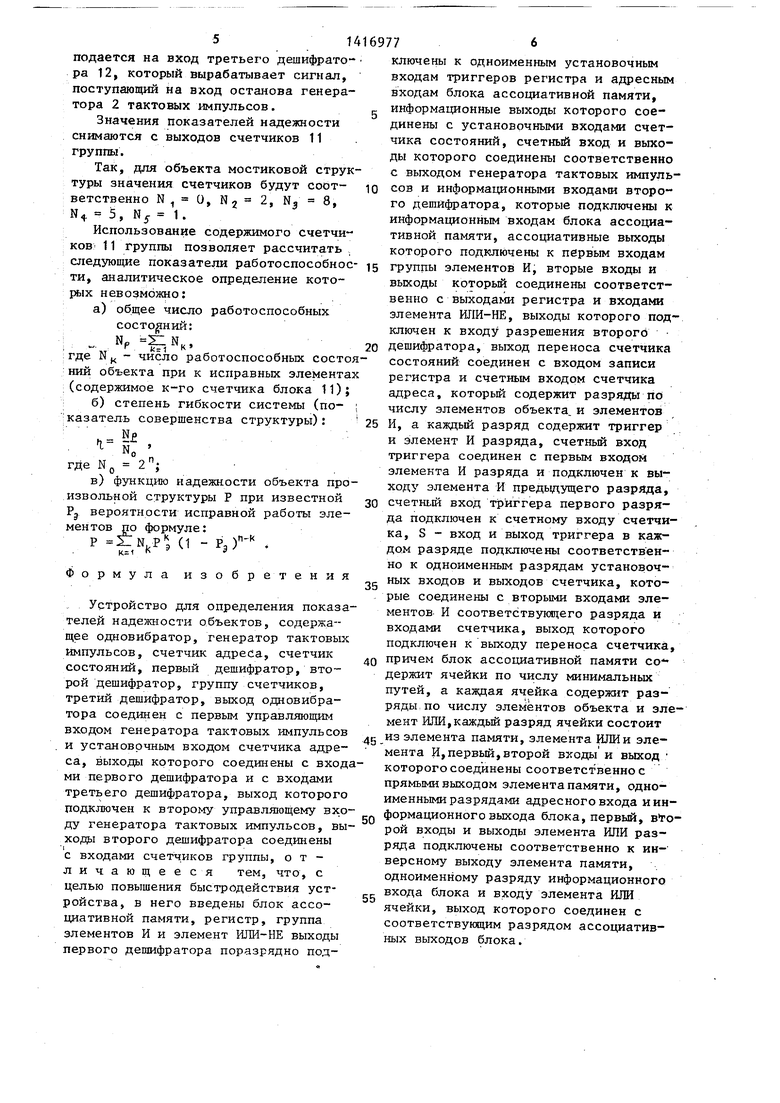

Блок 5 ассоциативной памяти предназначен для хранения кодов минимальных путей. Число элементов исследуемого объекта определяет разрядность блока 5, а число минимальных путей - его емкость. В качестве примера в табл. 1 представлены коды минимальных путей для мостиковой схемы, содержащей пять элементов с третьим элементом в; диагонали.

Подключение г-шформационных выходов блока 5 ассоциативной памяти к установочным входам счетчика состояний позволяет заносить в последний коды минимальных путей в его начальных значений дов счетчика 6 состояний ционными входами блока 5 возможность поиска памяти такого кода, ет код состояния счетчика 6 (когда все единицы кода минимального пути совпадут хотя бы с частью единиц кода состояния счетчика). Накрытие отображается на ассоциативном выходе блока 5 и позволяет исключить повторньй учет работоспособного состояния анализируемого объекта.

Счетчик 6 состояний предназначен .для перебора кодов только работо10

15

20

25

30

35

качестве дд Связь выхо- с информа- обеспечивает в ассоциативной который накрьша- .

50

гистра 7, что обеспечивает измен состояний счетчика 3 и занесение формации в регистр 7 в конце ци работы счетчика состояний.

Регистр 7 предназначен для за нания номеров рассмотренных мини ных путей и управления вторым де фратором 10. Наличие единицы в i разряде регистра 7 () запре повторное занесение в группу сче ков 11 информации об исправном с стоянии объекта, если такое сост ние встречалось при рассмотрении минимального пути.

Второй дешифратор 10 служит д преобразования кода количества р тоспособных элементов объекта, п ступающего на информационные вхо в унитарньй код. Если исправны к элементов объекта (в коде содерж ся к едршиц), то сигнал появляет на к - м выходе () дешифрат 10 и поступает на вход соответст щего к-го счетчика в группе сче ков 11 при наличии сигнала на вх разрешения дешифратора.

Дешифратор 10 состоит из сумм ра единиц.

Третий дешифратор 12 предназн для выработки сигнала окончания ты устройства. После пересмот всех минимальных путей с выхо счетчика 3 адреса снимается код са m - го слова и поступает на в дешифратора 12, на выходе которо вырабатывается сигнал, запрещающ работу генератора 2 тактовых имп сов. Выход дешифратора 12 соедин с вторым управляющим входом (ост ва) генератора 2 тактовых импуль

Структура счетчика состояний зволяет изменить логику его рабо Вначале в него заносится код мин мального пути из блока 5 ассоциа ной памяти. В дальнейшем с посту нием сигналов на счетный вход из нять состояние смогут лишь те тр геры, которые первоначально были установлены в нуль. Единичное зн ние остальных триггеров удержива благодаря наличию на S-входах ко минимального пути от блока 5 асс циативной памяти. Таким образом, мирование импульсов, поступающих

способных состояний объекта. Счетчик генератора 2 тактовых импульсов.

0

5

0

5

0

5

д

0

гистра 7, что обеспечивает изменение состояний счетчика 3 и занесение информации в регистр 7 в конце цикла работы счетчика состояний.

Регистр 7 предназначен для запоминания номеров рассмотренных минимальных путей и управления вторым дешифратором 10. Наличие единицы в i -м разряде регистра 7 () запрещает повторное занесение в группу счетчиков 11 информации об исправном состоянии объекта, если такое состояние встречалось при рассмотрении i-To минимального пути.

Второй дешифратор 10 служит для преобразования кода количества работоспособных элементов объекта, поступающего на информационные входы в унитарньй код. Если исправны к элементов объекта (в коде содержится к едршиц), то сигнал появляется на к - м выходе () дешифратора 10 и поступает на вход соответствующего к-го счетчика в группе счетчиков 11 при наличии сигнала на входе ; разрешения дешифратора.

Дешифратор 10 состоит из сумматора единиц.

Третий дешифратор 12 предназначен для выработки сигнала окончания работы устройства. После пересмотра всех минимальных путей с выходов счетчика 3 адреса снимается код адреса m - го слова и поступает на входы дешифратора 12, на выходе которого вырабатывается сигнал, запрещающий работу генератора 2 тактовых импульсов. Выход дешифратора 12 соединен с вторым управляющим входом (останова) генератора 2 тактовых импульсов.

Структура счетчика состояний по- зволяет изменить логику его работы. Вначале в него заносится код минимального пути из блока 5 ассоциативной памяти. В дальнейшем с поступле- нием сигналов на счетный вход изменять состояние смогут лишь те триггеры, которые первоначально были установлены в нуль. Единичное значение остальных триггеров удерживается благодаря наличию на S-входах кода минимального пути от блока 5 ассоциативной памяти. Таким образом, суммирование импульсов, поступающих от

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения показателей надежности объектов | 1987 |

|

SU1430968A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Устройство управления обращением к подпрограммам | 1984 |

|

SU1273929A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1990 |

|

SU1795458A1 |

Изобретение относится к области вычислительной техники и может быть использовано при анализе и прогнозировании надежности объектов. Цель изобретения - уменьшение времени определения показателей надежности. Устройство содержит одновибратор 1, генератор 2 тактовых импульсов, счетчик 3 адреса, первый дешифратор 4, блок 5 ассоциативной памяти, счетчик 6 состояний,регистр 7, группу злемен- тов И 8, злемент ИЛИ-НЕ 9, второй дешифратор 10, группу счетчиков 11, третий дешифратор 12. По сигналам счетчика 3, адреса из блока 5 ассоциативной памяти выбираются коды минимальных путей, поступающие на установочный вход счетчика 6 состояний. Счетчик 6 производит перебор только заведомо работоспособных состояний объекта. С выхода счетчика 6 коды состояний поступают на информационный вход блока 5 ассоциативной памяти, на ассоциативном выходе которого появляются сигналы, если указанные коды состояний уже встречались ранее. Счетчики 11 группы накапливают число работоспособных состояний объекта при различном числе исправных злементов. 3 ил., 3 табл. i СЛ

6 содержит п разрядов. Выход переноса счетчика 6 подключен к счетному . выходу счетчика 3 и входу записи репроизводится только триггерами, которые бьши вначале установлены в нуль. Например, если начальное значение

314

счетчика 6 равно коду последнего минимального пути 01110(табл.1), то последующими значениями счетчика 6 будут соответственно коды 01111, 11110 И11111. Тем самым производится перебор только заведо1 о работоспособных состояний объекта, что приводит к резкому повьшению быстродействия устройства.

Устройство для определение показателей надежности работает следующим образом.

В исходном состоянии в блок 5 ассоциативной памяти занесены коды минимальных путей, а счетчик 3 адреса, счетчик 6 состояний, регистр 7 и группы счетчиков 11 обнулены.

Запуск устройства производится пр срабатьтании одновибратора 1, сигнал с выхода которого подается на установочный вход счетчика 3 адреса и первый управляющий вход запуска генератора 2 тактовых импульсов. Счетчик 3 адреса устанавливается в нулевое состояние. Сигнал с выходов счетчика 3 поступают на входы первого дешифратора 4. Сигналом с первого выхода дешифратора 4 выбирается код первого минимального пути, записанный в блоке 5 ассоциативной памяти по первому адресу. Этот код подается на устано- .вочные входы счетчика 6 состояний и далее с выходов счетчика 6 на входы второго дешифратора 10. На вход разрешения дешифратора 10 подается единица, так как регистр 7 обнулен, а следовательно, все элементы И группы 8 закрлты и с выхода .элемента 9 ИПИ-НЕ снимается единичный сигнал. С выхода дешифратора 10 в соответствующий счетчик 11 группы поступает сигнал.

Следующий такт начинается с поступлением сигнала с генератора 2 тактовых импульсов на счетный вход счетчика 6 состояний.

Пря подаче на счетный вход счетчика 6 импульсов от генератора 2 в работе счетчика 6 принимают участие только те его разряды, на которые с блока 5 ассоциативной памяти подаются нулевые сигналы. С выходов счетчика 6 сигналы подаются на дешифратор 10, который: разблокирован на все время просмотра первого минимального пути. С выходов дешифратора 10 сигналы поступают в группы счетчиков 11 совпадений.

977

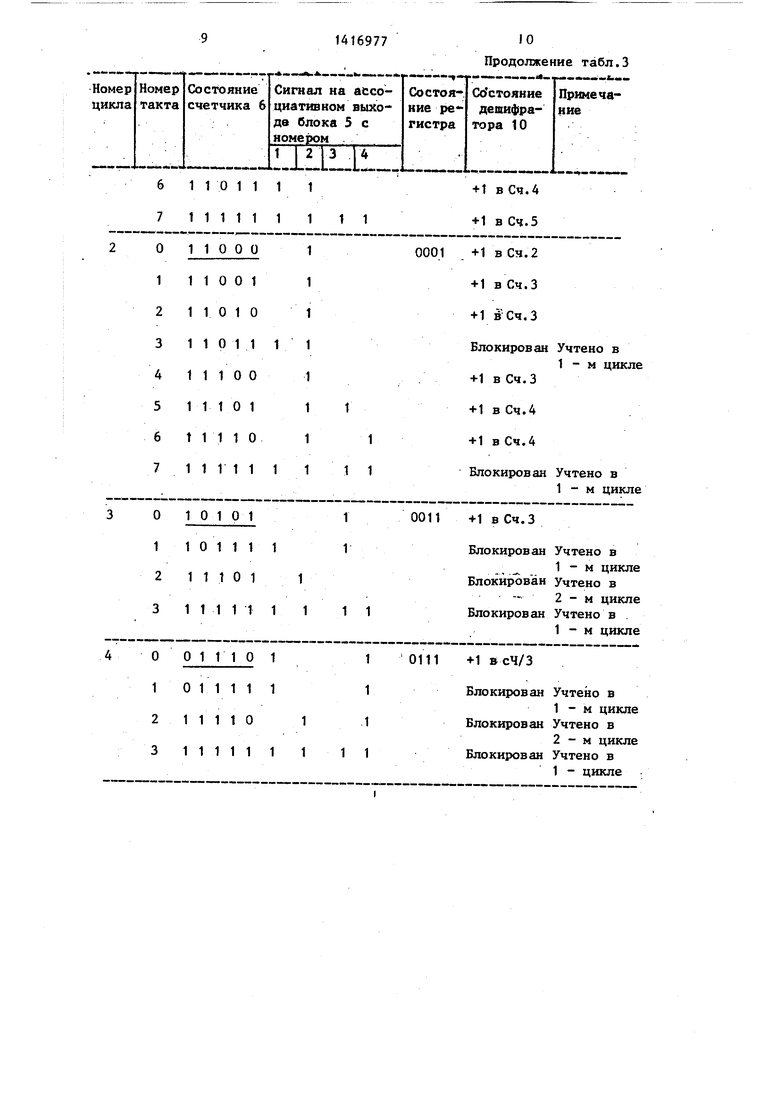

Работу счетчика 6 и дешифратора 10 во время первого цикла поясняет табл, 2.

Когда в результате работы счетчика 6 все его разряды устанавливаются в единичное состояние, на выходе переполнения счетчика 6 появляется единичный сигнал, который увеличива0 ет содержимое счетчика 3 адреса на единицу, а следовательно, модифицирует адрес слова в блоке 5 ассоциативной памяти. Этот же сигнал разрешает занесение единицы в младший разряд

5 регистра 7. На этом первый цикл работы устройства закончен.

По модифицированному адресу из блока 5 ассоциативной памяти считывается код следующего минимального пу-

0 ти и начинается очередной цикл работы устройства.

В каждом к-м цикле () необходимо исключить из рассмотрения те состояния исследуемого объекта, кото-

5 рые бьши учтены в предьщущих циклах,

иначе в случае повторного учета в счетчиках t1 группы накапливаются неверные значения. С этой целью код состояния объекта из счетчика 6 по0 дается на информационные входы блока 5 ассоциативной памяти. Накрытие поданного кода одним из кодов минимальных путей (чему соответствует совпадение всех единиц кода минимального пути хотя бы с частью единиц поданного кода) отображается единицей на соответствующем, например, р-м ассоциативном выходе блока 5. Если номер р ассоциативного выхода меньше к,

Q это свидетельствует о повторном рассмотрении уже просмотренного минимального пути. Поскольку в триггерах регистра 7 с номерами меньше к уже записаны единицы, то р-й элемент И из группы 8 срабатывает и на выходе элемента ИЛИ-НЕ 9 появляется нуль, блокирующий срабатывание второго дешифратора 10, в результате запре- щается занесение информации в группу счетчиков 11.

Работа блока 5 ассоциативной памяти, счетчика 6 состояний, регистра 7, второго дешифратора 10 пояснена в табл. 3.

Окончание работы устройства происходит следующим образом.

При очередном окончании цикла модифицированное значение счетчика 3 адреса, представляющее код числа m

5

5

0

5

51416977

вход третьего дешифрато- ый вырабатывает сигнал, на вход останова генеравых импульсов.

показателей надежности выходов счетчиков 11

объекта мостиковой струксчетчиков будут соот10

кл вх вх ин ди чи ды с со го ин ти к

ветственно N, 0, , N3 8, N 5, N 1.

Использование содержимого счетчиков 11 группы позволяет рассчитать

следующие показатели работоспособное- 5 группы элементов И, вторые входы и ти, аналитическое определение которых невозможно:

а)общее число работоспособных состояний:

I - .Np.,,

где N ц - число работоспособньк состояний объекта при к исправных элементах (содержимое к-го счетчика блока 11);

б)степень гибкости системы (по- ; казатель совершенства структуры):

.- N

N:

где NO

в)функцию надежности объекта провыходы которьй соединены соответственно с выходами регистра и входами элемента ИГШ-НЕ, выходы которого подключен к входу разрещения второго

20 дешифратора, выход переноса счетчика состояний соединен с входом записи регистра и счетным входом счетчика адреса, которьй содержит разряды по числу элементов объекта, и элементов

25 И, а каждьй разряд содержит триггер и элемент И разряда, счетньй вход триггера соединен с первым входом элемента И разряда и подключен к выходу элемента И предыдущего разряда, счетньй вход триггера первого разряда подключен к счетному входу счетчика, S - вход и выход триггера в каждом разряде подключены соответственно к одноименным разрядам установочных входов и выходов счетчика, которые соединены с вторыми входами эле- Устройство для определения показа- ментов И соответствукядего разряда и

извольной структуры Р при известной PJ вероятности исправной работы элементов по формуле:

р {J пК / ri Nfl-k

30

/РЭ (1 - Р.)

Формула изобретения

35

телей надежности объектов, содержащее одновибратор, генератор тактовых импульсов, счетчик адреса, счетчик состояний, первый дешифратор, второй дешифратор, группу счетчиков, третий дешифратор, выход одновибра- тора соединен с первым управляющим

входами счетчика, выход которого подключен к вьпсоду переноса счетчика, 40 причем блок ассоциативной памяти со- держит ячейки по числу минимальных путей, а каждая ячейка содержит раз- рядЫ:По числу элементов объекта и элемент ИЛИ, каждьй разряд ячейки состоит

входом генератора тактовых импульсов из элемента памяти, элемента ИЛИ и эле- и установочным входом счетчика адре- „ента И,первьй,второй входы и выход са, выходы которого соединены с входа- которого соединены соответственное ми первого дешифратора и с входами третьего дешифратора, выход которого

прямыми выход ом элемента памяти, одноименными раз рядами адресного входа иин

подключен к второму управляющему вхо- формационного выхода блока, первьй, вТо- ду генератора тактовых импульсов, вы- рой входы и выходы элемента ИЛИ раз- ходы второго дешифратора соединены

ряда подключены соответственно к ин- версному выходу элемента памяти, одноименному разряду информационного gj. входа блока и входу элемента ИЛИ ячейки, выход которого соединен с соответствующим разрядом ассоциативных выходов блока.

с входами счетчиков группы, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок ассоциативной памяти, регистр, группа элементов И и элемент ИЛИ-НЕ выходы первого дешифратора поразрядно под

ключены к одноименным установочным входам триггеров регистра и адресным входам блока ассоциативной памяти, информационные выходы которого соединены с установочными входами счетчика состояний, счетньй вход и выходы которого соединены соответственно с выходом генератора тактовых импульсов и информационными входами второго дешифратора, которые подключены к информационным входам блока ассоциативной памяти, ассоциативные выходы которого подключены к первым входам

входами счетчика, выход которого подключен к вьпсоду переноса счетчика, причем блок ассоциативной памяти со- держит ячейки по числу минимальных путей, а каждая ячейка содержит раз- рядЫ:По числу элементов объекта и элемент ИЛИ, каждьй разряд ячейки состоит

из элемента памяти, элемента ИЛИ и эле- „ента И,первьй,второй входы и выход которого соединены соответственное

прямыми выход ом элемента памяти, одноименными раз рядами адресного входа иинформационного выхода блока, первьй, вТо рой входы и выходы элемента ИЛИ раз-

ряда подключены соответственно к ин- версному выходу элемента памяти, одноименному разряду информационного входа блока и входу элемента ИЛИ ячейки, выход которого соединен с соответствующим разрядом ассоциативных выходов блока.

Номер минимальногопути

1 2 3 4

О 1 1 О

Сч.к - к-й счетчик 11 группы.

О

о 1 1

1 о о 1

1 о 1 о

Таблица 2

Таблица 3

Т,3.7

фиг,3

| Устройство для определения надежности объектов | 1977 |

|

SU708359A1 |

| Устройство для определения показателей надежности объектов | 1981 |

|

SU1072058A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1987-01-26—Подача