Изобретение относится к вычислительной технике и может быть использовано при анализе и прогнозировании надежности объектов на основе пока- зателей структурной надежности.

Цель изобретения - повьппение быстродействия устройства.

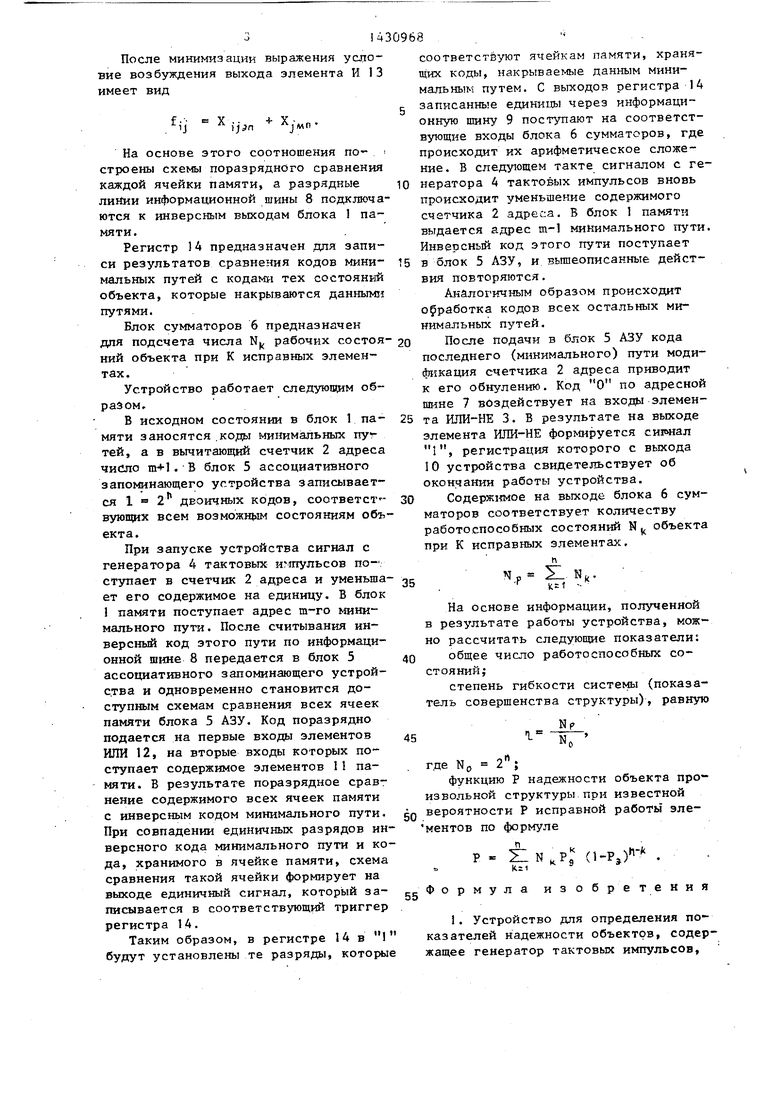

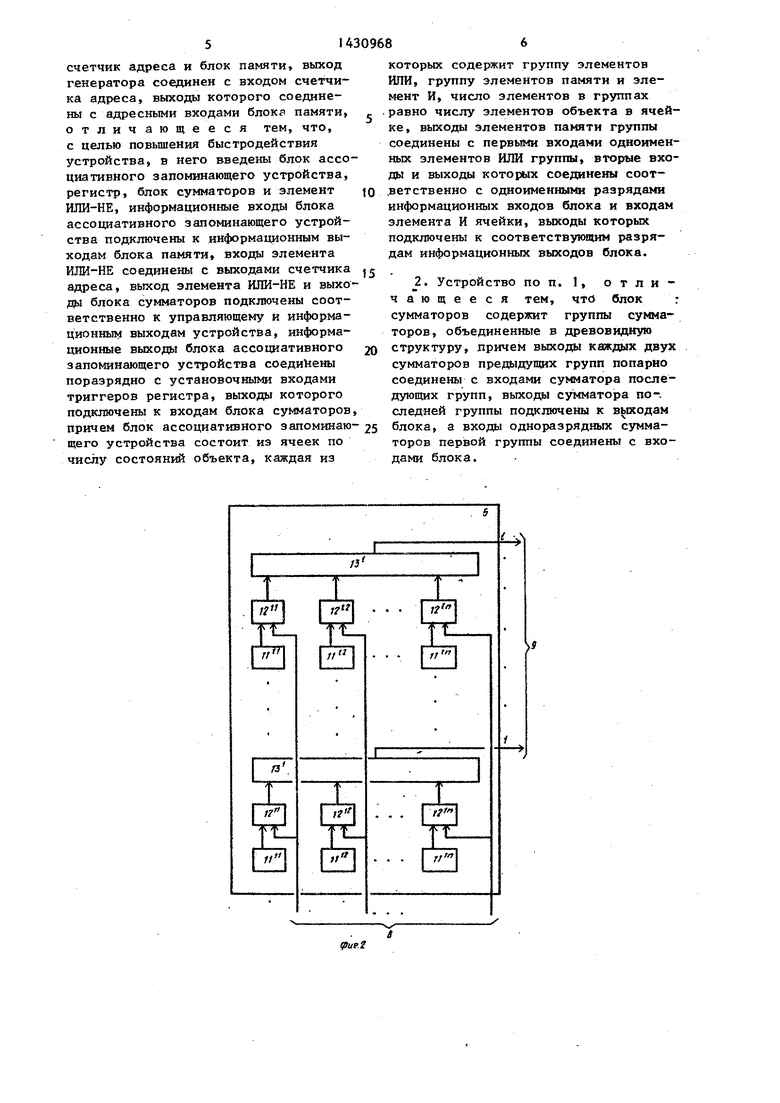

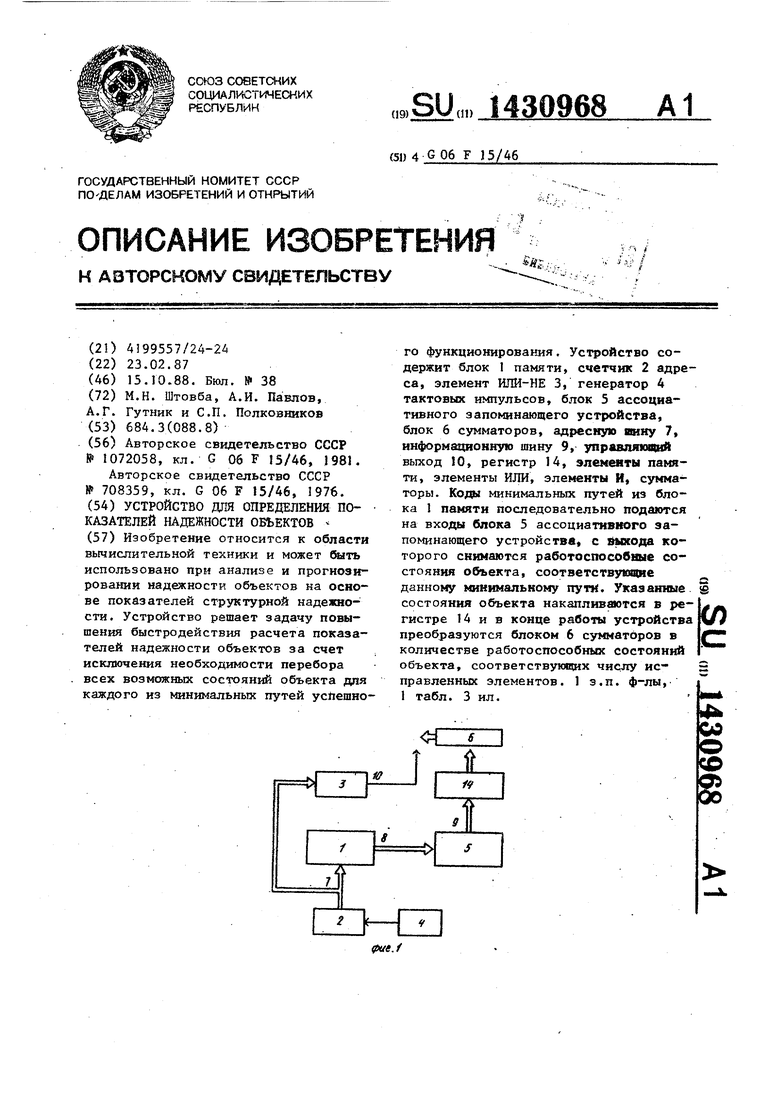

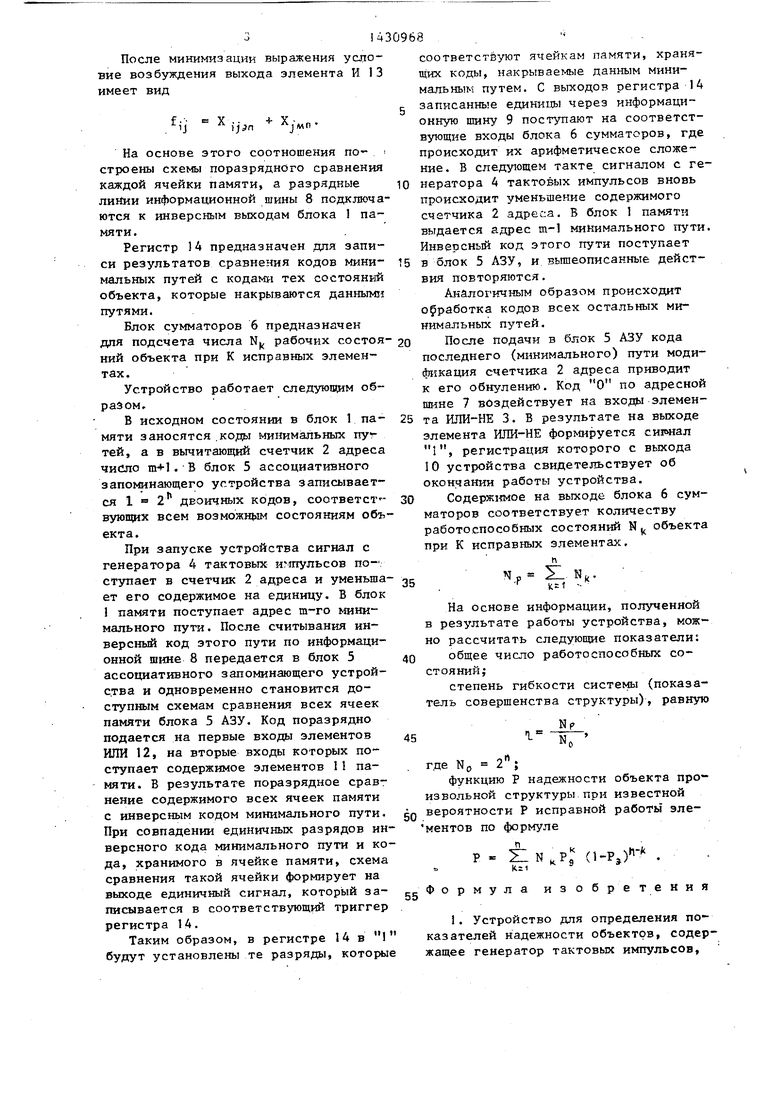

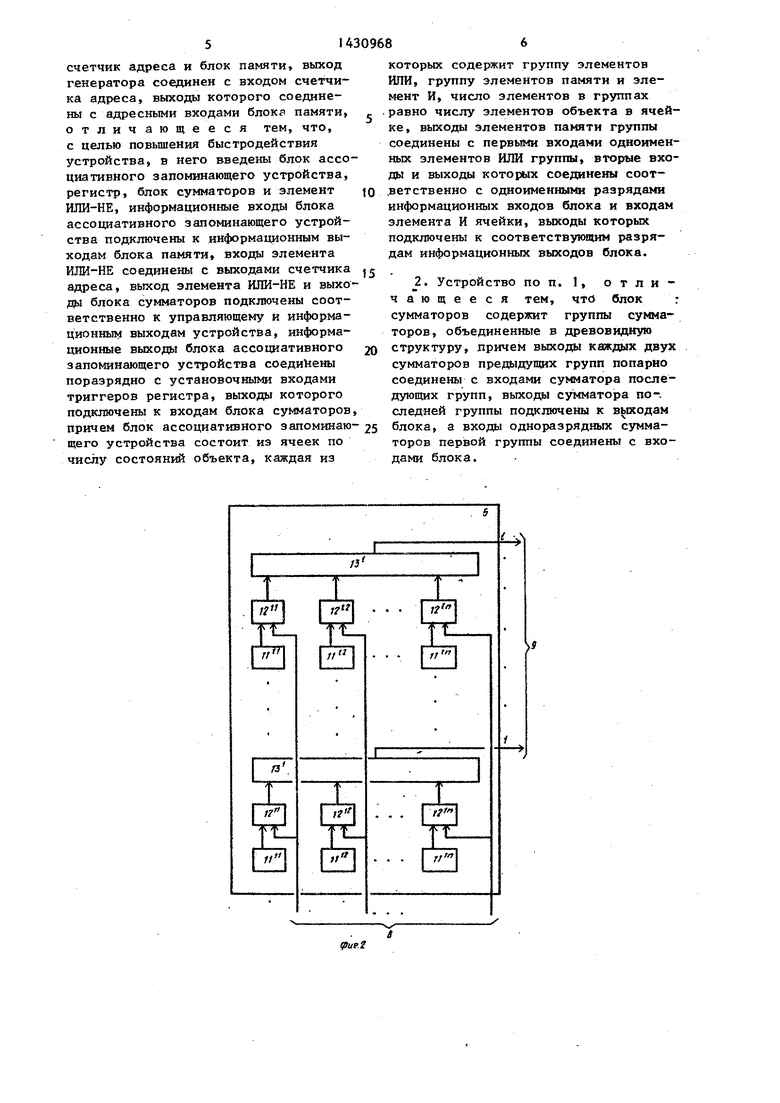

На фиг. 1 и 2 изображена структурная схема предлагаемого устройства; на фиг. 3 - структурная схема много- входового сумматора.

Устройство содержит блок 1 памяти, счетчик 2 адреса, элемент ИЛИ-НЕ 3, генератор 4 тактовых импульсов, блок 5 ассоциативного запоминающего устройства, блок 6 сумматоров, адресную пшну 7, информационную шину 8, информационную шину 9, управ- злементы ИЛИ 12, элементы И 13, per- гистр 14 и сумматоры 15.

Блок 1 памяти предназначен для хранения кодов минимальньк путей. Например, для мостиковой схемы, состоящей из элементов Xj,x,X5,X4 и х (х в диагонали) содер(жимое блока 1, т.е коды минимальных путей, представлено в табл нце.

об окончании работы устройства и возбуждения управляющего выхода 10. Блок 5 ассоциативного запоминающего устройства (АЗУ) предназначен для хранения всех п-разрядных кодов, выполнения операций сравнения кодов минимальных путей, поступающих из блока 1 памяти с хранимыми кодами, фиксации фактов совпадения кодов и выдачи результатов сравнения через регистр 14 в блок 6 сумматоров. Сравнение осуществляется по схеме импликаций. При этом возбуждение соответствующего выхода блока 5 АЗУ проис- ходит в том случае, если единичные значения кода минимального пути являются подмножеством единичных значений кода состояния объекта.

Совокупность элементов ИЛИ 12, подключенных к элементам памяти одной ячейки и одному элементу И 13, образуют схему поразрядного сравнения. Сравнение осуществляется по схеме импликаций. Правило сравнения состоит в следующем. На выходе элемента И 1 3 единичный сигнал должен формироваться только при совпадении единичных значений разрядов кода минимального пути с единичными значениям содержимого соответствующих элементо 11 памяти ячейки АЗУ. Тогда

F 1, если fjid fi- - I fij ...f,-, 1 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения показателей надежности объектов | 1987 |

|

SU1416977A1 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1363307A1 |

| Устройство для селекции признаков объектов | 1990 |

|

SU1725237A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для решения транспортных задач линейного программирования | 1991 |

|

SU1814082A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к области вычислительной техники и может ть использовано при анализе и прогнозировании надежности объектов на основе показателей структурной надеясно- сти. Устройство решает задачу повышения быстродействия расчета показателей надежности объектов за счет исключения необходимости перебора всех возможных состояний объекта для каждого из минимальных путей успешного функционирования. Устройство содержит блок 1 памяти, счетчик 2 адреса, элемент ИЛИ-НЕ 3, генератор 4 тактовых импульсов, блок 5 ассоциативного запоминающего устройства, блок 6 сумматоров, адресную шину 7, информационну шину 9, улравяяюций выход 0, регистр 14, элементы памяти, элементы ИЛИ, элементы И, сумматоры. Коды минимальных путей из блока 1 памяти последовательно подаются на входы блока 5 ассоциативного запоминающего устройстве, с быхода которого снимаются работоспособные состояния объекта, соответствующне данному минимальному пути. Указанные состояния объекта накапливаются в регистре 14 и в конце работы устройства преобразуются блоком 6 сумматоров в количестве работоспособных состояний объекта, соответствующих числу исправленных элементов. 1 з.п. ф-лы, 1 табл. 3 ил. (Л 4ii Од О UD

Из данных таблицы следует, что на- личие 1 в соответствующем разряде показывает наличие и исправность элемента в цепи, а О - отсутствие или о тк аз эл емента.

В данном случае число элементов п 5, число минимальных путей m 4. Разрядность блока определяется числом элементов в исследуемом объекте,г а емкость - числом минимальных путей.

бчетчик 2 адреса содержит Р разрядов и предназначен для формирования адреса ячейки блока 1 памяти.

Элемент ИПИ-НЕ 3 на Р входов предназначен для формирования сигнала

В свою очередь

f п I, если X мп

или X

О,

что эквивалентно

.-.. х- .„$х.,„+ X

где F;

jwn

J jwn

-- значение функции ..на выходе элемента И 13.;

-значение функции на вьпсо- де элемента ИЛИ 12 J;

-значение содержимого элемента 114;

-значение j-ro разряда кода минимального пути;

i iTT

j - iT.

После минимизации выражения уопо- вие возбуждения выхода элемента И 13 имеет вид

ij

X

ijjn

j wn

с записанные единицы через информационную шину 9 поступают на соответствующие входы блока 6 сумматоров, где происходит их арифметическое сложение. В следующем такте сигналом с ге10 нератора 4 тактовых импульсов вновь происходит уменьшение содержимого счетчика 2 адреса. Б блок 1 памяти выдается адрес т-1 минимального пути Инверсньй код этого пути поступает

На основе этого соотношения по- строены схемы поразрядного сравнения каждой ячейки памяти, а разрядные лиМии информационной шины 8 подключаются к инверсным выходам блока 1 памяти.

Регистр 14 предназначен для записи результатов сравнения кодов мини- tg в блок 5 АЗУ, и вьппеописанные деистмал ьных путей с кодами тех состояний объекта, которые накрываются даннымн путями.

Блок сумматоров 6 предназначен для подсчета числа N рабочих состоя- 2о НИИ объекта при К исправных элементах.

Устройство работает следующим образом.

В исходном состоянии в блок 1 па- 25 та ИЛИ-НЕ 3. Б результате на выходе

ВИЯ повторяются.

Аналогичным образом происходит обработка кодов всех остальных минимальных путей.

После подачи в блок 5 АЗУ кода последнего (минимального) пути моди ф{1кация счетчика 2 адреса приводит к его обнулению. Код О по адресной шине 7 воздействует на входы элемен

мяти заносятся.коды минимальных пут тей, а в вычитающий счетчик 2 адреса число го. В блок 5 ассоциативного запоьшнающего устройства записывается 1 2 двоичных кодов, соответст -- вующих всем возможщлм состояниям объекта.

При запуске устройства сигнал с генератора 4 тактовых импульсов по- стзтает в счетчик 2 адреса и уменьша ет его содержимое на единицу. В блок 1 памяти поступает адрес т-го ьшни- мального пути. После считывания инверсный код этого пути по информационной шине 8 передается в блок 5 ассоциативного запоминающего устройства и одновременно становится доступным схемам сравнения всех ячеек памяти блока 5 АЗУ. Код поразрядно подается на первые входы элементов Ю1И 12, на вторые входы которых поступает содержимое элементов 11 памяти. В результате поразрядное сравнение содержимого всех ячеек памяти с инверсным кодом минимального пути.

При совпадении единичных разрядов инверсного кода минимального пути и кода, хранимого в ячейке памяти, схема сравнения такой ячейки формирует на выходе единичный сигнал, который записывается в соответствующий триггер регистра 14.

Таким образом, в регистре 14 в 1 будут установлены те разряды, которые

соответстзуют ячейкам памяти, хранящих коды, накрывае1-1ые данным минимальным путем. С выходов регистра 14

записанные единицы через информационную шину 9 поступают на соответствующие входы блока 6 сумматоров, где происходит их арифметическое сложение. В следующем такте сигналом с генератора 4 тактовых импульсов вновь происходит уменьшение содержимого счетчика 2 адреса. Б блок 1 памяти выдается адрес т-1 минимального пути. Инверсньй код этого пути поступает

в блок 5 АЗУ, и вьппеописанные деистВИЯ повторяются.

Аналогичным образом происходит обработка кодов всех остальных минимальных путей.

После подачи в блок 5 АЗУ кода последнего (минимального) пути моди- ф{1кация счетчика 2 адреса приводит к его обнулению. Код О по адресной шине 7 воздействует на входы элемен

элемента ИЛК-НЕ фop fflpyeтcя си1едал 1, регистрация которого с выхода 10 устройства свидетельствует об окончании работы устройства. Содерж1- мое на выходе блока 6 сумматоров соответствует количеству работоспособных состояний N объекта при К исправных элементах.

N

.р

N,

На Основе информации, полученной в результате работы устройства, можно рассчитать следующие показатели:

общее число работоспособных состояний;

степень гибкости системы (показатель совершенства структуры), равную

NP

N.

gg 40 45

, где NO

функцию р надежности извольной структуры при CQ вероятности Р исправной ментов по формуле

п SlN

Кг1

Pj (l-Pj) . рмула изобретения

счетчик адреса и блок памяти, выход генератора соединен с входом счетчика адреса, выходы которого соединены с адресными входами блокр памяти, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок ассоциативного запоминающего устройства, регистр, блок сумматоров и элемент ШШ-НЕ, информационные входы блока ассоциативного запоминающего устройства подключены к информационным выходам блока памяти, входы элемента ИЛИ-НЕ соединены с выходами счетчика адреса, выход элемента ИЛИ-НЕ и выходы блока сумматоров подключены соответственно к управляющему и информационным выходам устройства, информационные выходы блока ассоциативного запоминающего устройства соеди11ены поразрядно с установочными входами триггеров регистра, выходы которого подключены к входам блока сумматоров причем блок ассоциативного запоминаю щего устройства состоит из ячеек по числу состояний объекта, каждая из

которых содержит группу элементов ИЛИ, группу элементов памяти и элемент И, число элементов в группах .равно числу элементов объекта в ячейке, выходы элементов памяти группы соединены с первьми входами одноименных элементов ИЛИ группы, вторые входы и выходы которых соединены соот- .ветственно с одноименными разрядами информационных входов блока и входам элемента И ячейки, выходы которых подключены к соответствующим разрядам информационных выходов блока.

фи8.

| Устройство для определения показателей надежности объектов | 1981 |

|

SU1072058A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Устройство для определения надежности объектов | 1977 |

|

SU708359A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1987-02-23—Подача