11

И

:

4

О

со а

Л.7

1U

Изобретение относится к цифровой вычислительной технике, в частности к электронике, и может быть использовано в полупроводниковых запоминающих устройствах с произвольной выборкой.

Целью изобретения является повьппе- ние надежности запоминающего устройства.

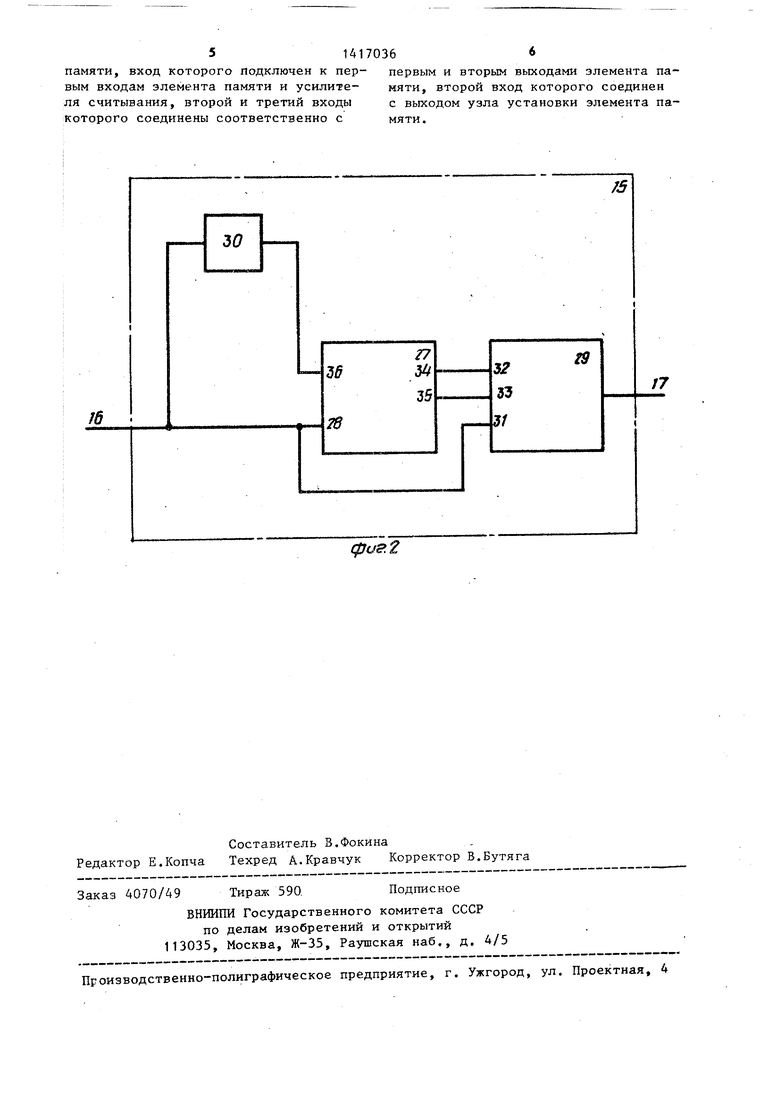

На фиг. 1 изображена структурная схема запоминающего устройства; на фиг, 2 - структурная схема блока контроля.

Запоминающее устройство содержит матрицу t элементов памяти (ЭП), состоящую из ЭП 2, объединенных словар- ными 3 и разрядными 4 шинами, дешифраторы строк 5 и столбцов 6, входы 7 которых являются адресными входами устройства, усилители 8 записи-счи- тьшания, первый вход - выход 9 которых является входом/выходом устрой- Ьтва, блок 10 синхронизации и блок 11 задания режима, основные 12 и дополнительный 13 формирователи импульсов выборки (ФИВ), шину 14 опорного напряжения, блок 15 контроля, вход 16 и выход 17 которого соединены соответственно с выходом дополнительного ФИВ 13 и входом блока 11 задания режима. Первый 18 и второй 19 выходы блока 10 синхронизации подключень) к первому входу .20 дополнительного ФИВ 13 и к второму входу 21 усилителей 8 эаписи-считьюания,третий 22 и четвертый 23 входы которых соединены соответственно с соответствующими разрядными шинами 4 и с выходами дешифратора 6 столбцов. Выходы дешифратора 5 строк и блока 11 задания режима подключены соответственно к перво- y 24 и второму 25 входам ФИВ 12, выход которых соединен с соответствующими словарными шинами 3. Шина опорного напряжения подключена к второму выходу 26 дополнительного ФИВ 13

Блок 15 контроля (фиг,. 2) содержит элемент 27 памяти, первый вход 28 которого является входом блока контроля, усилитель 29 считывания, выход которого является выходом блока контроля, узел 30 установки элемента памяти, вход которого подключен к первым входам 31 элемента 27 памяти и усилителя 29 считывания, второй 32 и третий 33 входы которого соединены соответственно с первым 34 и вторым 35 выходами элемента 27 памяти, второй вход 36 которого соединен с вьтхо

0

5

0

5

70362

дом узла 30 установки элемента памяти.. ,

Запоминающее устройство работает следующим образом.

В режиме хранения на выходе ФИВ 12 на словарных 3 и разрядных 4 шинах поддерживаются потенциалы, обеспечивающие хранение информации в ЭП 2, усилители 8 записи-считывания выключены. При обращении к ЗУ выбор требуемого ЭП 2 осуществляется включением формирователя 12 и усилителя 8, соот- .ветствующих входным адре.сам на входе 7. В режиме записи выбранный усилитель 8 формирует сигнал, соответствующий входной информации, который затем записывается в выбранный ЭП 2. В режиме считывания сигнал, формируемый на щинах 4, усиливается и поступает на выход 9 ЗУ, Адресные дешифраторы 5 строк и столбцов 6 обеспечивают включение ФИВ 12 и усилителя 8 в соответствии с входными адресными .сигналами. Блок- 10 синхронизации осуществляет синхронизацию работы блоков ЗУ, управляет работой ЗУ.

Правильная работа ЗУ при считывании зависит от параметров сигналов, вырабатываемых ФИВ 12, в первую очередь , амплитуды. В определенных усло ВИЯХ, например, при отклонении напряжения источника питания от номинального значения, возможна неправильная работа ЗУ (например, ложное считывание) . В таких случаях блок 15 контроля, на вход которого поступает сигнал с выхода ФИВ 13, и блок 11 задания режима таким образом регулируют работу ФИВ 12, что обеспечивают надежное считывание информации из ЗУ. Сигнал с первого выхода блока 10 синхронизации поступает на первый вход 20 ФИВ 13, имеющего характеристики, идентичные основным ФИВ 12, второй вход 26 ФИВ 13 подключен к. щине 14 опорного напряжения, потенциал которой определяется в зависимости от сигналов, задаваемых ФИВ 12 в нормальных условиях. В результате на выходе ФИВ 13 формируется сигнал, имеющий характеристики, аналогичные характеристикам сигналов, вырабатываемых основными ФИВ 12, если бы в ЗУ не было бы блока 15 контроля. Сигнал с выхода дополнительного ФИВ 13 поступает на вход 16 блока 15 контроля, на выходе 17 которого формируется сигнал с пара- метрами, зависящими от того, обеспе0

5

0

5

0

5

314

чивают или нет параметры сигналов выборки на выходе основного ФИВ 12 надежную работу ЗУ. В зависимости от параметров сигнала, поступающих на вход блока 11 с выхода 17 блвка 15 контроля, на выходе блока 11 формируется сигнал, меняющий параметры им- пульсов выборки и обеспечивающий надежную работу ЗУ.

Введение дополнительного ФИВ 13 и блока 15 контроля позволяет повысить надежность работы ЗУ путем уменьшения чувствительности к разбросу параметров, .отклонению напряжения источника питания от номинального значения, что также расширяет допустимый диапазон изменения напряжения питания ЗУ.

Блок 15 контроля работает следующим образом.

В режиме хранения на вход 16 блока 15 подается нкзкйй логический сигнал, усилитель 29 считывания отключен, узел 30 установки ЭП устанавливает элемент 27 памяти в определенное состояние, в котором наиболее вероятно ложное считывание, связанное с внутренним разбалансом параметров элементов памяти. На выходе 17 блока 15 поддерживается сигнал с низким логическим уровнем. В режиме считывания, на вход 16 блока 15 поступает с блока 10 синхронизации сигнал, имеюпщй высокий логический уровень, который подключает ЭП 27 к усилителю 29 считывания, который включается, и одно- временно выключается узел 30 установки ЭП. В результате на выходе 17 блока 15 формируется сигнал считывания, параметры которого зависят от того, произошло или нет ложное считывание. Параметры входного сигнала, поступающего на вход 16 блока 15, элемента 27 памяти, усилителя 29 считывания отслеживают характеристики сигналов и параметры схем, используе- Mfccc в матрице 1 ЭП, что позволяет контролировать и повысить надежность функционирования ЗУ.

Введение блока колтроля, отслеживающего работу элементов памяти ЗУ, позволяет повысить надежность работы ЗУ при изменении контру1 тивно-схемо- технических параметров приборов.

Дополнительный ФИВ 13 может быть выполнен аналогично ФИВ 12. В качест ве дешифраторов строк 5 и столбцов 6 а также блока 10 синхронизации могут

7036

быть применены известные логические блоки.

Предлагаемое ЗУ имеет более кий диапазон изменения, напряжения источника питания и температуры, что связано с уменьшением чувствительности в ЗУ. Введение дополнительных бл.оков в ЗУ не приводит к ухудше Q нию быстродействия и потребляемой мощности ЗУ, существенному увеличению числа компонентов (транзисторов и т.д.) ЗУ. -.

15

Формула изобретения

1.Запоминающее устройство, содержащее матрицу элементов памяти, дешифраторы строк и столбцов, входы

Q которых являются адресными входами устройства, усилители .записи-считывания, первые входы-выходы которых объединены и являются информационным входом-выходом устройства, блок син5 хронизации, блок задания режима, формирователи импульсов выборки, первый и второй входы которых подключены соответственно к выходам дешифраторов строк и выходу блока задания режима,

0 второй выход блока синхронизации подключен к вторым входам усилителей- записи-считывания,, третьи и четвертые входы которых соединены соотйет- ственно с соответствующими разрядными пинами матрицы элементов памяти и выходами дешифратора столбцов, выходы формирователей импульсов выборки подключены к соответствующим словарным шинам матрицы элементов памяти, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнитель- ньш формирователь импульсов выборки .и блок контроля, вход и выход которого подключены соответственно к выходу дополнительного формирователя импульсов выборки и входу блока задания режима, первый вход дополнительного формирователя импульс ов выборки подключен к шин е опорного напряжения устройства, второй вход - к первому входу блока синхронизации.

2.Устройство по п. 1, о т л и- чающееся тем, что блок контроля содержит элемент памяти, первый вход которого является входом блока контроля, усилитель считывания, выход которого,является выходом блока контроля, узел установки элемента

5

0

514170366

памяти, вход которого подключен к пер- первым и вторым выходами элемента па- вым входам элемента памяти и усилн-не- мяти, второй вход которого соединен ля считывания, второй и третий входы с выходом узла установки элемента па- которого соединены соответственно с мяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Устройство для считывания информации из динамической памяти | 1980 |

|

SU982082A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

Изобретение относится к цифровой вычислительной технике, в частности к электронике, и может быть использовано в полупроводниковых запоминающих устройствах с произвольной выборкой. Запоминающее устройство содержит матрицу 1 элементов памяти, состоящую из элементов L памяти, объединенных словарными 3 и разрядными 4 шинами, дешифраторы строк 5 и столбцов 6, блок 10 синхронизации, блок 11 задания режима, усилители записи-считывания 8, основные 12 и дополнительный 13 формирователи импульсов выборки, шину 14 опорного напряжения, блок 15 контроля. Запоминающее устройство имеет широкий диапазон изменения напряжения источника питания и температуры, что связано с уменьшением чувствительности в запоминающем устройстве. Введение блока контроля и дополнительного формирователя импульсов выборки позволяет повысить надежность работы устройства при изменении конструктивно-схематических параметров приборов. 1 з.п. ф-лы, 2 ил. с (Л

36

J6

28

32

33

19

17

фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| IEEE Journal of Solid State Circuits,v.SC-20,1985,№ 5,p.929-934 | |||

Авторы

Даты

1988-08-15—Публикация

1986-05-05—Подача