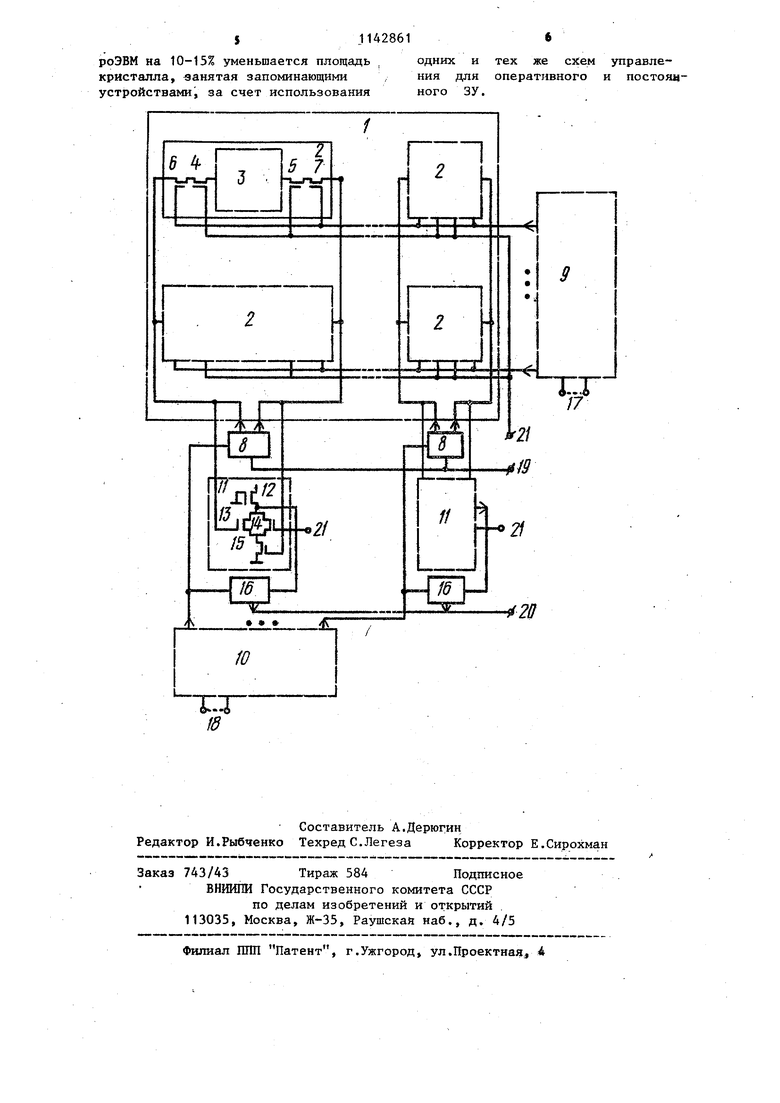

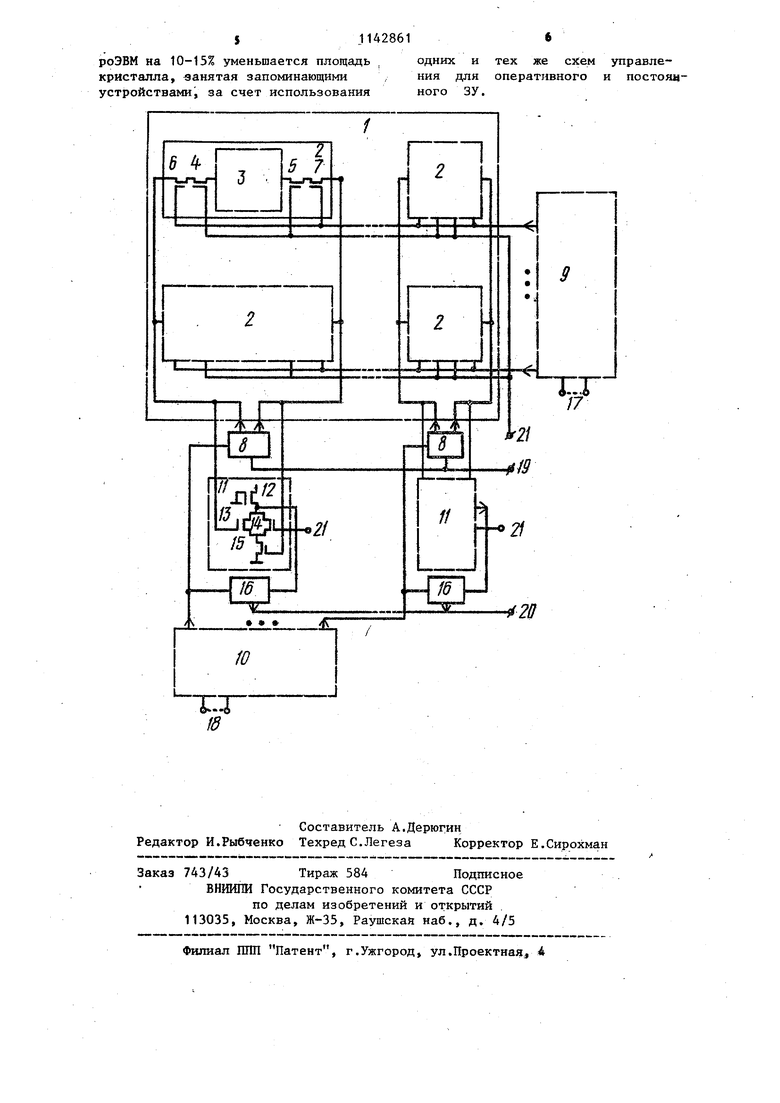

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, И может быть использовано при построении микроЭВ имеющих в своем составе оперативное и постоянное запоминающее устройств Известно полупроводниковое запом нающее устройство (ЗУ), содержащее микросхемы оперативного и постоянно го ЗУ, каждая из которых содержит накопитель и схемы управления: дешифраторы строк и столбцов и устройство считывания ll. Недостатком такого ЗУ является аппаратная избыточность схем управления и отдельных элементов накопителя . Наиболее близким к предлагаемому является оперативное запоминающее устройство, содержащее накопитель для хранения оперативной информации дешифраторы строк и столбцов, блоки записи и считывания. 2j . Недостатком устройства является невозможность использованияего для хранения постоянной информации, что ограничивает область применения ЗУ. Цель изобретения - расширение области применения ЗУ за счет совме щения функций оперативного и постоявного запоминающих устройств и обе печения возможности одновременного хранения независимых оперативной и постоянной информации в каждом элементе памяти. : Поставленная цель достигается тем, что в полупроводниковое запоми нающее устройство, содержащее матри цу элементов памяти, каждый из кото рых состоит из статического триггер и двух управляющих элементов, выпол ненньрс на транзисторах, дешифратор строк, дешифратор столбцов, усилите ли записи, ключевые усилители, причем затворы транзисторов управляющих элементов каждой строки соединены с выходами дешифратора строк, входы которого являются одними адре йыми входами устройства, стоки первого и второго транзисторов управ:ляющих элементов каждого столбца соединены с выходами соответствующего усилителя записи, вход которого является информационным входом устройства, а управляющий вход соед нен с соответствующим выходом дешифратора столбцов, входы которого ЯВ ляются другими адресными входами устройства, управляющие входы ключевых усилителей соединены с соответствующими выходами дешифратора столбцов, а выходы являются информационным выходом устройства, введены логические элементы и в каждый элемент памяти - два элемента связи, выполненных на транзисторах, причем стоки первого и второго транзисторов элементов связи соединены с истоками транзисторов соответствующих управляющих элементов, истоки - с соответствующими входами статического триггера, а затворы являются дополнительным входом устройства, входы каждого логического элемента соединены с выходами соответствующего усилителя записи, управляющий вход с дополнительным входом устройства,. а выход - с входом соответствующего ключевого усилителя. При этом каждый логический элемент содержит нагрузочный транзистор р-типа и три ключевых транзистора п-типа, причем сток нагрузочного транзистора р-типа соединен с шиной питающего напряжения, исток является выходом логического элемента и соединен со стоками первого и второго ключевых транзисторов п-типа, истоки которых соединены со стоком третьего ключевого транзистора п-тит па, исток которого и затвор нагрузочного транзистора р-типа соединены с шиной нулевого потенциала, затвор первого ключевого транзистора п-типа является управляющим входом, а затворы второго и третьего ключевых транзисторов п-типа - входами логического элемента. 1 На чертеже изображена схема одного разряда предлагаемого запоминающего устройства. Запоминающее устройство содержит матрицу 1 элементов памяти (ЭП) 2, состоящих из статического триггера 3, первого и второго элементов связи, выполненных на транзисторах 4 и 5, первого и второго управляющих транзисторов 6 и 7, усилители 8 записи, дешифратор 9 строк, дешифратор 10 столбцов, логический элемент 11, нагрузочный транзистор 12 логического элемента, первьй, второй и третий ключевые транзисторы 13, 14 и 15 логического элемента, ключепой усилитель 16, одни и другие адресные входы 17 и 18, информационный вход 19, информационный выход 20, дополнительный управляющий вход 21. Устройство работает в четьфех режимах: запись, считьгеание оперативной информации, считывание посто явной информации, хранение информации. Оперативная информация хранится в статическом триггере 3 ЭП. Хранение оперативной информации обе печивается устойчивостью состояния триггера 3 при поступлении на него напряжения питания. Постоянная информация определяется первым и вторым дополнительными транзисторами 4 и 5 ЭП 2. Программирование достигается размыканием на стадии изготовления устройства заранее предусмотренных проводящих перемычек, связывающих сток - исток этих транзисторов. Занесение в ЭП 2 единицы (нуля информации соответствует наличию (отсутствию) проводящих перемычек между стоком и истоком первого и вт рого дополнительных транзисторов 4 и 5 ЭП 2. Таким образом, и оператив ная, и постоянная информации хранят ся на одном и том же ЭП 2 независимо друг от друга. При обращении к оперативной информации на дополнительный управляющий вход 21 устройства подается сигнал 1, а при обращении к постоянной информации сигнал О. В режиме записи оперативной информации на информационный вход 19 и адресные входы 17 и 18 подается код числа и код адреса ЭП 2, в кото рый она должна быть записана. Код адреса поступает в дешифратор 9 строк и дешифратор 10 столбцов, происходит выборка строки и столбца в матрице ЭП, при этом упра ляющие транзисторы 6 и 7 ЭП 2 откры ты сигналом 1 на их затворах. В зависимости от парафазного сигнал на выходе усилителя 8 записи на пря мой и инверсной шинах выбранного, столбца устанавливаются парафазные :логические сигналы. Транзисторы 4 и 5 ЭП 2 открыты сигналом 1 на до полнительном управляющем входе 21. .Триггер 3 ЭП 2 принимает состояние, ,соответствующее значению информации на входе 19. В режиме считывания оперативной информации состояние шин столбцов . определяете состоянием выбранного ЭП 2, когда открыты управляющие тран зисторы 6 и 7 и транзисторы 4 и 5. Второй ключевой транзистор 14 логического элемента 11 открыт сигналом 1 на входе 21. На выходе логического элемента устанавливается инверсия напряжения на инверсной шине столбца, и через ключевой усили : тель 16 выбранного столбца она поступает на информационный выход устройства ,20. В режиме считывания постоянной информации первый и второй транзисторы 4 и 5 ЭП .2 закрыты сигналом 0 на дополнительном управляющем входе 21. Состояние прямой и инверсной шин выбранного столбца и соответственно сигналов на затворах первого и третьего ключевых транзисторов 13 и 15 логического элемента 11 определяется отсутствием или наличием перемычек . При наличии перемычек на шинах столбца в момент выборки устанавливается парафазная информация, при отсутствии перемычек состояние шин столбцов и сигналы на затворах первого и третьего активных транзисторов 13 и 15 равны высоким потенциалам, определяемым усилителями 8 записи, второй ключевой транзистор закрыт сигналом О на входе 21. При парафазной:, информации на затворах первого и третьего ключевых транзисторов 13 и 15 логического элемента 11 на его выходе образуется сигнал 1, а при равных высоких потенциалах - сигнал О, которьй через ключевой усилитель выбранного столбца поступают на информационньй выход 20. I В предлагаемом устройстве для выполнения функций хранения как оперативной, так и постоянной информации используются одни и те же элементы памяти. При этом оперативная и постоянная информации не зависят друг от друга. Это расширяет область применения устройства, поскольку одно и то же устройство с общими схемами управления (выполненное, наример, в виде единой микросхемы) ожет быть использовано для хранения постоянной, и оперативной информаии. При использовании предлагаемого устройства в однокристалльной микроЭВМ на 10-15% уменьшается площадь кристалла, занятая запоминающими устройствами, за счет использования

одних и тех же схем управления для оперативного и постоянного ЗУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2047919C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

1. ПОЛУПРОВОДНЖОВОЕ ЗАПОМИНАКШЩЕ УСТРОЙСТВО, содержащее матрицу элементов памяти, каждый из которых состоит из статического триггера и двух управляющих элементов, выполненных на транзисторах, дешифратор строк, дешифратор столбцов, усилители записи, ключевые усили ели, причем затворы транзисторов управляющих элементов каждой строки соединены с выходами дешифратора строк, входы которого являются одними адресными входами устройства, стоки первого и второго транзисторов управляющих элементов каждого столбца соединены с выходами соответствующего усилителя записи, вход которого является информационным входом устройства, а управляющий вход соединен с соответствующим выходом дешифратора столбцов, входы которого являются другими адресными входами устройства, управляющие входы ключевых усилителей соединены с соответствующими выходами дешифратора столбцов, а выходы являются информационным выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет совмещения функций оперативного и постоянного запоминаюш:их устройств, в него введены логические элементы и в каждый элемент памяти - два элемента связи, вьтолненных на транзисторах, причем стоки первого и второго транзисторов элементов связи соединены с истоками транзисторов соответствующих управляющих элементов, истоки с соответствующими входами статического триггера, а затворы являются дополнительным входом устройства, входы каждого логического элемента соединены с выxoдa ш соответствующего усилителя записи, управляющий Л вход - с дополнительным входом устройства, а выход - с входом соответствующего ключевого усилителя. 2. Устройство по п. 1, о т л ичающееся тем, что логический элемент содержит нагрузочньш транзистор р-типа и три ключевых транзистора п-типа, причем сток нагрузочного транзистора р-типа соединен с шиной питающего напряжения, истох является выходом логического элемента и соединен со стоками первого и второго ключевых транзисторов , Г)-типа, истоки которых соединены со стоком третьего ключевого транзистора п-типа, исток которого и затвор нагрузочного транзистора р-типа соединены с шиной нулевого потенциала, затвор первого ключевого транзистора п-типа является управляющим входом, а затворы второго и третьего ключевых .транзисторов и-типа - входами логического элемента.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Под ред | |||

| В.М.Пролейко | |||

| М., Советское радио, 1980, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Горн Л.С., Хазанов Б.И | |||

| Элементы микромощньпс цифровых устройств | |||

| М., Атомиздат, 1980, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1985-02-28—Публикация

1983-04-12—Подача