(54 ) УСТРОЙСТВО для СЧИТЫВАНИЯ ИНФОРМАЦИИ из ДИНАМИЧЕСКОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Запоминающее устройство | 1986 |

|

SU1417036A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

Изобретение относится к мик(5оэлектронике, а именно к устро 1ствам для считывания информации из динамиг ческойпамяти, и может быть применен при создании интегральных полупровод никовых динамических оперативных запоминающих устройств на основе МПД однотранзисторных элементов памяти. Известно устройство для считывани информации, содержащее матрицу статических элементов памяти, усилители считывания, дешифратор и блок управления t 1 J. Недостатками такого устройства являются большая за.нимаемая элементами памяти площадь, большая потребляемая мощность. Наиболее близким к предлагаемому является устройство для считывания информации из динамической памяти на основе МПД однотранзисторных элемен тов памяти, содержащее формиров атели,дешифратор, ключи, схему включения стооки. схему синхронизации. При работе устройства с выхода блока управления последовательно подаются два управляющих сигналас задерхчкой второго относительно первого,равной, как минимум, задержке распространения сигнала по словарной шине, поскольку меньшая Ёеличина задержки приводит к ложному срабатыванию устройства. Первый управляющий сигнал поступает с выхода схемы включения строки,второй - с выхода схемы включения усилителей считывания, задержка второго сигнала относительно первого обеспечивается схемой синхронизации. При этом увеличение задержки между управляющими сигналами увеличивает надежность работы устройства, но ухудшает его быстродействие. Уменьшение задержки между сигналами увеличивает быстродействие устройства, но при этом увеличивается и вероятность его ложного срабатывания Г 2. Недостатком данного устройства является невозможность одновременного повышения надежности считывания и быстродействия.

Цель изобретения - повышение быстродействия .ус тройства.

Поставленная цель достигается тен что устройство для считывания информмации из динамической памяти, содержащее первый формирователь,выход которого соединен с первыми входами ключей, вторые входы которых соединеныс выходами соответствующего дешифра|ТОра, а выходы ключей являются выходами устройства, второй формирователь, выход которого соединен с управляющим входом блока усилителей считывания, входы которых являются числовыми входаМи устройства, входы второго формирователя соединены с выходами соответствующих ключей.

Таким образом, достижение поставленной цели обеспечивается подключением входов схемы включения усилителей считывания к вторым концам словарных шин опорных элементов.Такое подключение автоматически делает задержку включения схемы включения усилителей считывания равной i времени распространения сигнала по словарной шине.

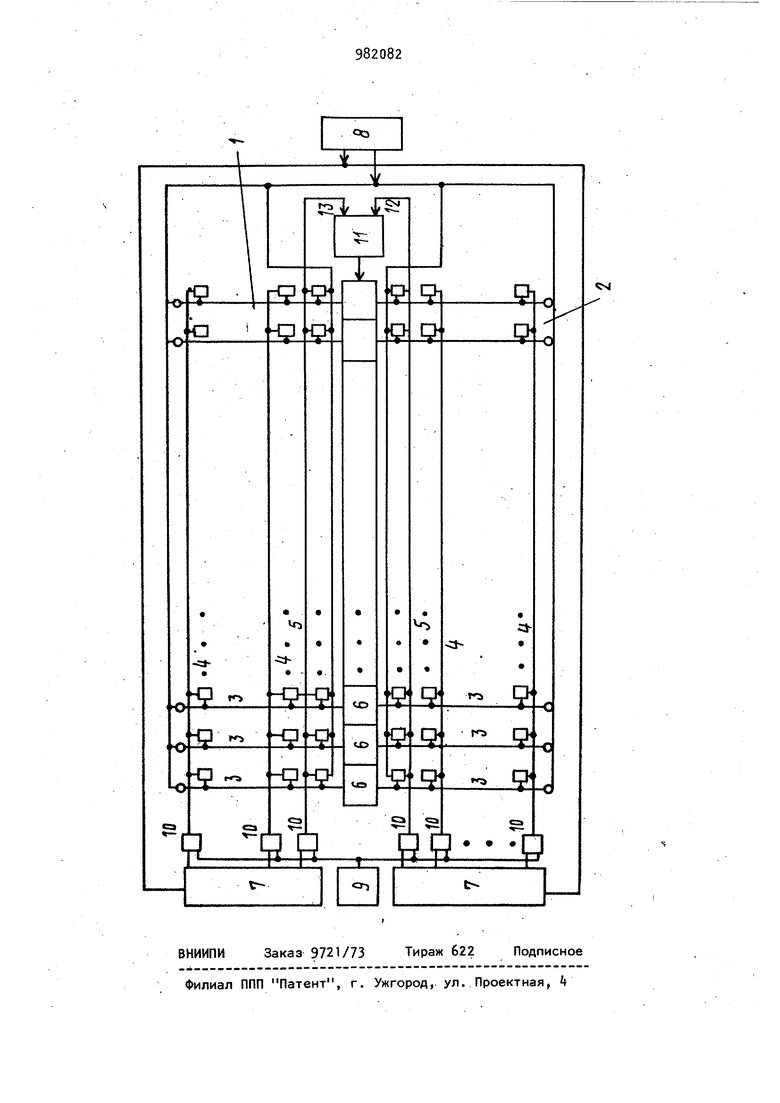

На чертеже изображена структурная схема устройства.

Устройство содержит полуматрицы 1 -И 2 однотранзисторных элементов памяти, соединенных по столбцам разрядными шинами 3 и ПО строкам - c/ioварными шинами А. В каждой полуматрице имеется ряд опорных элементов памяти, соединенных по строкам словарными шинами 5 и подключенных по одному к каждой азрядной шине. Устроиство содержит блок 6 усилителей считывания,к сигнальным входам каждого из которых подключены соответствующие разрядные шины первой и второй полуматриц, дешифратор 7 строк, блок В предзаряда, выходы которого соединены с входами предзаряда дешифратора, разрядных шин и опорных элементов, первый формирователь 9 включения стро ки, выход которого через ключи 10 сое динен со всеми первыми концами словарных шин, второй формирователь 11 включения усилителей считывания,, имеющий два входа. Первый вход 12 формирователя включения усилителей считывания соединен с вторым концом одной из словарных шин опорных элементов а вто рой вход 13 - с вторым концом другой.

словарной шины опорных элементов., а выход соединен свходами управления усилителей считывания.

Перед началом считывания устройство выводится в исходное состояние. При этом включен блок предзаряда, и через входы предзаряда разрядные шины заряжаются до одинакового уровня напряжения, в опорных элементах устанавлисается опорный уровень напряжения, и ключи дешифратора строк приводятся в открытое состояние. После этого блок предзаряда выключается включается дешифратор строк, и все ключи дешифратора строк, кроме двух, переводятся в закрытое состояние. При этом через один из открытых ключей выход формирователя включения строк подключен к соответствующей словарной шине элементов памяти, находящейся в одной из полуматриц а через другой открытый ключ выход формирователя включения строк подключен к словарной шине опорных элементов, находящихся во второй полуматрице. После этого включается формирователь включения строки , и с его выхода через открытые ключи дешифратора строк сигнал начинает распространяться по соответствующим с ловарным шинам элементов памяти и топорных элементов.По мере распространения сигнала по словарным шинам к одному из выходов каждого из усилителей считывания подключаются элементы памяти, находящиеся в одной полуматрице, к другому входу - опорные элементы, находящиеся,в другой полуматрице, а в результате на входах усилителей считывания устанавливается дифференциальный сигнал, соответствующий хранимой в элементе памяти информации. После тогЬ, как сигнал достигнет второго конца выключаемой словарной шины опорных элементов, он поступает на один из входов и включает формирователь включения усилителей считывания, по сигналу с которого усилители считывания усиливают ин формацию на их сигнальных входах. Поскольку при выборе словарной шины элментов памяти, одновременно выбирается из двух словарных шин опорных элементов, формирователь включения усилителей считывания всегда окзываегся включенным либо по одному,либо по другому входу.

По истечении необходимого времени выдержки формирователь включения

строки, формирователь включения усилителей считывания и дешифратор стро выключаются, и включается блок предзаряда, по сигналам с которого все разрядные шины заряжаются до одинакового yjpOBH напряжения, в опорных элементах устанавливется опорный уровень напряжения, и все ключи дешифратора строк переводятся в открытое состояние,

Устройство готово к началу следующего цикла считывания.

Надежность работы устройства считывания определяется вероятностью выполнения условия: задержка включения формирователя считывания не меньше задержки сигнала по словарной шиКе. В случае прототипа из-за технологического разброса параметров компонентов вероятность нарушения этого условия всегда существует.

Предлагаемый вариант устройства обеспечивает автоматическое выполнение этого УСЛОВИЯ, поскольку усилители считывания не могут быть вклю мены до тех пор, пока сигнал не достигнет вторых концов словарных шин.В случае прототипа в величину задержки включения усилителей считывания необходимо вводить запас, обеспечивающий нормальную работу устройства в некотором диапазоне разброса технологических параметров, что ухудшает его быстродействие. Предлагаемый вариант устройства не

требует введения этого запаса и обеспечивает, таким образом, максимальное быстродействие, поскольку включение усилителей считывания осу щесталяется без дополнительной задержки в момент достижения сигналом вторых концов словарных шин.

Формула изобретения

Устройство для считывания информации из динамической памяти, содержащее .первый формирователь, выход которого соединен с первыми входами ключей, вторые входы которых соединены с выходами соответствующего дешифратора, а выходы ключей являются выходами устройства, второй формирователь, выход которого соединен с управляющим- входом блока усилителей считывания, входы которых являются числовыми входами устройства, о тличающееся тем, что, с целью повышения бытсродействия устройства, входы второго формирователя соединены с выходами соответствукяцих. ключей.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-12-15—Публикация

1980-09-29—Подача