Изобретение относится к вычислительной технике, а именно к высокопроизводительным вычислительным устройствам для мультипрограммной обработки информации.

Основной функцией устройств для мультипрограммной обработки информации является обеспечение мультипрограммного режима работы. В мультипрограммном режиме функционирования квазипараллельно выполняется некоторое множество процессов. Все эти процессы считаются запущенными на выполнение, одновременно и независимо друг от друга выполняющимися. Каждый процесс выполняется по своей программе, работающей над совокупностью элементов памяти, составляющих вектор состояния процесса. Функционирование процесса состоит в выполнении этой программы, каждый шаг которой изменяет содержание вектора состояния процесса. Поскольку представление о процессоре, на котором выполняется процесс, заложено в семантику команд, составляющих программу, можно считать, что совокупность программы и вектора состояния процесса (образ процесса) полностью его определяет. Каждый процесс функционирует в среде образа независимо от наличия или отсутствия других процессов. В однопроцессорной ЭВМ (или однопроцессорном модуле мультипроцессорной системы) мультипрограммный режим состоит в квазипараллельном, попеременном выполнении процессов: кажМ

Ч ч

IV4

дый процесс на некоторое время занимает разделяемые всеми процессами ресурсы процессора, выполняется (обычно не до полного завершения) некоторое время, затем его выполнение приостанавливается (образ процесса замирает в том состоянии, в котором оказался в момент приостановки процесса), ресурсы процессора предоставляются следующему процессу и т.д. Приостановленные процессы вновь ставятся в очередь процессов, ожидающих возможности занять ресурс процессора. Часть образа процесса (образ процесса в процессоре) соответствует состоянию программно-доступных процессу элементов памяти внутри процессора. В архитектуре современных ЭВМ одни и те же внутренние элементы памяти процессора независимо используются программами различных процессов. Следовательно, когда происходит переключение процессов, состояние этих элементов памяти для снимаемого процесса должно быть сохранено, а для включаемого в работу процесса восстановлено прежнее состояние этих элементов памяти для данного процесса, сохраненного ранее. Далее по тексту под образом процесса будет иметься в виду образ процесса в процес- соре. Во многих существующих вычислительных системах используются те или иные средства поддержки взаимодействия квазипараллельных процессов. Для однопроцессорных традиционных архитектур для поддержки взаимодействия и переключения процессов используются чисто программные средства, не поддержанные архитектурой (системой команд) центрального процессора.

Известна вычислительная система i PSC/2, содержащая до 128 процессорных узлов, связанных друг с другом системой связи с топологией ГИПЕРКУБ. Каждый процессорный узел содержит центральный процессор80386, сопроцессор для обработки чисел с плавающей точкой 80387, локальную память объемом 1-16 Мбайт и маршрутизатор прямых сообщений. Для обеспечения взаимодействия процессов, расположенных в разных узлах, и переключения процессов в одном узле, в каждом из узлов размещается часть операционной системы (ОС)- ядро узловой OC-MBOS. MBOS и сам узловой процессор 80386 обеспечивают координацию графика входящих и исходящих из узла сообщений, управляют планированием и выполнением процессов пользователя. Аппаратно поддержаны с помощью маршрутизатора функции по обмену сообщениями, а поддержка планирования и переключения процессов осуществляется

чисто программно узловой ОС, т.е. определенная часть полезного времени занята сохранением образов предыдущих процессов и подготовкой образов новых процессов,

что снижает быстродействие системы в целом.

Известна вычислительная система NCUBE (ten). Переключение и взаимодействие процессов здесь также обеспечивается

0 программными средствами узловой операционной системы, однако эти программные средства опираются на ряд специальных команд, введенных в набор команд узлового процессора специально для поддержки

5 квазипараллельных процессов. Эти команды обеспечивают управление взаимодействием и переключением процессов. Поскольку такая поддержка также является программной, существуют определенные

0 временные затраты на сохранение образа предыдущего процесса и подготовку к работе образа следующего процесса, что снижает быстродействие системы в целом.

Известно устройство Т800, которое яв5 ляется функционально законченным компьютером, реализованным на одном кристалле (транспьютер). В состав транспьютера входят быстрая внутрикристальная память с минимальным числом

0 регистров, а также микропрограммный диспетчер, обеспечивающий выполнение на одном транспьютере ряда процессов, разделяющее процессорное время. Наличие диспетчера исключает необходимость

5 создания программного ядра диспетчиро- аания процессов. Активные процессы содержатся в списке, который является связанным списком указателей на рабочие области процессов, выделенные в памяти.

0 Активный процесс выполняется до тех пор, пока это возможно, затем процесс приостанавливается, а из списка запускается на вы- полнение следующий процесс. Переключение с процесса на процесс заии5 мает меньше времени, чем в предыдущих устройства, так как число регистров невелико (всего 6). Недостатком устройства является, во-первых, то, что образы процессов помещены в фиксированный объем памяти,

0 что ограничивает число обрабатываемых процессов, а перезагрузка образов процессов из общей памяти требует больших временных затрат; во-вторых, сохранение содержимого регистров (хотя и малого чис5 ла) и загрузка в них необходимой информации также требуют временных затрат, что снижает быстродействие устройства в целом.

Наиболее близким к изобретению по технической сущности является вычислительное устройство, содержащее блок буферной памяти, арифметико-логический блок, шинный формирователь, дешифратор, причем первый вход блока буферной памяти является входом адреса устройства, вход синхронизации устройства соединен с входом синхронизации блока буферной памяти и с входом синхронизации арифметико-логического блока, второй вход блока буферной памяти соединен с вторым информационным выходом арифметико-логического блока, третий вход блока буферной памяти соединен с третьим входом кода операций арифметико-логического блока и с третьим выходом дешифратора, выход блока регистров соединен с вторым информационным входом арифметико-логического блока, первый и второй входы кода операций которого соединены соответственно с первым и вторым выходами дешифратора, вход которого соединен с вторым входом кода операций устройства, первый вход кода операций которого соединен с входом режима арифметико-логического блока, первый информационный вход которого соединен с входом данных устройства, вход/выход режима которого соединен с входом/выходом сдвига арифметико-логического блока, выход состояния которого соединен с выходом вектора состояния устройства, вход режима которого соединен с управляющим входом шинного формирователя, информационный вход которого соединен с первым информационным выходом арифметико-логического блока, выход шинного формирователя соединен с выходом данных устройства,

В данном устройстве работа в мультипрограммном режиме осуществляется за счет переключения с процесса на процесс программными средствами. При этом программно осуществляется пересылка в некоторое место основной памяти содержимого регистров снимаемого с обработки процесса и пересылка из основной памяти в регистры процессора образа процесса, на который производится переключение. Во время переключения процессов процессор занят пересылками образов процессов, что сокращает время эффективного использования процессора. Время, затраченное на переключение образов (по сути - потерянное) пропорционально удвоенному объему образа процесса (равному числу рабочих регистров) и времени доступа к памяти. Частое переключение с процесса на процесс приводит к серьезному снижению производительности вычислительной системы, работающей в мультипрограммном режиме.

Целью изобретения увеличение быстродействия вычислительной системы в мультипрограммном режиме.

Поставленная цель достигается тем, что

в мультипрограммное вычислительное устройство, содержащее блок буферной памяти, арифметико-логический блок и первый шинный формирователь, причем вход синхронизации устройства подключен к входу синхронизации блока буферной памяти и входу синхронизации арифметико-логического блока, вход-выход признака сдвига, выход состояния, первый информационный

выход, вход режима и первый информационный вход которого подключены соответственно к входу-выходу режима устройства, выходу вектора состояния устройства, информационному входу первого шинного

формирователя, первому входу кода операции устройства и первому информационному входу устройства, первый вход режима устройства подключен к управляющему входу первого шинного формирователя, выход

которого подключен к первому выходу данных устройства, введены второй и третий шинные формирователи, блок регистров, дешифратор, мультиплексор, блок памяти, блок формирования признаков текущих

процессов в мультипроцессорной системе и блок управления, при этом второй информационный вход устройства подключен к первому информационному входу блока памяти, третий информационный вход устройства подключен к первому входу выборки блока регистров и первому информационному входу мультиплексора, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему информационным входам блока буферной памяти, первый выход которого подключен к информационному входу второго шинного формирователя и первому информационному входу третьего шинного

формирователя, четвертый информационный вход устройства подключен к первому адресному входу блока памяти, первый выход которого подключен к информационному входу блока формирования признаков

текущих процессов в мультипроцессорной системе, второму информационному входу мультиплексора и первому информационному входу блока регистров, второй выход блока памяти подключен к второму выходу

данных устройства, вход выборки, вход чтения/записи и второй вход режима которого подключены соответственно к первому входу выборки, первому входу чтения/записи и входу режима блока памяти, второй адресный вход которого подключен к выходу блока формирования признаков текущих процессов в мультипроцессорной.системе, вход начальной установки устройства подключен к входам начальной установки блока управления и блока формирования призна- ков текущих процессов в мультипроцессорной системе, вход синхронизации устройства подключен к второму входу выборки блока памяти, входу синхронизации блока регистров и входу синхронизации блока управления, первый, второй и третий выходы которого подключены соответственно к второму входу чтения/записи блока памяти, первому управляющему входу блока формирования признаков текущих про- цессов в мультипроцессорной системе и выходу признака готовности результата устройства, второй вход кода операции которого подключен к информационному входу дешифратора, первый, второй и третий вы- ходы которого подключены соответственно к первому, второму входам кода операции арифметико-логического блока и входу режима блока управления, четвертый выход дешифратора подключен к третьему входу кода операции арифметико-логического блока, третьему информационному входу мультиплексора и первому входу записи/чтения блока регистров, первый выход которого соединен с выходом второго шин- ного формирователя и подключен к второму информационному входу блока памяти, второй выход блока буферной памяти подключен к второму информационному входу третьего шинного формирователя, выход которого соединен с вторым выходом блока регистров и подключен к второму информационному входу арифметико-логического блока, второй информационный вход которого подключен к второму информационно- му входу блока регистров и четвертому информационному входу мультиплексора четвертый выход блока управления подключен к третьему адресному входу блока памяти, пятому информационному входу мультиплексора и второму входу выборки блока регистров, пятый выход блока управления подключен к второму управляющему входу блока формирования признаков текущих процессов в мультипроцессорной сие- теме, управляющему входу мультиплексора, второму входу записи/чтения блока регистров и управляющему входу второго шинного формирователя, шестой выход блока управления подключен к третьему управляющему входу блока формирования признаков текущих процессов в мультипроцессорной системе, третьему входу записи/чтения блока регистров и управляющему входу третьего шинного формирователя, седьмой выход

блока управления подключен к четвертому управляющему входу блока формирования признаков текущих процессов в мультипроцессорной системе, шестому информационному входу мультиплексора и четвертому входу записи/чтения блока регистров, вход единичного потенциала устройства подключен к входу единичного потенциала блока управления. Блок управления содержит три триггера, счетчик, три элемента И, элемент НЕ и два элемента ИЛИ, причем вход начальной установки блока управления подключен к первому входу первого элемента И и инверсному входу установки в ноль первого триггера, вход синхронизации блока управления подключен к счетному входу счетчика и первому входу первого элемента ИЛИ, выход которого подключен к входам установки в ноль второго и третьего триггеров, вход режима блока управления подключен к входу синхронизации второго триггера, выход которого подключен к первому входу второго олемента И, инверсный выход которого подключен к входу синхронизации первого триггера, второму входу первого элемента ИЛИ и информационному входу счетчика, первый информационный выход которого подключен к четвертому выходу блока управления и входу третьего эле- мента И, инверсный выход которого подключен к второму выходу блока управления и первому входу второго элемента ИЛИ, инверсный выход которого подключен к первому выходу блока управления, вход единичного потенциала которого подключен к инверсному входу установки в единицу первого три гера, информационным входам и инверсным входам установки в единицу второго и третьего триггеров, выход третьего триггера подключен к второму входу второго элемента И и третьему выходу блока управления, прямой выход первого триггера подключен к пятому выходу блока управления, инверсный выход первого триггера подключен к шестому выходу блока управления и информационному входу первого триггера второй информационный выход счетчика подключен к второму входу второго элемента ИЛИ и седьмому выходу блока управления, третий информационный выход счетчика подключен к входу элемента НЕ, выход которого подключен к второму входу первого элемента И, выход которого подключен к входу синхронизации третьего триггера Блок формирования признаков текущих процессов в мультипроцессорной системе содержит три регистра, дса элемента И и два элемента НЕ, причем первый, второй и третий управляющие входы и инфор- мационный вход блока подключены

соотвзтс . венно к входу первого элемент, НЕ, входу синхронизации первого регистра, входу синхронизации второго регистра и информационному входу третьего регистра, выход которого подключен к информационным входам первого и второго регистров, выходы которых объединены по схеме МОНТАЖНОЕ ИЛИ и подключены к выходу блока, четвертый управляющий вход которого подключен к входу второго элемента НЕ и первому входу первого элемента И, инверсный выход которого подключен к входу записи/считывания третьего регистра, выход первого элемента НЕ подключен к второму входу первого элемента И и первому входу второго элемента И, инверсный выход которого подключен к входам записи/считывания первого и второго регистров, вход начальной установки блока подключен к входам установки в ноль первого, второго и третьего регистров, выход второго элемента НЕ подключен к второму входу второго элемента И.

В предлагаемом техническом решении увеличение быстродействия вычислительной системы в мультипрограммном режиме достигается за счет сокращения времени переключения процессов. Переход на обработку следующего процесса происходит в случае прихода в устройство команды (инструкции), содержащей код переключения процесса. После дешифрации кода устройство начинает обработку следующего процесса. Совокупность мультиплексора, блока буферной памяти, первого и второго шинных формирователей может быть названа регистровым устройством. Тогда переключения процессов заключается в смене блока регистров и регистрового устройства друг на друга, каждый из которых может быть подключен либо к арифметико- логическому блоку (в случае обработки процесса), либо к блокам, осуществляющим подготовку этого блока регистров (или регистрового устройства) к следующему процессу. Блок регистров и регистровое устройство равноправны и идентичны, работа их в двух разных режимах осуществляется параллельно, что позволяет существенно сократить время на переключение процессов. При большом количестве процессов, обрабатываемых вычислительной системой, либо при необходимости частого их переключения сокращение времени на переключение процессов приводит к повышению производительности всей вычислительной системы.

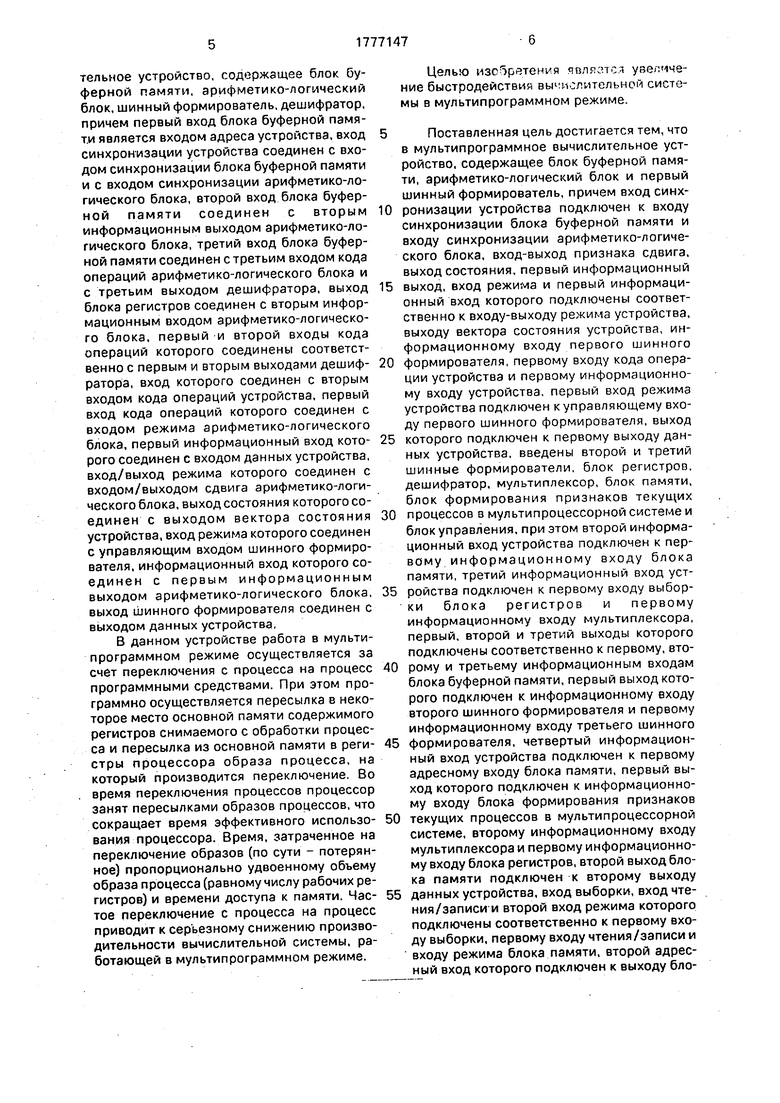

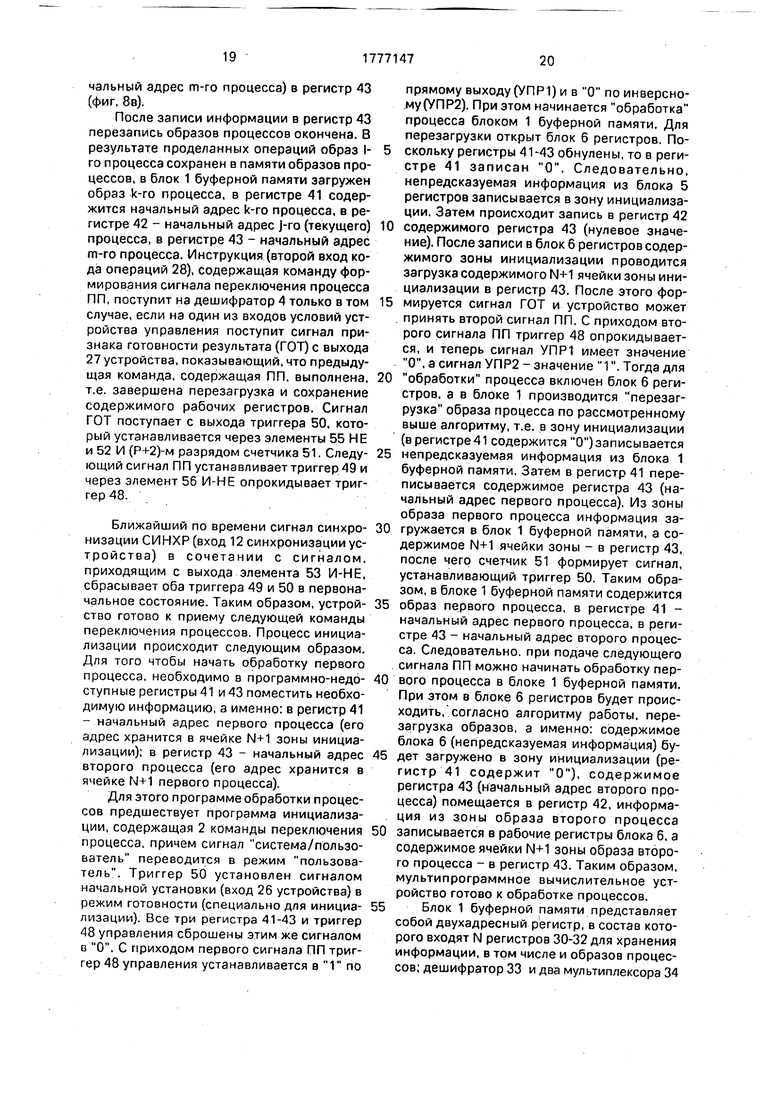

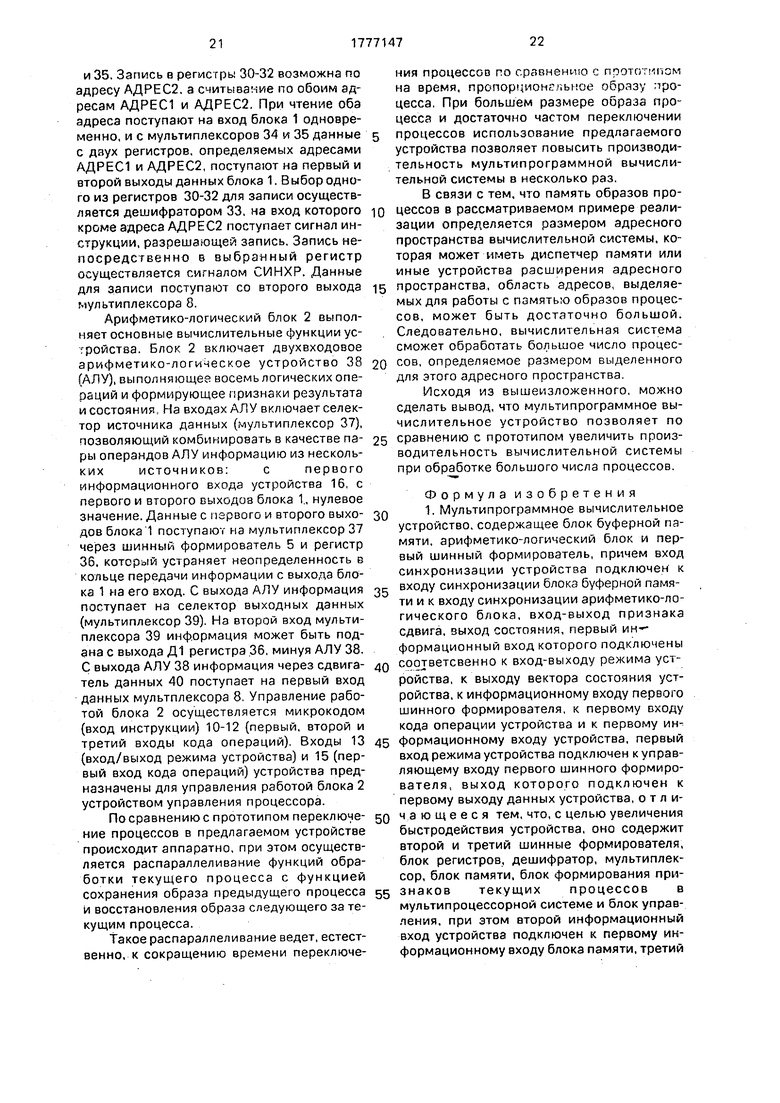

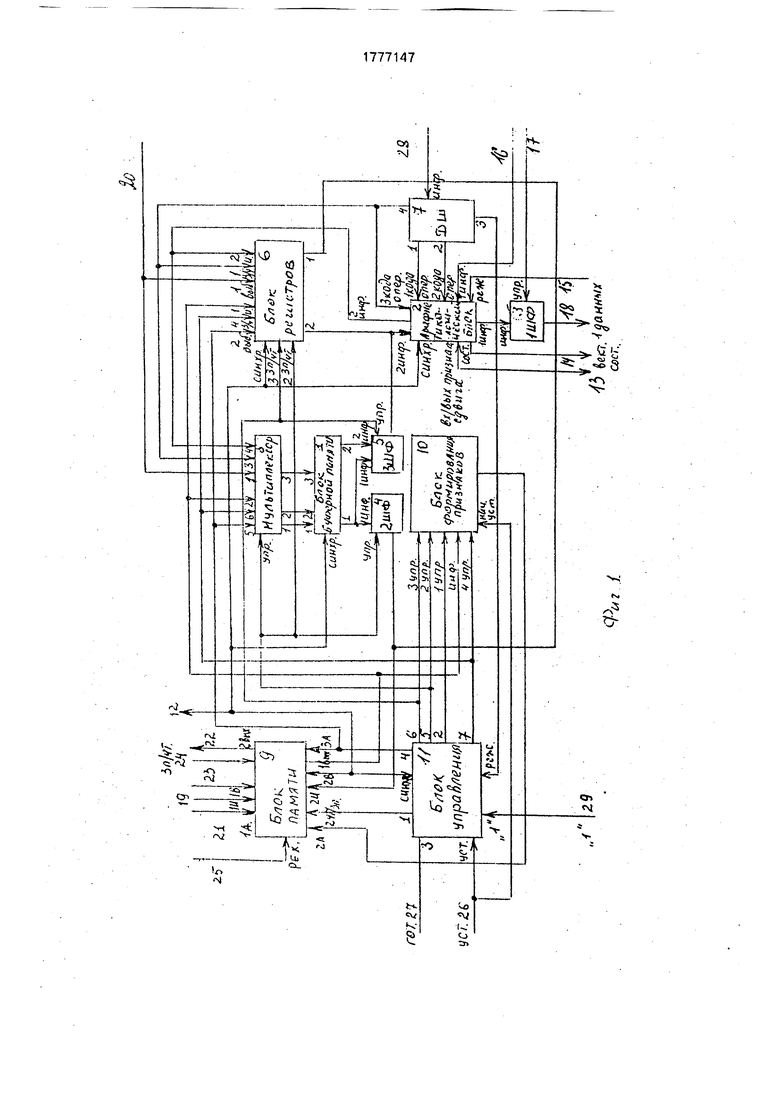

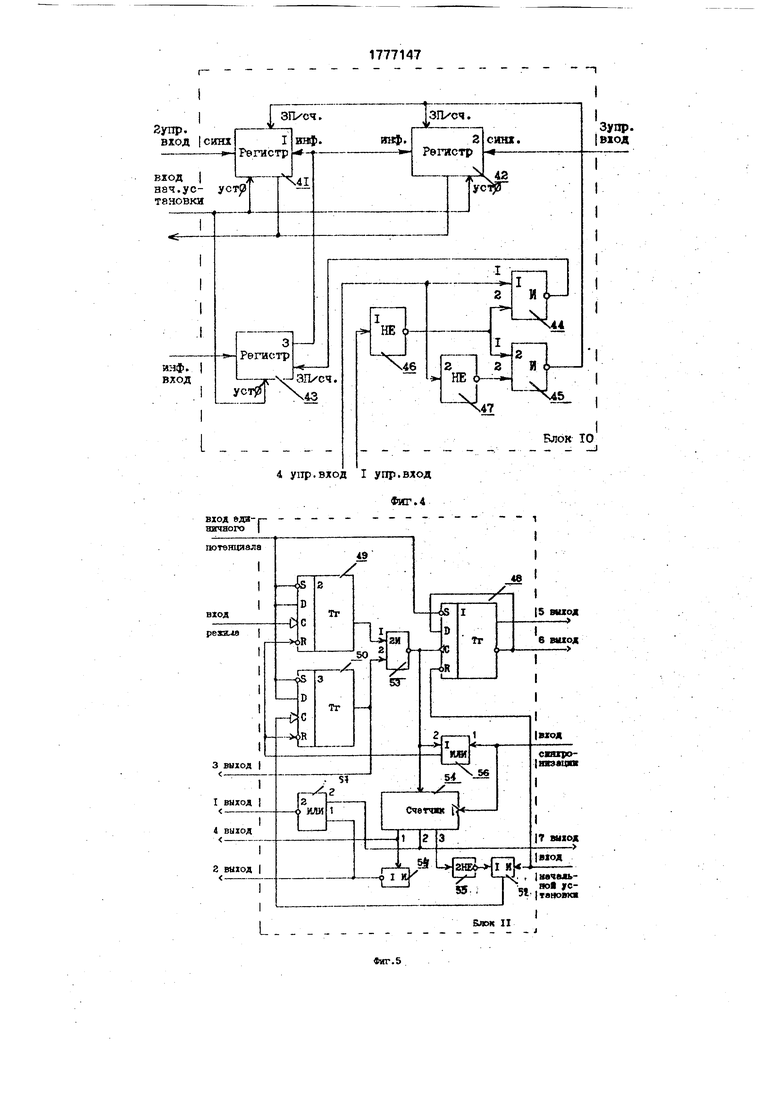

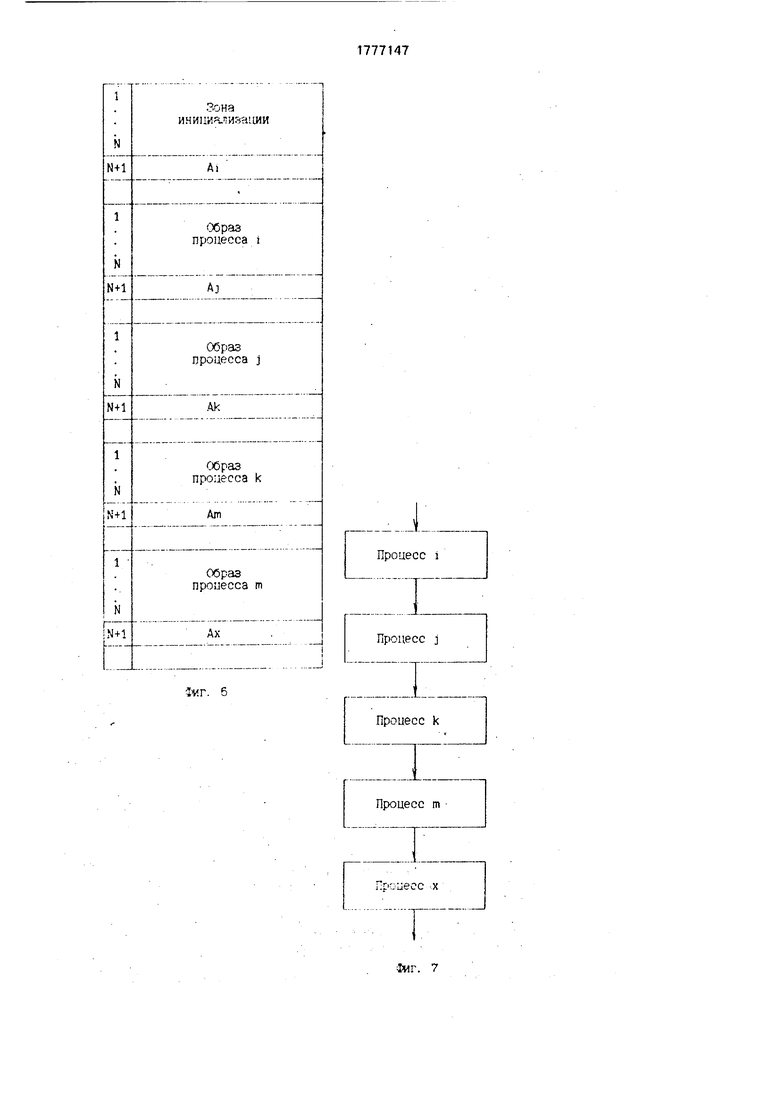

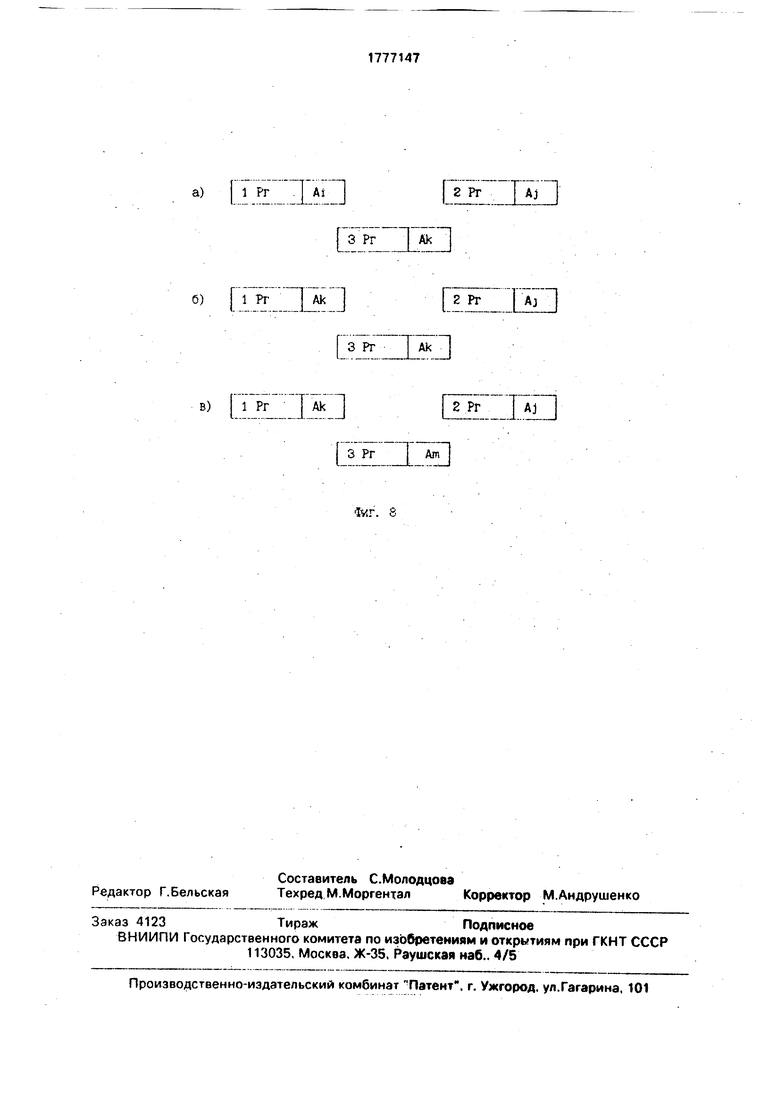

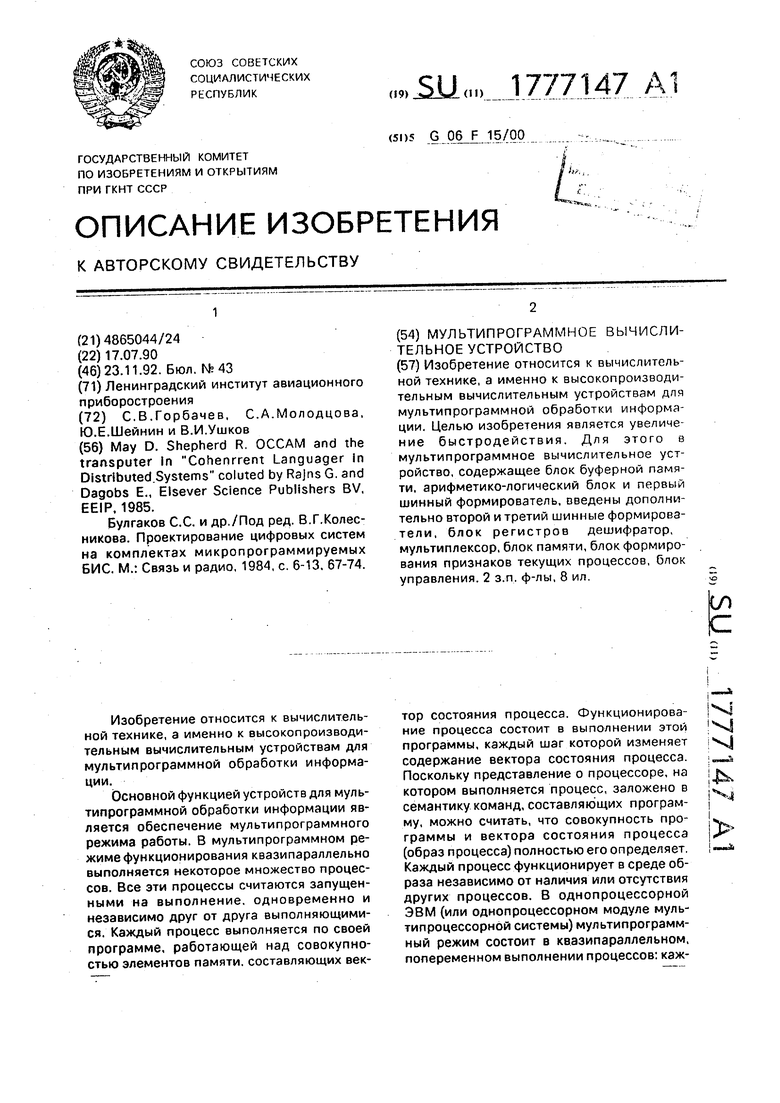

Не фиг. 1 покалано -руюур ч гхсма предлагаемого устройства: на фиг 2 - пример реализации блока буферной памяти; на фиг. 3 - пример реализации арифметико-ло- 5 гического блока; на фиг. А - функциональная схема блока формирования признаков текущих процессов в мультипроцессорной системе; на фиг. 5 - функциональная схема блока управления; на фиг. 6 - структура па0 мяти образов процессов: на фиг. 7 - очередь процессов; на фиг, 8 - содержимое регистров блока формирования признаков текущих процессов в мультипроцессорной системе.

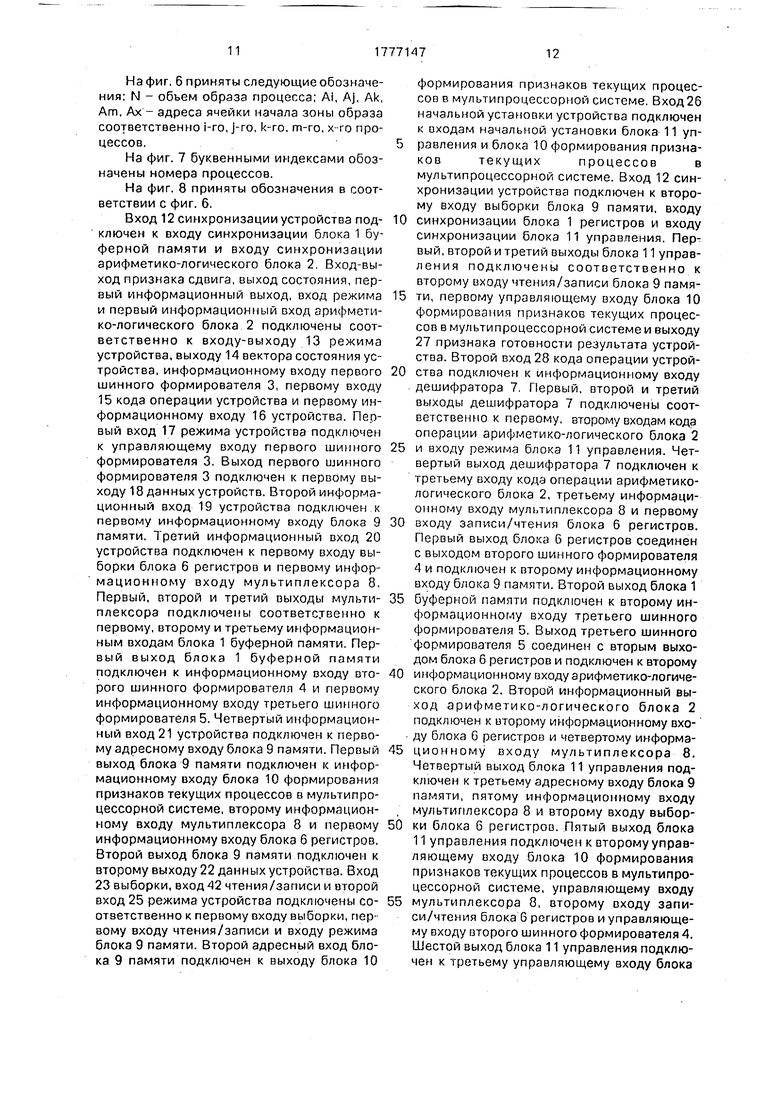

5 Предлагаемое устройство (фиг. содержит: блок 1 буферной памяти, арифметико- логический блок 2, шинные формирователи 3-5, блок 6 регистров, дешифратор 7. мультиплексор 8, блок 9 памя ги, блок 10 форми0 рования признаков текущих процессов ь мультипроцессорной системе, блок 11 управления, вход 12 синхронизации,вход/выход 13 режима , выход 14 вектора состояния, первый вход 15 кода операций, первый ин5 формационный вход 16, первый вход 17 режима, первый выход 18 данных, второй, третий и четвертый информационные входы 19-21, второй выход 22 данных, вход 23 выборки, вход 24 чтения/записи, второй вход

0 25 режима, вход 26 начальной установки, выход 27 признака готовности результата, второй вход 28 кода операций, вход 29 единичного потенциала.

Блок 1 буферной памяти (фиг. 2) содер5 жит N регистров 30-32, дешифратор 33, два мультиплексора 34 и 35, первый, второй и третий входы, вход синхронизации, первый и второй выходы.

Арифметико-логический блок 2 (фиг. 3)

0 содержит регистр 36, мультиплексор 37, арифметико-логическое устройство 38, выходной мультиплексор 39. схему 40 сдвига, вход синхронизации, два информационных входа, три входа кода операций, выход со5 стояния, вход режима, два информационных выхода и вход/выход сдвига.

Блок 10 формирования признаков текущих процессов в мультипроцессорной системе (фиг, 4) содержит три регистра 41-43,

0 два элемента И 44, 45, два элемента НЕ 46,47, четыре управляющих входа, вход начальной установки, информационный вход, выход.

Блок 11 управления (фиг. 5) содержит

5 три триггера 48-50, счетчик 51, три элемента 52-54 И, элемент 55 НЕ и два элемента 56 и 57 ИЛИ. вход режима, вход синхронизации, вход начальной установки, вход единичного потенциала, семь выходов.

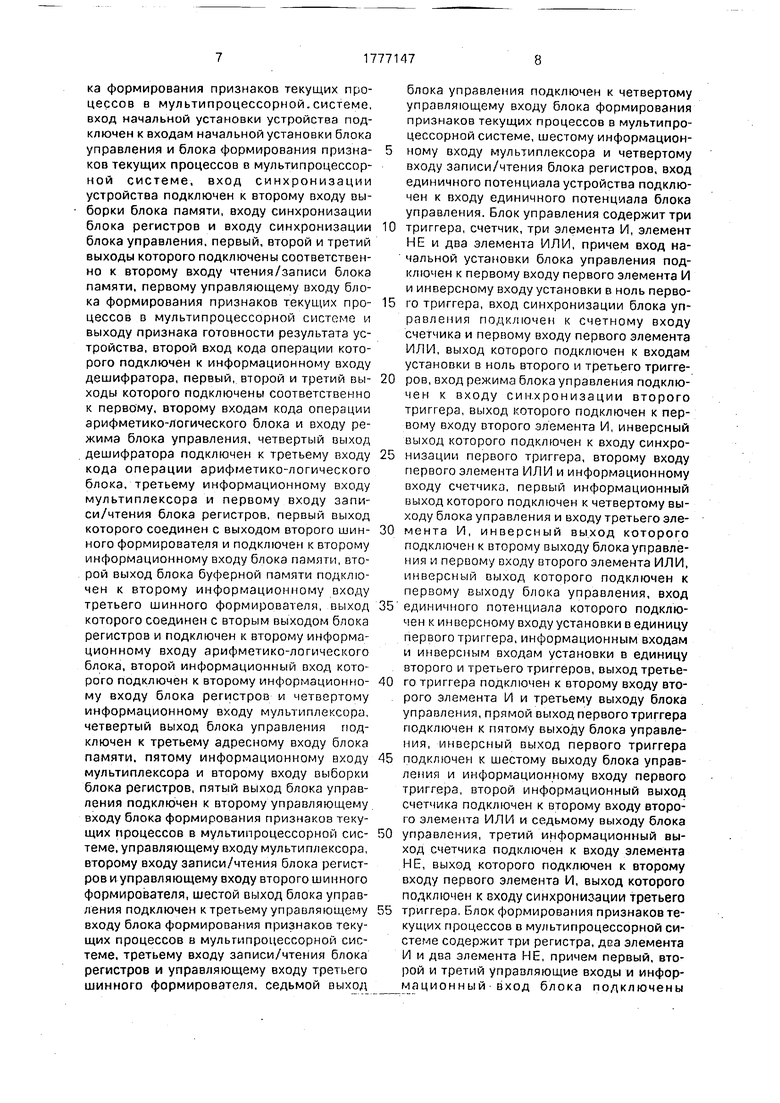

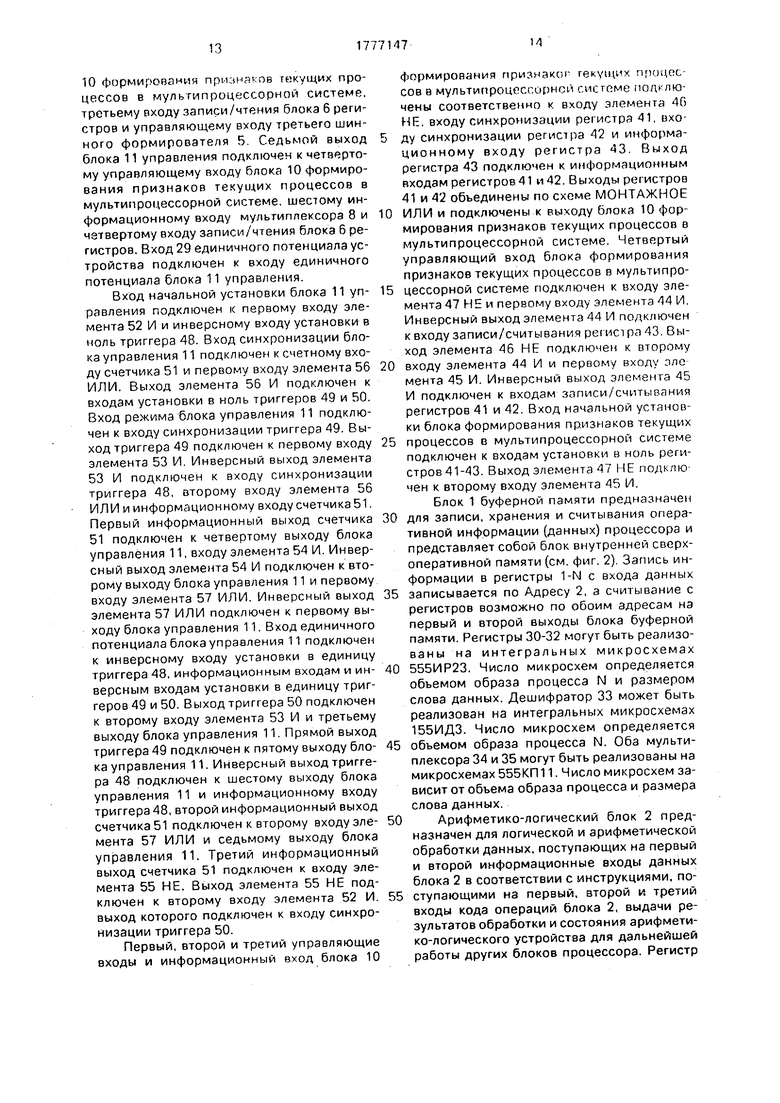

На фиг. 6 приняты следующие обозначения: N - объем образа процесса; Ai, Aj, Ak, Am, Ax - адреса ячейки начала зоны образа соответственно i-го, j-ro, k-ro, m-ro, x го процессов.

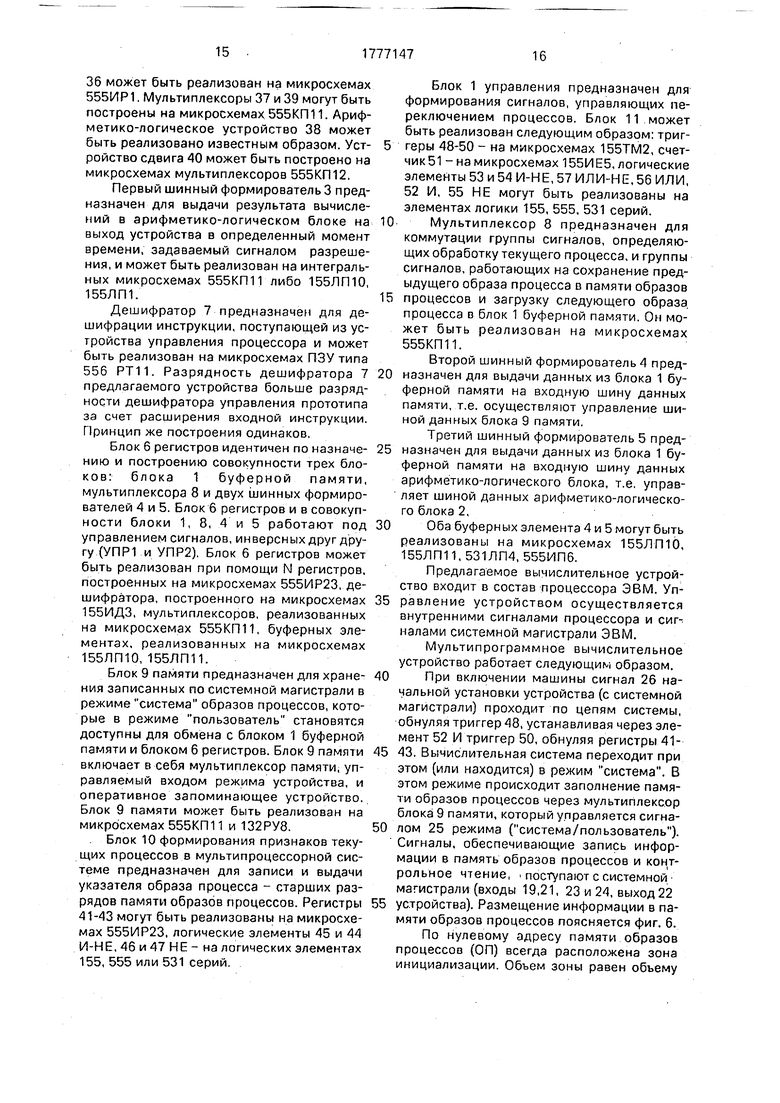

На фиг. 7 буквенными индексами обозначены номера процессов.

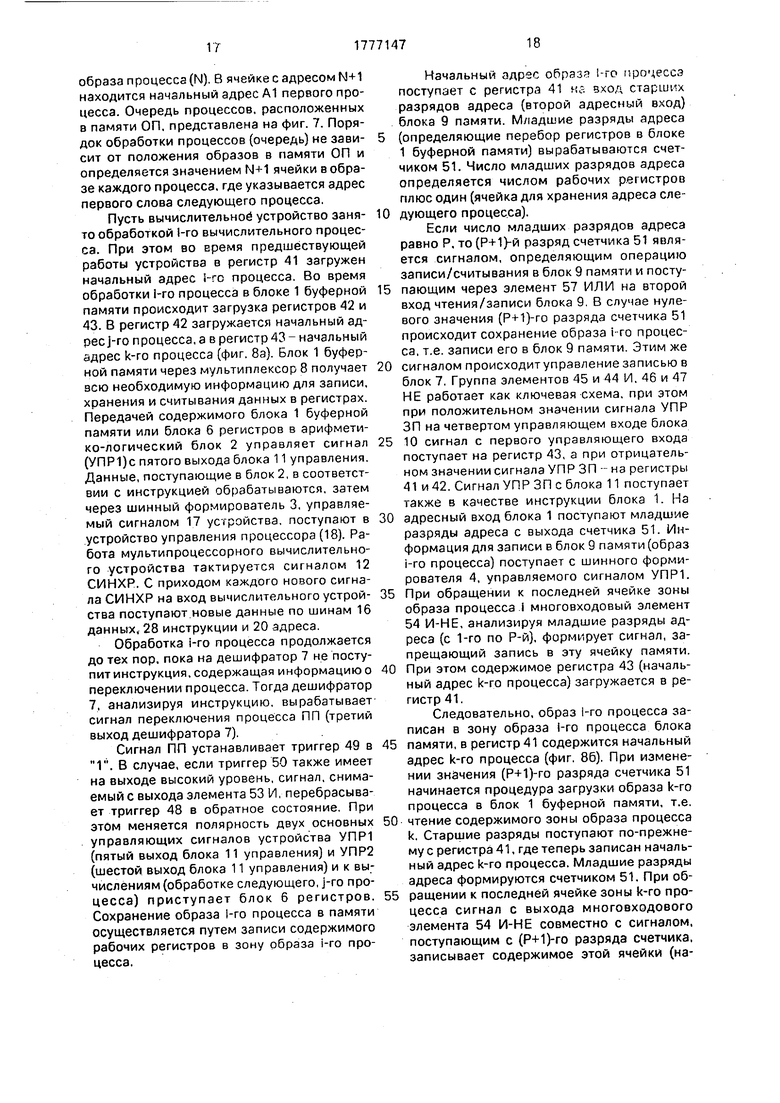

На фиг. 8 приняты обозначения в соответствии с фиг. 6.

Вход 12 синхронизации устройства подключен к входу синхронизации блока 1 буферной памяти и входу синхронизации арифметико-логического блока 2. Вход-выход признака сдвига, выход состояния, первый информационный выход, вход режима и первый информационный вход арифметико-логического блока 2 подключены соответственно к входу-выходу 13 режима устройства, выходу 14 вектора состояния устройства, информационному входу первого шинного формирователя 3, первому входу 15 кода операции устройства и первому информационному входу 16 устройства. Первый вход 17 режима устройства подключен к управляющему входу первого шинного формирователя 3. Выход первого шинного формирователя 3 подключен к первому выходу 18 данных устройств. Второй информационный вход 19 устройства подключен к первому информационному входу блока 9 памяти. Третий информационный вход 20 устройства подключен к первому входу выборки блока 6 регистров и первому информационному входу мультиплексора 8. Первый, второй и третий выходы мультиплексора подключены соответственно к первому, второму и третьему информационным входам блока 1 буферной памяти. Первый выход блока 1 буферной памяти подключен к информационному сходу второго шинного формирователя 4 и первому информационному входу третьего шинного формирователя 5. Четвертый информационный вход 21 устройства подключен к первому адресному входу блока 9 памя ги. Первый выход блока 9 памяти подключен к информационному входу блока 10 формирования признаков текущих процессов в мультипроцессорной системе, второму информационному входу мультиплексора 8 и первому информационному входу блока 6 регистров. Второй выход блока 9 памяти подключен к второму выходу 22 данных устройства. Вход 23 выборки, вход 42 чтения /записи и второй вход 25 режима устройства подключены соответственно к первому входу выборки, первому входу чтения/записи и входу режима блока 9 памяти. Второй адресный вход блока 9 памяти подключен к выходу блока 10

формирования признаков текущих процессов в мультипроцессорной системе. Вход 26 начальной установки устройства подключен к входам начальной установки блока 11 управления и блока 10 формирования признаковтекущихпроцессоввмультипроцессорной системе. Вход 12 синхронизации устройства подключен к второму входу выборки блока 9 памяти, входу

синхронизации блока 1 регистров и входу синхронизации блока 11 управпения. Первый, второй и третий выходы блока 11 управ- ления подключены соответственно к второму входу чтения/записи блока 9 памяти, первому управляющему входу блока 10 формирование признаков текущих процессов в мультипроцессорной системе и выходу 27 признака готовности результата устройства. Второй вход 28 кода операции устройствэ подключен к информационному входу дешифратора 7. Первый, второй и третий выходы дешифратора 7 подключены соответственно к первому, второму входам кода операции арифметико-логического блока 2

и входу режима блока 11 управления. Четвертый выход дешифратора 7 подключен к третьему входу кода операции арифметико- логического блока 2, третьему информационному входу мультиплексора 8 и первому

входу записи/чтения блока 6 регистров. Первый выход блока G регистров соединен с выходом второго шинного формирователя 4 и подключен к второму информационному входу блока 9 памяти. Второй выход блока 1

буферной памяти подключен к второму информационному входу третьего шинного формирователя 5. Выход третьего шинного формирователя 5 соединен с вторым выходом блока 6 регистров и подключен к второму

информационному входу арифметико-логического блока 2. Второй информационный выход арифметико-логического блока 2 подключен к второму информационному входу блока 6 регистров и четвертому информационному входу мультиплексора 8. Четвертый выход блока 11 управления подключен к третьему адресному входу блока 9 памяти, пятому информационному входу мультиплексора 8 и второму входу выборки блока 6 регистров. Пятый выход блока 11 управления подключен к второму управляющему входу блока 10 формирования признаков текущих процессов в мультипроцессорной системе, управляющему входу

мультиплексора 8, второму входу записи/чтения блока 6 регистров и управляющему входу второго шинного формирователя 4. Шестой выход блока 11 управления подключен к третьему управляющему входу блока

10 формирования текущих процессов в мультипроцессорной системе, третьему входу записи /чтения блока 6 регистров и управляющему входу третьего шинного формирователя 5 Седьмой выход блока 11 управления подключен к четвертому управляющему входу блока 10 формирования признаков текущих процессов в мультипроцессорной системе, шестому информационному входу мультиплексора 8 и четвертому входу записи/чтения блока 6 регистров. Вход 29 единичного потенциала устройства подключен к входу единичного потенциала блока 11 управления.

Вход начальной установки блока 11 уп- равления подключен к первому входу элемента 52 И и инверсному входу установки в ноль триггера 48. Вход синхронизации блока управления 11 подключен к счетному входу счетчика 51 и первому входу элемента 56 ИЛИ. Выход элемента 56 И подключен к входам установки в ноль триггеров 49 и 50. Вход режима блока управления 11 подключен к входу синхронизации триггера 49. Выход триггера 49 подключен к первому входу элемента 53 И. Инверсный выход элемента 53 И подключен к входу синхронизации триггера 48, второму входу элемента 56 ИЛИ и информационному входу счетчика 51. Первый информационный выход счетчика 51 подключен к четвертому выходу блока управления 11, входу элемента 54 И. Инверсный выход элемента 54 И подключен к второму выходу блока управления 11 и первому входу элемента 57 ИЛИ. Инверсный выход элемента 57 ИЛИ подключен к первому выходу блока управления 11. Вход единичного потенциала блока управления 11 подключен к инверсному входу установки в единицу триггера 48, информационным входам и ин- версным входам установки в единицу триггеров 49 и 50. Выход триггера 50 подключен к второму входу элемента 53 И и третьему выходу блока управления 11. Прямой выход триггера 49 подключен к пятому выходу бло- ка управления 11. Инверсный выход триггера 48 подключен к шестому выходу блока управления 11 и информационному входу триггера 48, второй информационный выход счетчика 51 подключен к второму входу эле- мента 57 ИЛИ и седьмому выходу блока управления 11. Третий информационный выход счетчика 51 подключен к входу элемента 55 НЕ. Выход элемента 55 НЕ подключен к второму входу элемента 52 И. выход которого подключен к входу синхронизации триггера 50.

Первый, второй и третий управляющие входы и информационный вход блока 10

формирования признаког текущих прпцес, сов в мультипроцессорной системе подключены соответственно к входу элемента 46 НЕ, входу синхронизации регистра 41, входу синхронизации регистра 42 и информационному входу регистра 43. Выход регистра 43 подключен к информационным входам регистров41 и42. Выходы регистров 41 и 42 объединены по схеме МОНТАЖНОЕ ИЛИ и подключены к выходу блока 10 формирования признаков текущих процессов в мультипроцессорной системе. Четвертый управляющий вход блока формирования признаков текущих процессов в мультипроцессорной системе подключен к входу элемента 47 НЕ и первому входу элемента 44 И. Инверсный выход элемента 44 И подключен к входу записи/считывания pet истра43 Выход элемента 46 НЕ подключен к второму входу элемента 44 И и первому входу зло мента 45 И. Инверсный выход элемента 45 И подключен к входам записи/считывания регистров 41 и 42. Вход начальной установки блока формирования признаков текущих процессов в мультипроцессорной системе подключен к входам установки в ноль регистров 41-43. Выход элемента 47 НЕ подклю чен к второму входу элемента 45 И.

Блок 1 буферной памяти предназначен для записи, хранения и считывания оперативной информации (данных) процессора и представляет собой блок внутренней сверхоперативной памяти (см. фиг. 2) Запись информации в регистры 1-N с входа данных записывается по Адресу 2, а считывание с регистров возможно по обоим адресам нэ первый и второй выходы блока буферной памяти. Регистры 30-32 могут быть реализо- ваны на интегральных микросхемах 555ИР23. Число микросхем определяется объемом образа процесса N и размером слова данных. Дешифратор 33 может быть реализован на интегральных микросхемах 155ИДЗ. Число микросхем определяется объемом образа процесса N. Оба мультиплексора 34 и 35 могут быть реализованы на микросхемах 555КП11. Число микросхем зависит от объема образа процесса и размера слова данных.

Арифметико-логический блок 2 предназначен для логической и арифметической обработки данных, поступающих на первый и второй информационные входы данных блока 2 в соответствии с инструкциями, поступающими на первый, второй и третий входы кода операций блока 2, выдачи результатов обработки и состояния арифметико-логического устройства для дальнейшей работы других блоков процессора. Регистр

36 может быть реализован на микросхемах 555ИР1. Мультиплексоры 37 и 39 могут быть построены на микросхемах 555КП11. Арифметико-логическое устройство 38 может быть реализовано известным образом. Устройство сдвига 40 может быть построено на микросхемах мультиплексоров 555КП12.

Первый шинный формирователь 3 предназначен для выдачи результата вычислений в арифметико-логическом блоке на выход устройства в определенный момент времени, задаваемый сигналом разрешения, и может быть реализован на интегральных микросхемах 555КП11 либо 155ЛП10, 155ЛП1.

Дешифратор 7 предназначен для дешифрации инструкции, поступающей из устройства управления процессора и может быть реализован на микросхемах ПЗУ типа 556 РТ11. Разрядность дешифратора 7 предлагаемого устройства больше разрядности дешифратора управления прототипа за счет расширения входной инструкции. Принцип же построения одинаков,

Блок 6 регистров идентичен по назначению и построению совокупности трех блоков: блока 1 буферной памяти, мультиплексора 8 и двух шинных формирователей 4 и 5. Блок б регистров и в совокупности блоки 1, 8, 4 и 5 работают под управлением сигналов, инверсных друг другу (УПР1 и УПР2). Блок 6 регистров может быть реализован при помощи N регистров, построенных на микросхемах 555ИР23, дешифратора, построенного на микросхемах 155ИДЗ, мультиплексоров, реализованных на микросхемах 555КП11, буферных элементах, реализованных на микросхемах 155ЛП10, 155ЛП11.

Блок 9 памяти предназначен для хранения записанных по системной магистрали в режиме система образов процессов, которые в режиме пользователь становятся доступны для обмена с блоком 1 буферной памяти и блоком 6 регистров. Блок 9 памяти включает в себя мультиплексор памяти, управляемый входом режима устройства, и оперативное запоминающее устройство. Блок 9 памяти может быть реализован на микросхемах 555КП11 и 132РУ8.

Блок 10 формирования признаков текущих процессов в мультипроцессорной системе предназначен для записи и выдачи указателя образа процесса - старших разрядов памяти образов процессов. Регистры 41-43 могут быть реализованы на микросхемах 555ИР23, логические элементы 45 и 44 И-НЕ, 46 и 47 НЕ - на логических элементах 155, 555 или 531 серий.

Блок 1 управления предназначен для формирования сигналов, управляющих переключением процессов. Блок 11 может быть реализован следующим образом: триггеры 48-50 - на микросхемах 155ТМ2, счет- чик51 -на микросхемах 155ИЕ5, логические элементы 53 и 54 И-НЕ, 57 ИЛИ-НЕ, 56 ИЛИ, 52 И, 55 НЕ могут быть реализованы на элементах логики 155, 555, 531 серий.

Мультиплексор 8 предназначен для

коммутации группы сигналов, определяющих обработку текущего процесса, и группы сигналов, работающих на сохранение предыдущего образа процесса в памяти образов

процессов и загрузку следующего образа процесса в блок 1 буферной памяти. Он может быть реализован на микросхемах 555КП11.

Второй шинный формирователь 4 предназначен для выдачи данных из блока 1 буферной памяти на входную шину данных памяти, т.е. осуществляют управление шиной данных блока 9 памяти.

Третий шинный формирователь 5 предназначен для выдачи данных из блока 1 буферной памяти на входную шину данных арифметико-логического блока, т.е. управляет шиной данных арифметико-логического блока 2.

Оба буферн ых элемента 4 и 5 могут быть

реализованы на микросхемах 155ЛП10, 155ЛП11, 531ЛП4, 555ИП6.

Предлагаемое вычислительное устройство входит в состав процессора ЭВМ. Управление устройством осуществляется внутренними сигналами процессора и сигналами системной магистрали ЭВМ.

Мультипрограммное вычислительное устройство работает следующим образом.

При включении машины сигнал 26 начальной установки устройства (с системной магистрали) проходит по цепям системы, обнуляя триггер 48, устанавливая через элемент 52 И триггер 50, обнуляя регистры 4143, Вычислительная система переходит при этом (или находится) в режим система. В этом режиме происходит заполнение памяти образов процессов через мультиплексор блока 9 памяти, который управляется сигналом 25 режима (система/пользователь). Сигналы, обеспечивающие запись информации в память образов процессов и контрольное чтение, поступают с системной магистрали (входы 19,21, 23 и 24, выход22

устройства). Размещение информации в памяти образов процессов поясняется фиг. 6. По нулевому адресу памяти образов процессов (ОП) всегда расположена зона инициализации. Объем зоны равен объему

образа процесса (N). В ячейке с адресом N+1 находится начальный адрес А1 первого процесса. Очередь процессов, расположенных в памяти ОП, представлена на фиг. 7. Порядок обработки процессов (очередь) не зави- сит от положения образов в памяти ОП и определяется значением N+1 ячейки в образе каждого процесса, где указывается адрес первого слова следующего процесса.

Пусть вычислительное устройство заня- то обработкой 1-го вычислительного процесса. При этом во время предшествующей работы устройства в регистр 41 загружен начальный адрес Ко процесса. Во время обработки 1-го процесса в блоке 1 буферной памяти происходит загрузка регистров 42 и 43. В регистр 42 загружается начальный адрес j-ro процесса, а в регистр 43 - начальный адрес k-ro процесса (фиг. 8а). Блок 1 буферной памяти через мультиплексор 8 получает всю необходимую информацию для записи, хранения и считывания данных в регистрах. Передачей содержимого блока 1 буферной памяти или блока 6 регистров в арифметико-логический блок 2 управляет сигнал (УПР1)с пятого выхода блока 11 управления. Данные, поступающие в блок 2, в соответствии с инструкцией обрабатываются, затем через шинный формирователь 3, управляемый сигналом 17 устройства, поступают в устройство управления процессора (18). Работа мультипроцессорного вычислительного устройства тактируется сигналом 12 СИНХР. С приходом каждого нового сигнала СИНХР на вход вычислительного устрой- ства поступают новые данные по шинам 16 данных, 28 инструкции и 20 адреса.

Обработка i-ro процесса продолжается до тех пор, пока на дешифратор 7 не поступит инструкция, содержащая информацию о переключении процесса. Тогда дешифратор 7, анализируя инструкцию, вырабатывает сигнал переключения процесса ПП (третий выход дешифратора 7).

Сигнал ПП устанавливает триггер 49 в 1. В случае, если триггер 50 также имеет на выходе высокий уровень, сигнал, снимаемый с выхода элемента 53 И, перебрасывает триггер 48 в обратное состояние. При этом меняется полярность двух основных управляющих сигналов устройства УПР1 (пятый выход блока 11 управления) и УПР2 (шестой выход блока 11 управления) и к вычислениям (обработке следующего, j-ro процесса) приступает блок 6 регистров. Сохранение образа 1-го процесса в памяти осуществляется путем записи содержимого рабочих регистров в зону образа 1-го процесса.

Начальный адрес образ 1-го процесса поступает с регистра 41 ка вход старших разрядов адреса (второй адресный вход) блока 9 памяти. Младшие разряды адреса (определяющие перебор регистров в блоке 1 буферной памяти) вырабатываются счетчиком 51. Число младших разрядов адреса определяется числом рабочих регистров плюс один (ячейка для хранения адреса следующего процесса).

Если число младших разрядов адреса равно Р. то (Р+1}-й разряд счетчика 51 является сигналом, определяющим операцию записи/считывания в блок 9 памяти и поступающим через элемент 57 ИЛИ на второй вход чтения/записи блока 9. В случае нулевого значения (Р+1)-го разряда счетчика 51 происходит сохранение образа i го процесса, т.е. записи его в блок 9 памяти. Этим же сигналом происходит управление записью в блок 7. Группа элементов 45 и 44 И. 46 и 47 НЕ работает как ключевая схема, при этом при положительном значении сигнала УПР ЗП на четвертом управляющем входе блока 10 сигнал с первого управляющего входа поступает на регистр 43, а при отрицательном значении сигнала УПР ЗП - на регистры 41 и 42. Сигнал УПР ЗП с блока 11 поступает также в качестве инструкции блока 1. На адресный вход блока 1 поступают младшие разряды адреса с выхода счетчика 51. Информация для записи в блок 9 памяти (образ i-ro процесса) поступает с шинного формирователя 4, управляемого сигналом УПР1. При обращении к последней ячейке зоны образа процесса i многовходовый элемент 54 И-НЕ, анализируя младшие разряды адреса (с 1-го по Р-й), формирует сигнал, запрещающий запись в эту ячейку памяти. При этом содержимое регистра 43 (начальный адрес k-ro процесса) загружается в регистр 41.

Следовательно, образ 1-го процесса записан в зону образа 1-го процесса блока памяти, в регистр 41 содержится начальный адрес k-ro процесса (фиг. 86). При изменении значения (Р-Н)-го разряда счетчика 51 начинается процедура загрузки образа k-ro процесса в блок 1 буферной памяти, т.е. чтение содержимого зоны образа процесса k. Старшие разряды поступают по-прежнему с регистра 41, где теперь записан начальный адрес k-ro процесса. Младшие разряды адреса формируются счетчиком 51. При обращении к последней ячейке зоны k-ro процесса сигнал с выхода многовходового элемента 54 И-НЕ совместно с сигналом, поступающим с (Р+1)-го разряда счетчика, записывает содержимое этой ячейки (начальный адрес m-ro процесса) в регистр 43 (фиг. 8в).

После записи информации в регистр 43 перезапись образов процессов окончена. В результате проделанных операций образ I- го процесса сохранен в памяти образов процессов, в блок 1 буферной памяти загружен образ k-ro процесса, в регистре 41 содержится начальный адрес k-ro процесса, в регистре 42 - начальный адрес j-ro (текущего) процесса, в регистре 43 - начальный адрес m-го процесса. Инструкция (второй вход кода операций 28), содержащая команду формирования сигнала переключения процесса ПП, поступит на дешифратор 4 только в том случае, если на один из входов условий устройства управления поступит сигнал признака готовности результата (ГОТ) с выхода 27 устройства, показывающий, что предыдущая команда, содержащая ПП. выполнена, т.е. завершена перезагрузка и сохранение содержимого рабочих регистров. Сигнал ГОТ поступает с выхода триггера 50, который устанавливается через элементы 55 НЕ и 52 И (Р+2)-м разрядом счетчика 51. Следующий сигнал ПП устанавливает триггер 49 и через элемент 56 И-НЕ опрокидывает триггер 48.

Ближайший по времени сигнал синхронизации СИНХР(вход 12 синхронизации устройства) в сочетании с сигналом, приходящим с выхода элемента 53 И-НЕ, сбрасывает оба триггера 49 и 50 в первоначальное состояние. Таким образом,устройство готово к приему следующей команды переключения процессов. Процесс инициализации происходит следующим образом. Для того чтобы начать обработку первого процесса, необходимо в программно-недоступные регистры 41 и 43 поместить необходимую информацию, а именно: в регистр 41 - начальный адрес первого процесса (его адрес хранится в ячейке N+1 зоны инициализации); в регистр 43 - начальный адрес второго процесса (его адрес хранится в ячейке N+1 первого процесса).

Для этого программе обработки процессов предшествует программа инициализации, содержащая 2 команды переключения процесса, причем сигнал система/пользователь переводится в режим пользователь. Триггер 50 установлен сигналом начальной установки (вход 26 устройства) в режим готовности (специально для инициализации). Все три регистра 41-43 и триггер 48 управления сброшены этим же сигналом в О. С приходом первого сигнала ПП триггер 48 управления устанавливается в 1 по

прямому выходу (УПР1) и в О по инверсному (УПР2). При этом начинается обработка процесса блоком 1 буферной памяти. Для перезагрузки открыт блок 6 регистров. Поскольку регистры 41-43 обнулены, то в регистре 41 записан О. Следовательно, непредсказуемая информация из блока 5 регистров записывается в зону инициализации. Затем происходит запись в регистр 42

содержимого регистра 43 (нулевое значение). После записи в блок 6 регистров содержимого зоны инициализации проводится загрузка содержимого N+1 ячейки зоны инициализации в регистр 43. После этого формируется сигнал ГОТ и устройство может принять второй сигнал ПП. С приходом второго сигнала ПП триггер 48 опрокидывается, и теперь сигнал УПР1 имеет значение О, а сигнал УПР2-значение 1. Тогда для

обработки процесса включен блок 6 регистров, а в блоке 1 производится перезагрузка образа процесса по рассмотренному выше алгоритму, т.е. в зону инициализации (врегистре41 содержится О)записывается

непредсказуемая информация из блока 1 буферной памяти. Затем в регистр 41 переписывается содержимое регистра 43 (начальный адрес первого процесса). Из зоны образа первого процесса информация загружается в блок 1 буферной памяти, а содержимое N+1 ячейки зоны - в регистр 43, после чего счетчик 51 формирует сигнал, устанавливающий триггер 50. Таким образом, в блоке 1 буферной памяти содержится

образ первого процесса, в регистре 41 - начальный адрес первого процесса, в регистре 43 - начальный адрес второго процесса. Следовательно, при подаче следующего сигнала ПП можно начинать обработку первого процесса в блоке 1 буферной памяти. При этом в блоке 6 регистров будет происходить, согласно алгоритму работы, перезагрузка образов, а именно: содержимое блока 6 (непредсказуемая информация) будет загружено в зону инициализации (регистр 41 содержит О), содержимое регистра 43 (начальный адрес второго процесса) помещается в регистр 42, информация из зоны образа второго процесса

записывается в рабочие регистры блока 6. а содержимое ячейки N+1 зоны образа второго процесса - в регистр 43. Таким образом, мультипрограммное вычислительное устройство готово к обработке процессов.

Блок 1 буферной памяти представляет

собой двухадресный регистр, в состав которого входят N регистров 30-32 для хранения информации, в том числе и образов процессов; дешифратор 33 и два мультиплексора 34

и 35, Запись в регистры 30-32 возможна по адресу АДРЕС2. а считывание по обоим адресам АДРЕС1 и АДРЕС2. При чтение оба адреса поступают на вход блока 1 одновременно, и с мультиплексоров 34 и 35 данные с двух регистров, определяемых адресами АДРЕС1 и АДРЕС2, поступают на первый и второй выходы данных блока 1. Выбор одного из регистров 30-32 для записи осуществляется дешифратором 33, на вход которого кроме адреса АДРЕС2 поступает сигнал инструкции, разрешающей запись. Запись непосредственно в выбранный регистр осуществляется сигналом СИНХР. Данные для записи поступают со второго выхода мультиплексора 8.

Арифметико-логический блок 2 выполняет основные вычислительные функции ус- фойства. Блок 2 включает двухвходовое арифметико-логическое устройство 38 (АЛУ), выполняющее восемь логических операций и формирующее признаки результата и состояния, На входах АЛУ включает селектор источника данных (мультиплексор 37), позволяющий комбинировать в качестве па- ры операндов АЛУ информацию из нескольких источников: с первого информационного входа устройства 16, с первого и второго выходов блока 1, нулевое значение. Данные с первого и второго выхо- дов блока 1 поступают на мультиплексор 37 через шинный формирователь 5 и регистр 36, который устраняет неопределенность в кольце передачи информации с выхода блока 1 на его вход. С выхода АЛУ информация поступает на селектор выходных данных (мультиплексор 39). На второй вход мультиплексора 39 информация может быть подана с выхода Д1 регистра 36, минуя АЛУ 38. С выхода АЛУ 38 информация через сдвига- тель данных 40 поступает на первый вход данных мультплексора 8. Управление работой блока 2 осуществляется микрокодом (вход инструкции) 10-12 (первый, второй и третий входы кода операций). Входы 13 (вход/выход режима устройства) и 15 (первый вход кода операций) устройства предназначены для управления работой блока 2 устройством управления процессора.

По сравнению с прототипом переключе- ние процессов в предлагаемом устройстве происходит аппаратно, при этом осуществляется распараллеливание функций обработки текущего процесса с функцией сохранения образа предыдущего процесса и восстановления образа следующего за текущим процесса.

Такое распараллеливание ведет, естественно, к сокращению времени переключения процессов го сравнению с пооютипсм на время, пропорциональное образу процесса, При большем размере образа процесса и достаточно частом переключении процессов использование предлагаемого устройства позволяет повысить производительность мультипрограммной вычислительной системы в несколько раз.

В связи с тем, что память образов процессов в рассматриваемом примере реализации определяется размером адресного пространства вычислительной системы, которая может иметь диспетчер памяти или иные устройства расширения адресного пространства, область адресов, выделяемых для работы с памятью образов процессов, может быть достаточно большой. Следовательно, вычислительная система сможет обработать большое число процессов, определяемое размером выделенного для этого адресного пространства.

Исходя из вышеизложенного, можно сделать вывод, что мультипрограммное вычислительное устройство позволяет по сравнению с прототипом увеличить производительность вычислительной системы при обработке большого числа процессов.

Формула изобретения 1. Мультипрограммное вычислительное устройство, содержащее блок буферной памяти, арифметико-логический блок и первый шинный формирователь, причем вход синхронизации устройства подключен к входу синхронизации блока буферной памяти и к входу синхронизации арифметико-логического блока, вход-выход признака сдвига, выход состояния, первый информационный вход которого подключены соответсвенно к вход-выходу режима устройства, к выходу вектора состояния устройства, к информационному входу первого шинного формирователя, к первому входу кода операции устройства и к первому информационному входу устройства, первый вход режима устройства подключен к управляющему входу первого шинного формирователя, выход которого подключен к первому выходу данных устройства, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит второй и третий шинные формирователя, блок регистров, дешифратор, мультиплексор, блок памяти, блок формирования признаков текущих процессов в мультипроцессорной системе и блок управления, при этом второй информационный вход устройства подключен к первому информационному входу блока памяти, третий

информационный вход устройства подключен к первому входу выборки блока регистров и к первому информационному входу мультиплексора, первый, второй и третий выходы которого подключены соответствен- но к первому, второму и третьему информационным входам блока буферной памяти, первый выход которого подключен к информационному входу второго шинного формирователя и к первому информационному входу третьего шинного формирователя, четвертый информационный вход устройства подключен к первому адресному входу блока памяти, первый выход которого подключен к информационному входу блока формирования признаков текущих процессов в мультипроцессорной системе, к второмуинформационномувходумультиплексора и к первому информационному входу блока регистров, второй выход блока памяти подключен к второму выходу данных устройства, вход выборки, вход чтения-записи и второй вход режима которого подключены соответственно к первому входу выборки, к первому входу чтения-записи и к входу режима блока памяти, второй адресный вход которого подключен к выходу блока формирования признаков текущих процессов в мультипроцессорной системе, вход начальной установки устройства под- ключен к входам начальной установки блока управления и блока формирования признаков текущих процессов в мультипроцессорной системе, вход синхронизации устройства подключен к второму входу вы- оорки блока памяти, к входу синхронизации блока регистров и входу синхронизации блока управления, первый, второй и третий выходы которого подключены соответственно к второму входу чтения-записи блока па- мяти, к первому управляющему входу блока формирования признаков текущих процессов в мультипроцессорной системе и к выходу признака готовности результата устройства, второй вход кода операции ко- торого подключен к информационному входу дешифратора, первый, второй и третий выходы которого подключены соответственно к первому, второму входам-кода операции арифметико-логического блока и к входу режима блока управления, четвертый выход дешифратора подключен к третьему входу кода операции арифметико-логического блока, к третьему информационному входу мультиплексора и к первому входу записи- ч генИя блока регист ров первый выход которого соединен с выходом второго шинного формирователя и подключен к второму информационному входу блокапамчти второй

выход блока буферной памяти подключен к второму информационному входу третьего шинного формирователя, выход которого соединен с вторым выходом блока регистров и подключен к второму информационному входу арифметико-логического блока, второй информационный выход которого подключен к второму информационному входу блока регистров и к четвертому информационному входу мультиплексора, четвертый выход блока управления подключен к третьему адресному входу блока памяти, к пятому информационному входу мультиплексора и к второму входу выборки блока регистров, пятый выход блока управления подключен к второму управляющему входу блока формирования признаков текущих процессов в мультипроцессорной системе, к управляющему входу мультиплексора, к второму входу записи/чтения блока регистров и к управляющему входу второго шинного формирователя, шестой выход блока управления подключен к третьему управляющему блока формирования признаков текущих хщессов в мультипроцессорной системе, к третьему входу записи-чтения блока регистров и к управляющему входу третьего шинного формирователя, седьмой выход блока управления подключен к четвертому управляющему входу блока формирования признаков текущих процессов в мультипроцессорной системе, к шестому информационному входу мультиплексора и к четвертому входу записи-чтения блока регистров, вход единичного потенциала устройства подключен к входу единичного потенциала блока управления.

2. Устройство поп. 1,отличающее- с я тем, что блок управления содержит три триггера, счетчик, три элемента И, элемент НЕ и два элемента ИЛИ, причем вход начальной установки блока управления под ключен к первому входу первого элемента И и к инверсному входу установки в О первого триггера, вход синхронизации блока управления подключен к счетному входу счетчика и к первому входу первого элемента ИЛИ, выход которого подключен к входам установки в О второго и третьего триггеров, вход режима блока управления подключен к входу синхронизации второго триггера, выход которого подключен к первому входу второго элемента И, инверсный выход которого подключен к входу синхронизации первого триггера, к второму входу первого элемента ИЛИ и к информационно- , му входу счетчика, первый информационный выход которого подключен к четвертому выходу блока управления и к

входу третьего элемента И, инверсный выход которого подключен к второму выходу блока управления и первому входу второго элемента ИЛИ, инверсный выход которого подключен к первому выходу блока управления, вход единичного потенциала которого подключен к инверсному входу установки в 1 первого триггера, к информационным входам и инверсным входам установки в 1 второго и третьего триггеров, выход третьего триггера подключен к второму входу второго элемента И и х третьему выходу блока управления, прямой выход первого триггера подключен к пятому выходу блока управления, инверсный выход первого триггера подключен к шестому выходу блока управления и к информационному входу первого триггера, второй информационный выход счетчика подключен к второму входу второго элемента ИЛИ и к седьмому выходу блока управления, третий информационный выход счетчика подключен к входу элемента НЕ, выход которого подключен к второму входу первого элемента И, выход которого подключен к входу синхронизации третьего триггера.

3. Устройство по п. 1,отличающее- с я тем, что блок формирования признаков

текущих процессов в мультипроцессорной системе содержит три регистра, два элемента И и два элемента НЕ. причем первый, второй и третий управляющие входы и информационный вход блока подключены соответственно к входу первого элемента НЕ. к входу синхронизации первого регистра, к входу синхронизации второго регистра и информационному входу третьего регистра,

выход которого подключен к информационным входам первого и второго регистров, выходы КОТОРЫХ объединены по схеме МОНТАЖНОЕ ИЛИ и подключены к выходу блока, четвёртый управляющий вход которого подключен к входу второго элемента НЕ и первому входу первого элемента И, инверсный выход которого подключен х входу записи/считывания третьего регистра, выход первого элемента НЕ подключен к

второму входу первого элемента И и к первому входу второго элемента И. инверсный выход которого подключен к входам записи/ считывания первого и второго регистров., вход начальной установки блока подключен

к входам установки Б О первого, второго и третьего регистров, выход второго элемента НЕ подключен к второму входу второго элемента И.

..tL

fr

rngj

tftlj- №

UJj-./njf

г 1Шг ,

t MWwLZ-. .

7 7™tfi bvnintJu мчу/ц

v.A9(,hSndu MVa(

Д/Л /

cbvn

l07H2l/f/0dufi

13

J.JH

SZ JDfi

WJOJ

/776

Jtfvf

1777147

вход

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1987 |

|

SU1536396A1 |

| Процессор для мультипроцессорной системы | 1989 |

|

SU1688252A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Процессор | 1989 |

|

SU1725224A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

Изобретение относится к вычислительной технике, а именно к высокопроизводительным вычислительным устройствам для мультипрограммной обработки информации. Целью изобретения является увеличение быстродействия. Для этого в мультипрограммное вычислительное устройство, содержащее блок буферной памяти, арифметико-логический блок и первый шинный формирователь, введены дополнительно второй и третий шинные формирователи, блок регистров дешифратор, мультиплексор, блок памяти, блок формирования признаков текущих процессов, блок управления. 2 з.п. ф-лы, 8 ил.

Адрес I

2 вход)

Г Рг2

V V V

J. v .Vj u

I выход Фиг. 2

8ЮДХВНЮД3 ВХОДI

сдвиге кода операция

Г Адрес.

т

±.

3 вход

33

зг

L

Jt

вход сингро1НИ38ЦИИ

Г

-VV

Uz

Ъч

X

33

Блок I

выход

2ynp. вход |синх

вход |

нач.ус- устр

таяовки

инф. вход

4 упр.вход I упр.вход Фиг. 4

вюд еда-г- ничаого I

г выход |

L

Зу пр.

|вюд

Д Ц5ЫГАЛ -О I JtKЦ -1 l-rNJ , 1мвЧвДЬ1 «. ус85 .51 t.-..

Блок II

Rt «

31 |тановкш I

Зона

ИНИЦИЯ-ЧИЗаЦИИ

N N-H

Ai

Образ процесса i

N N+l

Aj

Образ процесса j

N N+l

Ak

Образ процесса k

Am

Образ процесса m

JN+1

Ax

Ј«r. 6

Процесс i

Процесс j

Процесс k

Процесс m

:::r

j.p-.Lieec x

Т

tor. 7

a) I L IAi ИLLM

C3 Pr 1№ II

6) I 1 Pr Ak

з

в) 1 Pr I Ak J

3 Pr J

2 Pr

Aj

fer. 8

| May D | |||

| Shepherd R | |||

| OCCAM and the transputer in Cohenrrent Languager in Distrlbuted.Systems coluted by Rajns G | |||

| and Dagobs E., Elsever Science Publishers BV, EEIP | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Булгаков С.С | |||

| и др./Под ред | |||

| В.Г.Колесникова | |||

| Проектирование цифровых систем на комплектах микропрограммируемых БИС | |||

| М.: Связь и радио, 1984, с | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1992-11-23—Публикация

1990-07-17—Подача