1

: . Изобретение относится к вычисли- телыюй технике, а именно к устрой- |ствам управления накопителями на ма ниткой ленте, и является усовершенствованием известного устройства, по авт.св. N 1 142839.

Цель изобретения - повышение быстродействия за счет сокращения времени локализации неисправностей.

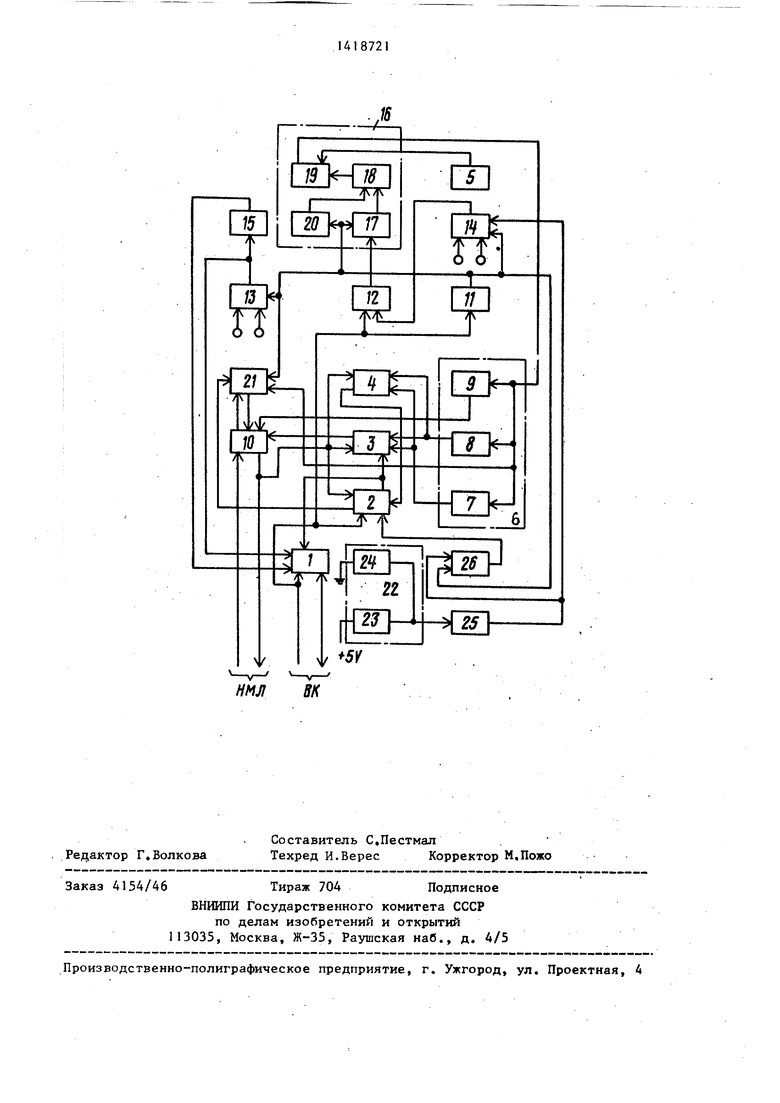

На чертеже представлена структурная схема устройства для сопряжения вычислительного комплекса с накопителем на магнитной ленте.

Устройство для сопряжения вычислительного комплекса с накопителем на магнитной ленте содержит первый блок 1 приемопередатчиков, блок 2 регистров, блок 3 циклического контроля, блок 4 хранения признаков состояния, генератор 5 тактовых импульсов, блок 6 синхронизации, включающий в себя синхронизатор 7 записи.

синхронизатор

воспроизведения, синхронизатор 9 работы накопителей, . второй блок 10 приемопередатчиков, регистр 1 Г хранения режимов контроля триггер 12 управления синхронизацией коммутатор 13 контролируемых сигналов, коммутатор 14. сигналов сброса, блок 15 триггеров запоминания динамических сигналов, блок 16 управления синхронизацией, первый элемент И 17, элемент ИЛИ 18, второй элемент И 19, первый элемент НЕ 20, имитатор 21 накопителя, коммутатор 22 режима диагностирования, состоящий из резистора 23 к переключателя 24, второй элемент НЕ 25, элемент И-НЕ 26.

Коммутатор 22 режима диагностирования предназначен для создания двух режимов диагностирования,

. Резистор 23 служит для создания напряжения, соответствующего логической 1 или логического О на входе второго элемента НЕ 25 при выключенном ил и включенном переключателе 24 соответственно,

В качестве переключателя 24 может быть использован переключатель, например типа ВДМ1-2, устанавливаемый на плате печатного монтажа. В качестве резистора 23, например, может быть использоваН резистор МЛТ-0,125-1 ком ± t 5%.

Устройство работает следующим об разом.

При работе устройства в комплексном режиме регистр 11 сброшен, та,- 5

10

15

20

, ,

25

30

35

40

45

ь ±

50

55

КИМ образом, высокий логический уровень на выходе первого элемента НЕ 20 через элемент HJBi 18 поступает на первый вход второго элемента И 19 и разрепшет поступление управляющей частоты от генератора 5 на входы блока 6 синхронизации. Таким образом, обеспечивается синхронизация.обмена данными между шиной вычислительного комплекса и накопителями. Положение переключателя 24 на работу устройства в комплекс ном режиме никакого влияния не оказывает, так как регистр 11 хранения режимов контроля сброшен, то появление сигнала низкого уровня на втором входе элемента И-НЕ 26 независимо от уро вня сигнала на первом входе этого элемента вызывает появление на выходе элемента И-НЕ 26 сигнала логической I, поступающего на входы вычитания блока 2 регистров.

Для облегчения и ускорения процесса отыскания возможных неисправностей устройства в нем предусмотрены два диагностических режима (в зависимости от положения переключателя 24), позволяющие проследить за состоянием группы наиболее важных по функциональному назначению триггеров и сигналов, именуемых контролируемьши точками и динамическими сигналами, во время вьшолнения команды.

Управление работой устройства в обоих режимах диагностирования осуществляется под действием диагностической программы, которая перед началом диагностирования вводится в оперативную память процессора.

Диагностирование аппаратуры происходит без участия накопителей на магнитной ленте, а необходимые сигналы вырабатываются имитатором 21 накопи-. теля,

При включенном переключателе 24 устройство работает в шаговом режиме диагностирования, где под шагом подразумевается следующее: через блок 1 программа загружает управляющую информацию, необходимую для выполнения текущего шага, в регистр 11 и параллельно через единичный вход запускается триггер 12 управления синхронизацией. Характерная особенность режима диагностирования - останов всех синхронизаторов (7-9) устройства, который осуществляется по приходу од3 , 14

ного из сигналов-сброса на .вход коммутатора 14 сигналов,

В указанном режиме диагностирования под действием управляюьцей информации, занесенной в регистр 11, создаются УСЛОВИЯ для запуска триггера 12 управления синхронизацией и прохода через второй элемент И 19 частоты от генератора 5 тактовых импульсов на входы синхронизаторов 7- 9, и все схемы устройства функционируют согласно их назначению и схемной реализации. При работе схем устройства вырабатываются сигналы сброса триггера 12 управления синхронизацией, которые прои,звольно подбираются из совокупности сигналов устройства при составлении диагностической программы. Сброшенный триггер

12управления синхронизацией останавливает работу синхронизирующих схем устройства и все проверяемые сигналы находятся в статичеком состоянии до следующего запуска триггера 12 управления синхронизацией. Обнуление этого триггера разрешает программе начинать опрос сигналов контролируемых точек устройства. Реформация о состоянии контролируемых сигналов устройства поступает от коммутатора

13контролируемых сигналов и блока 15 .триггеров запоминания динамических

сигналов через первый блок 1 приемопередатчиков в оперативную память процессора, где она обрабатывается диагностической программой. Принятая в оперативную память информация сравнивается программным путем с эталонной и в случае несовпадения формируется соответствующее ошибочной ситуации сообщение, выводимое на видеотерминал, входящий в состав ВК или на другое выходное устройство.

После получения сообщения, выводимого на. экран дисплея, о наличии неисправности устройства переключается в другой (динамический) режим диагностирования при помощи переключателя 24.

При включенном переключателе 24 сигнал логической единшда с выхода элемента НЕ 25 поступает на адресный вход коммутаора 14 сигналов сброса, блокируя сброс синхронизатора, а также поступает на первый вход элемен1 .

та И-НЕ 26, После загрузки диагностической программы в регистр хранения режимов контроля нулевой разряд данного регистра в виде сигнала логи„

че.скои единицы поступает на второй

вход элемента И-НЕ 26 и с его выхода сигнал логического нуля поступает на вход вычитания блока 2 регистров

(т,е. на входы регистра текущего адреса памяти и счетчиков байтов, входящих в блок 2 регистров), Поступление сигнала логического нуля на входы вычитания регистра текущего

адреса памяти и счетчика байтов запрещает в них изменение текущего адреса памяти и счета в счетчике байтов. При этом регистр текущего адреса памяти и счетчика байтов не могут

достичь переполнения, а это равно - сильно тому, что устройство выполняет, команды зап.иси или чтения зон бесконечной длины. Это позволяет при.наличии неисправности па основаНИИ полученной ранее информации (в. первом диагностическом режиме) о контрольной точке вести поиск неисправного элемента в динамическом режиме при помощи осциллографа, счетчика и других средств.

Формула изобретения

Устройство для сопряжения вычислительного комплекса с накопителем на магнитной ленте по авт. ев, №1 142839., отличающееся тем, что, с целью повышения быстродействия за счет сокращения времени локализации

неисправностей, в него-введены коммутатор режима диагностики, элемент И-НЕ, второй элемент НЕ, причем адресный вход коммутатора сигналов сброса соединен с выходом второго .

элемента НЕ и с первым входом элемента И-НЕ, второй вход которого соединен с выходом соответствующего разряда регистра хранения режимов контроля, а выход - с вычитающим входом блока регистров, вход второго элемента НЕ соединен с выходом коммутатора режима диагностики, первый и второй информационные входы которого подключены к шинам нулевого и единичного потенциалов устройства соответственно.

НМЛ ВК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Устройство для диагностики трехмашинного вычислительного комплекса | 1985 |

|

SU1383366A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для обмена информацией между эвм и магнитным накопителем | 1984 |

|

SU1218391A1 |

| Устройство для подключения абонентов к магистрали передачи данных | 1984 |

|

SU1254499A1 |

Изобретение относится к вычислительной технике, а именно к устройствам управления накопителями на магнитной ленте. Целью изобретения является сокращение времени локализации неисправности. Устройство содержит два блока приемопередатчиков, блок регистров, блок циклического контроля, блок хранения признаков состояния, генератор тактовых импульсов, блок синхронизации, регистр хранения режимов контроля,-триггер управления синхронизацией, коммутатор контролируемых сигналов, коммутатор сигналов сброса, блок триггеров запоминания динамических сигналов, блок управления синхронизацией, имитатор накопителя, коммутатор режима диагностирования, два элемента И, два элемента НЕ, элемент ИЛИ, элемент И-НЕ. I ил. (П

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-05—Подача