(Л

Выход

00 со

Изобретение относится к э.чектронз.мери- тельной и вычис.чительной технике и может быть использовано для преобразования в цифровом коде аналоговых сигналов, мгновенные значения которых занимают широкий динамический диапазон.

Цель изобретенияупронн ние устройства, повышение точности и быстродействия.

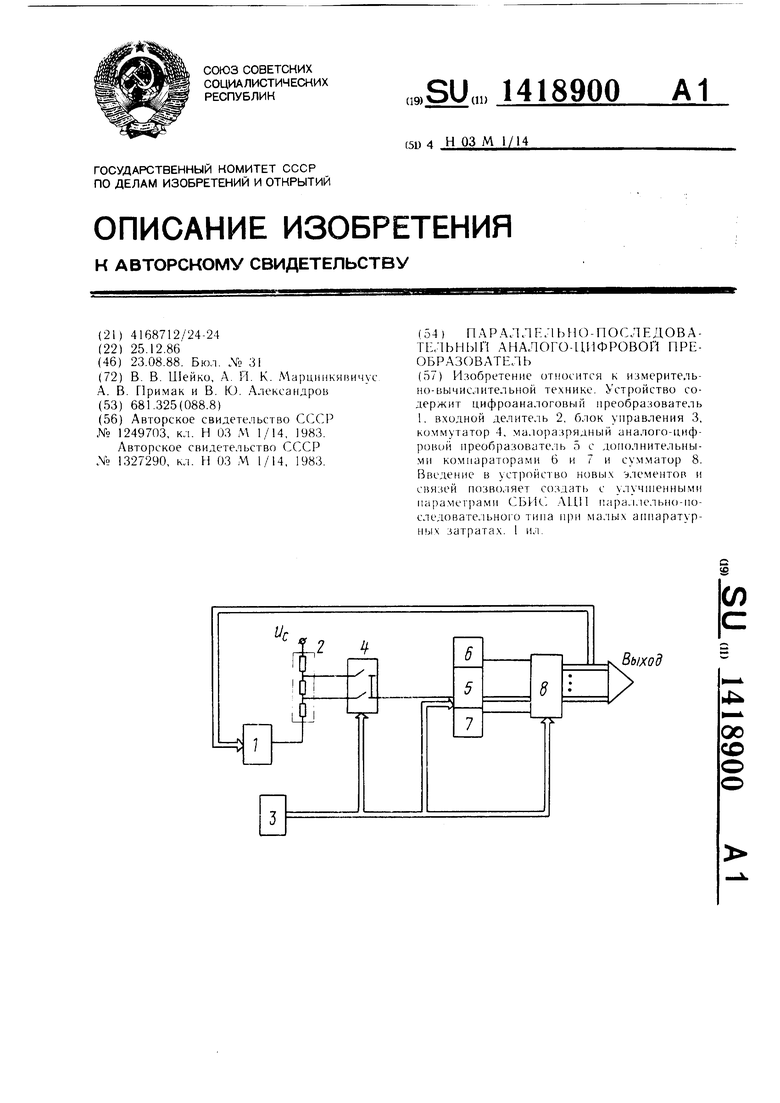

На чертеже представлена структурная схема предлагаемого параллельно-последовательного .

Предлагаемый преобразовате.пь содержит цифроаналоговый преобра.юнате.ль (ЦАП) 1, входной делитель 2 из трех последовательно соедипенных прецизионных резисторов, блок 3 управления, коммутатор 4, малоразрядный аналого-цифровой преоб- разоватео1ь (АЦП) 5 с дополнительными к()мпараторами 6 и 7 и сумматор 8.

Преобразователь работает следующим образом.

Перед каждым циклом преобразования коротким импульсом «Сброс блока 3 управ- .1ения устанавливается в «О код гг-ста)- П1ИХ разрядов сумматора 8, соответственно сгапан.ишасгся в «О выходное напряже- пне ЦАП 1. Резисторы делителя 2 подобраны таким образом, что па первом входе коммутатора 4 устанавливается папряжеппе

V, 2

l/x

В первом такте работы по фропг си.- нала «Такт Ь, форми)уемого блоком Л

управления, на вход .ЛЦП 5 подается си1 на;|

.-f-i

11а)а,1;1ельно-пос, 1едоватс. 1ьпый ana. ioio- 30 ци4 ровой пре()бразова1е.1ь, содержа1ций ре- зис1инпьп1 де,:1итель, первый вход которого является входной . а первый выход соединен с перньгм ин(}зо()мационпы.м нходс)м коммутатора, управляющие входы которою п(;дключепы к соответствуюпшм первым вхои и преобразуется им в код н-стар- 35 дам блока управлеппя, параллельный аналоших разрядов. При утом уровень cHi na, ia L ., устапавливается на входе резистивною де;1ителя 2 с помошью масп1табирук)пим о усилителя (не показан).

По срезу сигнала «Такт I код п-сгарп1и разрядов заносится в сумматор 8. В CBOKJ очередь, на выходе Ц.ЛП 1 устапавливается компепсиру юшее нипряжс нис o6 iaiiioii

110, 1ЯрНОСТИ

0,:.„ U.+MJ,.

40

45

I ()-пи1|)ровой преобраз(шате.1ь. пифроанало- oiu.iii п)еобразовате.,ть, отличающийся тем, что, с uc.ibK) упрощения устройства, новы- П(. 11пя точности н быстродействия в него виедоп сч мматс р, ин({)ор.мационные вход1 1 кот()К)() соединен) с соогветствуюп1ими ходами пара.-ь:1е, 1ЬП()1 о апалогч.) цифров()1(1 прсобраз(;вате, 1я, управ.аяюшие входы с соогнегс nyionuiMM BTOjibiMn вглходами б.юка управ. К Иия, а выходы являют с я выходпсн шиной, причем выходы стар1пих разрядов 1. осдинены (. соответствуюпи1ми вхол,ами цифроана, 1О1 ового | реобразовате,тя, выход которого соединен со )1м входо.м резис- Tiinnoio до.тптеля, второй выход которого пчдк. к второму информационному входу коммутатора, выход которого соединен с пп(|)ор.1аипонным па)а,т.тельного aiKi. i()i ()-uH()ip(uu)ro преобразовате,тя, р;и5.т51К1:1и1Й вхол. которого соединен с тьпм в)1ходом блока управления.

а на

при fвтором входе коммутатора 4

L ,-(,. лгл

L ,2

отсутствии О1пибк11 ,, где MJ

преооразпнании квапт П1ка,1ы .Л1II1 5.

Во в юром пикле работы ycipoHciisa по |1авлнк)п1сул сигна,1 «Такт 2 на вход

1 ..1М..|1 Н

.Vikill -) 1М

HllHHIill i

5

АЦП 5 поступает напряжение Ux2 и преоб разуется в код л-.младших разрядов.

По срезу сигнала «Такт 2 код п-млад- ших разрядов заносится в сумматор 8.

Динамические 11огреп ности преобразова ПИЯ корректируются с помощью дополнительных компараторов 6 и 7. Так, если к моменту второго преобразования входного сигнала / 6 iiar././(, то срабатывает компаратор б И производится вычитание единицы м.тадшего разряда в сумматоре 8. После установления нового значения Ихг , АЦП 5 формирует код л-м, 1адших разрядов.

В противном случае, когда /L iMn/ : С/6,/, с)абатывает дополнительный компаратор 7 и в сумматоре 8 производится сложепие единицы м.чадшего разряда. По окончании второго преобразования из сфор- мироваппого кода соответственно производится вычитание или сложение единиц младшего разряда относигельно старших раз- )ядов преобразования.

Пспользование изобретения позволяет создать экономичную и с высокими метро- , 1огическими пара.метрами СБПС АЦП па- рал.пельпо-последовательного типа при аппа- 1)атурпЬ)1х затратах, меньп1их на 25 30% чем в известном преобразователе.

(формула изобретения

11а)а,1;1ельно-пос, 1едоватс. 1ьпый ana. ioio- 0 ци4 ровой пре()бразова1е.1ь, содержа1ций ре- зис1инпьп1 де,:1итель, первый вход которого является входной . а первый выход соединен с перньгм ин(}зо()мационпы.м нходс)м коммутатора, управляющие входы которою п(;дключепы к соответствуюпшм первым вхо0

5

5 дам блока управлеппя, параллельный анало0

5

0

I ()-пи1|)ровой преобраз(шате.1ь. пифроанало- oiu.iii п)еобразовате.,ть, отличающийся тем, что, с uc.ibK) упрощения устройства, новы- П(. 11пя точности н быстродействия в него виедоп сч мматс р, ин({)ор.мационные вход1 1 кот()К)() соединен) с соогветствуюп1ими ходами пара.-ь:1е, 1ЬП()1 о апалогч.) цифров()1(1 прсобраз(;вате, 1я, управ.аяюшие входы с соогнегс nyionuiMM BTOjibiMn вглходами б.юка управ. К Иия, а выходы являют с я выходпсн шиной, причем выходы стар1пих разрядов 1. осдинены (. соответствуюпи1ми вхол,ами цифроана, 1О1 ового | реобразовате,тя, выход которого соединен со )1м входо.м резис- Tiinnoio до.тптеля, второй выход которого пчдк. к второму информационному входу коммутатора, выход которого соединен с пп(|)ор.1аипонным па)а,т.тельного aiKi. i()i ()-uH()ip(uu)ro преобразовате,тя, р;и5.т51К1:1и1Й вхол. которого соединен с тьпм в)1ходом блока управления.

I .;ь В .а Miiiri iii

KijpjK Ki lip О Крннцова 1(1.;|1исн11с

и )M()|lflC.. i;l I I I к I l.ll .-li 1Ц1(

г А1

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопительный "п"-разрядный сумматор | 1973 |

|

SU481035A1 |

| Устройство для контроля преобразователя угла поворота вала в код | 1988 |

|

SU1621173A1 |

| Генератор ступенчатого напряжения | 1986 |

|

SU1330734A1 |

| Стробоскопический измеритель временных интервалов | 1988 |

|

SU1656468A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1322364A1 |

| Устройство для решения р-мерных задачМАТЕМАТичЕСКОй физиКи | 1979 |

|

SU824216A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Устройство для сортировки чисел | 1988 |

|

SU1564611A1 |

Изобретение относится к измерительно-вычислительной технике. Устройство содержит цифроаналоговый преобразователь 1. входной делитель 2. блок управления 3, коммутатор 4, малоразрядный аналого-цифровой преобразователь 5 с дополнительными компараторами 6 и 7 и сумматор 8. Введение в устройство новых -: лементов и связей позволяет создать с улучшенными iiapaMerjiaMH СБИС- АЦ11 парал.кмьно-но- следовательного тина нри малых аннаратур- пых затратах. 1 ил.

| Устройство для аналого-цифрового преобразования | 1983 |

|

SU1249703A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1327290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-23—Публикация

1986-12-25—Подача