12

второй управляющие входы вто1зого коммутатора соединены соответс Т венно с вторым выходом блока управотения и с третьим входом блока управления и первым управляющим входом, третьего коммутатора5второй и третий 1зходы которого подключены соответственно к четвертому и пятому выходам блока управления дШестой и седьмой выходы кото- рого соединены с управляющими входами четвертого коммутатора, а восьмой и девятый выходы - соответственно с вторыми входами элементов И второй группы и третьими входами элементов И третьей группы, входы первого

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, в которых используется избыточное кодирование .данных.

Целью изобретения являетс;я повышение быстродействия устройства.

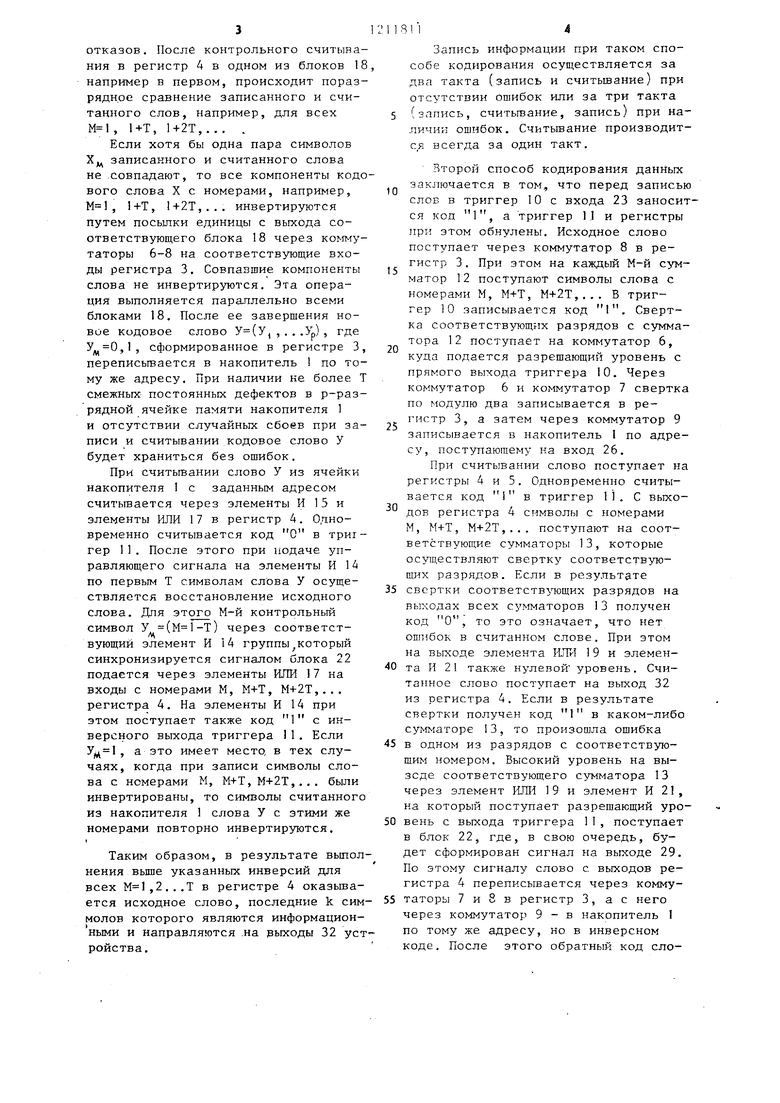

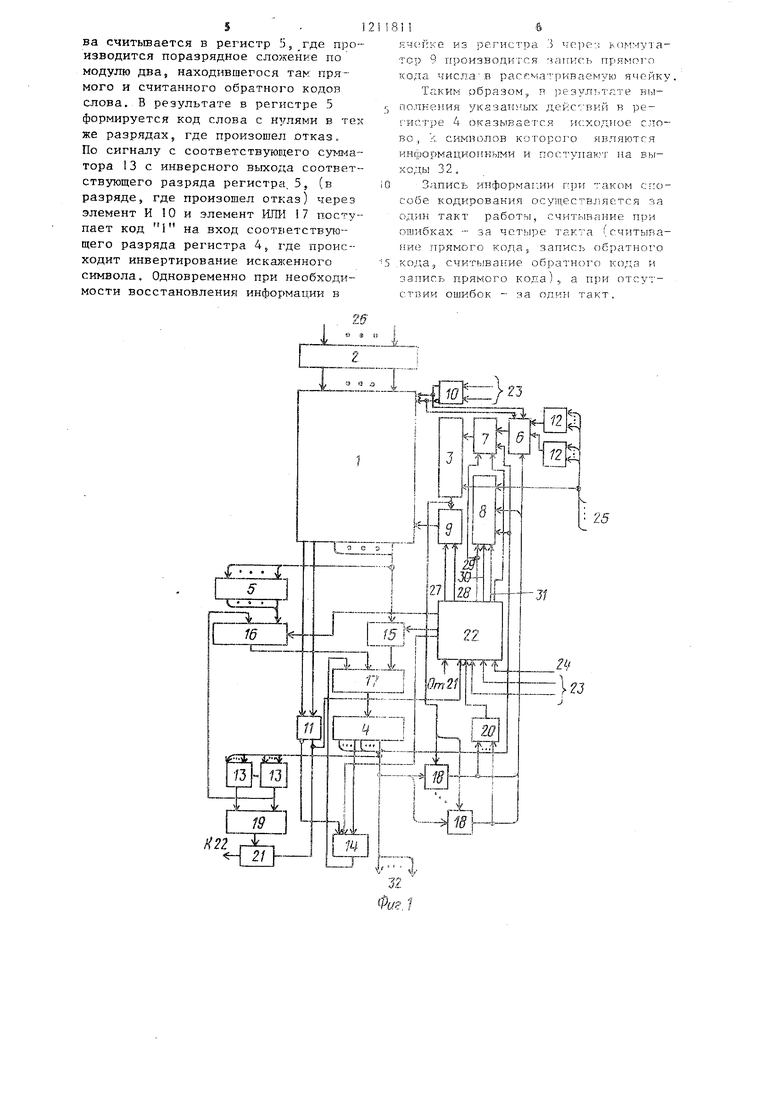

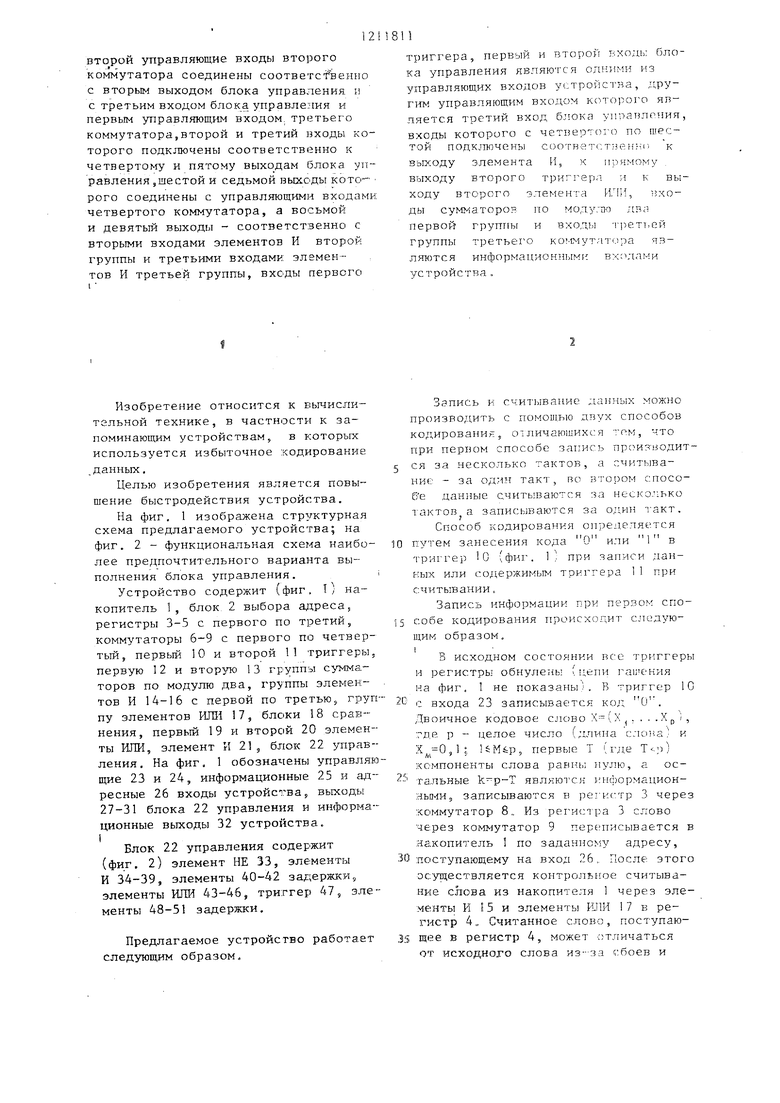

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема наиболее предпочтительного варианта выполнения блока управления.

Устройство содержит (фиг, li накопитель 1, блок 2 выбора адреса, регистры 3-5 с первого по третий, коммутаторы 6-9 с первого по четвертый, первый 10 и второй 1 триггеры, первую 12 и вторую 13 группы сумматоров по модулю два, группы элементов И 14-16 с первой по третью, группу элементов ИЛИ 7, блоки 18 сравнения, первый 19 и второй 20 элементы ИЛИ, элемент И 21, блок 22 управления. На фиг. 1 обозначены управляющие 23 и 24, информационные 25 и адресные 26 входы устройства, выходы 27-31 блока 22 управления и информационные выходы 32 устройства, i

Блок 22 управления содержит

(фиг. 2) элемент НЕ 33, элементЕЛ И 34-39, элементы 40-42 задержки, элементы ИЛИ 43-46, триггер 47 элементы 48-51 задержки.

Предлагаемое устройство работает следующим образом.

11

триггера, первый и второй входь; блока управления являются олнямн из управляющих входов устройства, дру- Г1-1М управляющим входом к(торого яп- ляется третий вход блока уппанлпяия входы которого с четвертого по шестой подключены соотнетстис- H-iii к вькоду элемента И, к прямому выходу второго триггерл и к выходу второго элемента ИЧИ. нхо- ды сумматоров по моду.тю днл первой группы и входы ч ретт.ей группы третьего коммутат(.)ра чз- ляются информапионпым -: вхолами устройства .

Запись и сч:итывание ;данных можно производить с помощью двух способов кодирования 5 отличающихся гем, что при первом способе запись произ водит- ся за несколько тактов, а считывание - за один такт, во втором спосо- б е данные считываются за несколько

Способ кодирования определяется

10 путем занесения кода

ЧУ

или

тригге 5 10 (фиг. 1 ; при записи даных или содержимым- триггера 1 1 при считывании.

Запись информации при первом спо- собе кодирования происходит следуюим образом,

i

В исходном состоянии вс:е Tpt-irrepbi

и регистрь обнулень; цепи 1 аи1ения на фиг. I не показаны). В триггер 10

с входа 23 записывается код. О .

Двоичное кодовое слово . . . .X р i, где р - целое число (длина cjioiia/ и ,1; 4Мбр, первые Т , где ) компоненты слова pafii-u.; нульэ, а остальные k-p-T являются 1;нформацион- HbB iHj записываются в регистр 3 через хоммутатор 8. Из 3 слово через коммутатор 9 переписывается в накопитель 1 по заданному адресу,

поступающему на вход 26,. После этого осуществляется контрольное считывание слова из накопителя 1 через элементы Р1 15 и элементы И1И 17 в регистр 4„ Считанное слово, поступаюшее в регистр 4, может с-тличаться от исходного слова из-за «-.боев и

отказов. После контрольного считывания в регистр 4 в одном из блоков 18 например в первом, происходит поразрядное сравнение записанного и считанного слов, например, для всех , И-Т, 14-21,... .

Если хотя бы одна пара символов Х записанного и считанного слова не .совпадают, то все компоненты кодового слова X с номерами, например, М, 1+Т, 1+2Т,... инвертируются путем посылки единицы с выхода соответствующего блока 18 через таторы 6-8 на соответствующие входы регистра 3, Совпавшие компоненты слова не инвертируются. Эта операция выполняется параллельно всеми блоками 18. После ее завершения новое кодовое слово У(У, , . . .Ур) , где ,1, сформированное в регистре 3 переписьгеается в накопитель 1 по тому же адресу. При наличии не более Т смежных постоянных дефектов в р-раз- рядной ячейке памяти накопителя 1 и отсутствии случайных сбоев при записи и считывании кодовое слово У будет храниться без ошибок.

При считывании слово У из ячейки накопителя 1 с заданным адресом считывается через элементы И 15 и элементы ИЛИ 17 в регистр 4. Одновременно считывается код О в триггер 11. После этого при иодаче управляющего сигнала на элементы И 14 по первьм Т символам слова У осуш;е- ствляется восстановление исходного слова. Для этого М-й контрольный символ У () через соответствующий элемент И 14 группы который синхронизируется сигналом блока 22 подается через элементы ИЛИ 17 на входы с номерами М, М+Т, М+2Т,... регистра 4. На элементы И 14 при этом поступает также код 1 с инверсного выхода триггера 11. Если , а это имеет место, в тех случаях, когда при записи символы слова с номерами М, М+Т,М+2Т,... были инвертированы, то символы считанного из накопителя 1 слова У с этими же номерами повторно инвертируются.

Таким образом, в результате выполнения вьшзе указанных инверсий для всех ,2...Т в регистре 4 оказьша- ется исходное слово, последние k сим молов которого являются информационными и направляются .на рьгходы 32 устройства.

5

0

5

1Я114

Запись информации при таком способе кодирования осуществляется за два такта (запись и считьшание) при отсутствии ошибок или за три такта 5 (запись, считывание, запись) при наличии ошибок. Считывание производится всегда за один такт.

Второй способ кодирования данных заключается в том, что перед записью слов в триггер 10 с входа 23 заносится код 1, а триггер 1.1 и регистры при этом обнулены. Исходное слово поступает через коммутатор 8 в регистр 3. При этом на каждый М-й сумматор 12 поступают символы слова с номерами М, M-t-T, М+2Т,... В триггер 10 записывается код 1. Свертка соответствующих разрядов с тора 12 поступает на комь1утатор 6, куда подается разрешающий уровень с прямого выхода триггера 10. Через коммутатор 6 и коммутатор 7 свертка по модулю два записывается в регистр 3, а затем через коммутатор 9 записывается в накопитель 1 по адресу, поступающему на вход 26.

При считывании слово поступает на регистры 4 и 5. Одновременно считывается код 1 в триггер П. С выходов регистра 4 символы с номерами М, М+Т, М+2Т,... поступают на соответствующие сумматоры 13, которые осутцествляют свертку соответствующих разрядов. Если в результате 5 свертки соответств тощих разрядов на выходах всех сз мматоров 13 получен код О, то это означает, что нет ощибок в считанном слове. При этом на выходе элемента IITR-I 19 и элемен- 0 та И 21 также нулевой уровень. Считанное слово поступает на выход 32 из регистра 4. Если в результате свертки получен код 1 в каком-либо сумматоре 13, то произошла ошибка 5 в одном из разрядов с соответствующим номером. Высокий уровень на вы- зсде соответствующего сумматора 13 через элемент I-LTM 19 и элемент И 21, на который поступает разрешающий уро- 0 вень с выхода триггера 11, поступает в блок 22, где, в свою очередь, будет сформирован сигнал на выходе 29. По этому сигналу слово с выходов регистра 4 переписывается через комму- 5 таторы 7 и 8 в регистр 3, а с него через коммутатор 9 - в накопитель 1 по тому же адресу, но в инверсном коде. После этого обратный код ело-

S . ва считьшается в регистр 5, где производится поразрядное сложение по модулю два, находившегося тан прямого и считанного обратного кодов слова. В результате в регистре 5 формируется код слова с нулями в тех же разрядах, где произошел отказ. По сигналу с соответствующего сумма-тора 13 с инверсного выхода соответ-- ствующего разряда регистра. 5. (в разряде, где произошел отказ) через элемент И 10 и элемент ИЛИ 7 поступает код 1 на вход соответствующего разряда регистра 4, где происходит инвертирование искалсенного символа. Одновременно при необходимости восстановления информации в

.1.

lIi..,rf7ffl::::k3

3

q

кода числа В расгматркваемую ячейку. Таким образом, в 15езул1,тгте BI,Iполнеиия указан: ых действий в ре- г ист ие 4 оказывает ся исходное слово , k символов которог о являются информационными и посгупакт на выходы 32,

Запись информа1:ии при таком сг о- собе кодирования осуществляется за один такт работы, считывание при ошибках - за четыре такта считывание прямого кода, запись обратного

KOfia, считывание обратного кода и запись прямого кода,, а при отсу;-- ствии ошибок - за один такт.

«7

: 25

Редактор л. Кастран

Заказ 647/57Тираж 544Подписное

ВНИИГГИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель В. Гордонова

Техред Л.Микеш Корректор А. Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU928423A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-18—Подача