СП

lN5

N9

CD

СО

Изобретение относится к вычислительной технике и может быть использовано в интегральных микросхемах на элементах инжекционной логи ки.

Цель изобретения - повьппение быстродействия сумматора и сокращение площади, занимаемой сумматором.

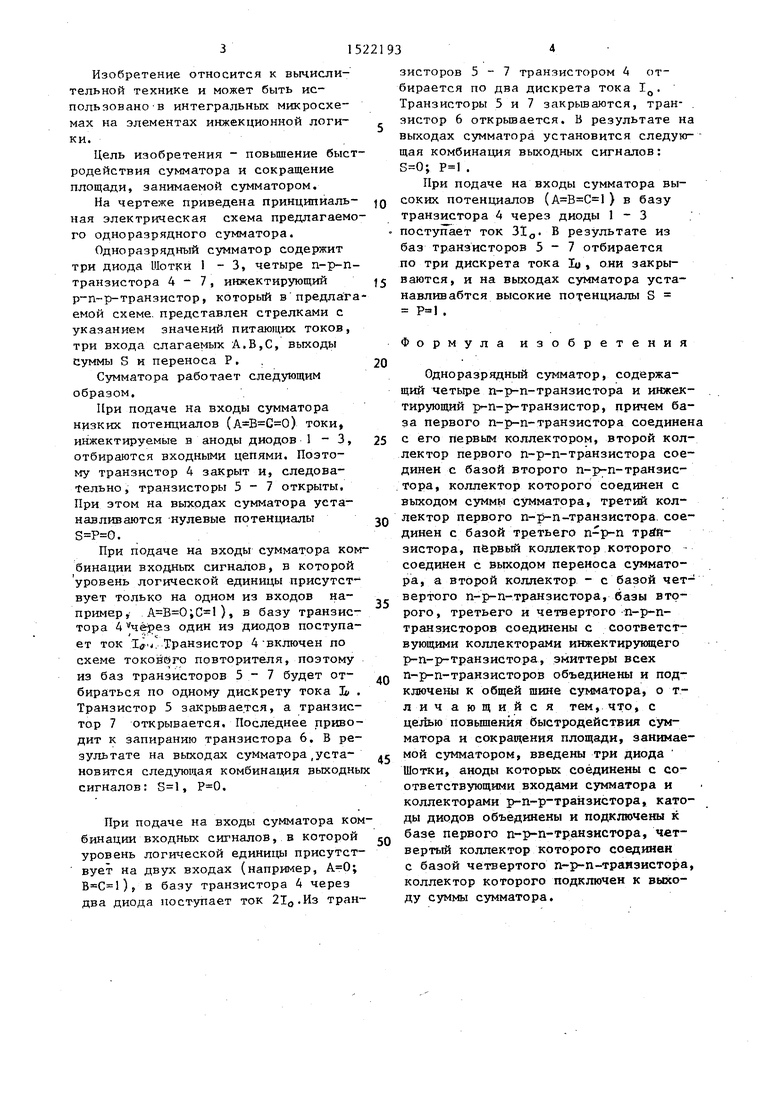

На чертеже приведена принципиаль- ная электрическая схема предлагаемого одноразрядного сумматора.

Одноразрядный сумматор содержит три диода Шотки I - 3, четыре п-р-п- транзистора 4-7, инжектирующий р-п-р-транзистор, который в предлагаемой схеме, представлен стрелками с указанием значений питающих токов, три входа слагаемых А,В,С, выходы суммы S и переноса Р. ,

Сумматора работает следующим образом.

При подаче на входы сумматора низких потенциалов () токи инжектируемые в аноды диодов 1 - 3, отбираются входными цепями. Поэтому транзистор 4 закрыт и, следовательно, транзисторы 5-7 открыты. При этом на выходах сумматора устанавливаются нулевые потенциалы .

При подаче на входы сумматора комбинации входных сигналов, в которой уровень логической единицы присутствует только на одном из входов на- примеру ), в базу транзистора 4 один из диодов поступает ток Itf.л Транзистор 4включен по схеме токовйгр повторителя, поэтому из баз транзисторов 5-7 будет от- бираться по одному дискрету тока It, , Транзистор 5 закрывается, а транзистор 7 открывается. Последнее приводит к запиранию транзистора 6. В результате на выходах сумматора,уста- новится следующая комбинация выходнь сигналов: , .

При подаче на входы сумматора комбинации входных сигналов, в которой уровень логической единицы присутствует на двух входах (например, ), в базу транзистора 4 через два диода поступает ток 21о.Из тран

,

g

5 0

5 Q

Q ,с

Q

5

зисторов 5-7 транзистором 4 отбирается по два дискрета тока 1. Транзисторы 5 и 7 закрьшаются, тран- . зистор 6 открьшается. В результате на выходах сзтматора установится следую-- щая комбинация выходных сигналов: .

При подаче на входы сумматора высоких потенциалов () в базу транзистора 4 через диоды 1-3 поступает ток З. В результате из баз транзисторов 5-7 отбирается по три дискрета тока « , они закрываются, и на выходах сумматора уста- навливабтся высокие потенциалы S .

Формула изобретения

Одноразрядный сумматор, содержащий четыре п-р-п-транзистора и инжектирующий р-п-р-транзистор, причем база первого п-р-п-транзистора соединена с его первым коллектором, второй коллектор первого п-р-п-транзистора соединен с базой второго п-р-п-транзис- .тора, коллектор которого соединен с выходом суммы сумматора, третий коллектор первого п-р-п-транзистора, соединен с базой третьего п-р-п трйй- зистора, первый коллектор которого - соединен с выходом переноса сумматора, а второй коллектор - с базой четвертого п-р-п-транзистора, базы второго, третьего и четвертого п-р-п- транзисторов соединены с соответствующими коллекторами инжектирукмдего р-п-р-транзистора, эмиттеры всех п-р-п-транзисторов объединены и подключены к общей шине сумматора, о т- л и ч а ю щ и и с я тем, что, с целью повьшенйя быстродействия сумматора и сокращения площади, занимаемой сзгмматором, введены три диода Шотки, аноды которых соединены с соответствующими входами сумматора и коллекторами р-п-р-транзистора, катоды диодов объединены и подключены к базе первого п-р п-транзнстора, четвертый коллектор которого соединен с базой четвертого п-р-п-траизистора, коллектор которого подключен к выходу суммы сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1986 |

|

SU1335984A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Мажоритарный элемент И @ Л типа | 1986 |

|

SU1406777A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

Изобретение относится к вычислительной технике и может быть использовано в интегральных микросхемах на элементах инжекционной логики. Целью изобретения является повышение быстродействия сумматора и сокращение площади, занимаемой сумматором. Поставленная цель достигается введением трех диодов Шотки 1,2,3 на входах сумматора, содержащего четыре п-р-п транзистора 4,5,6,7 и инжектирующего р-п-р транзистора. 1 ил.

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шагурин И.И.Проектирование цифровых микросхем на элементах инжекцион- ной логики | |||

| М.: Радио и связь, 1984, с.138, рис.4,9.а | |||

| Одноразрядный сумматор | 1982 |

|

SU1043637A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1988-03-01—Подача