t Изобретение относится к устройствам вычислительной техники и может быть использовано при построении микропроцессорных систем.

Цель изобретения - повышение быстродействия.

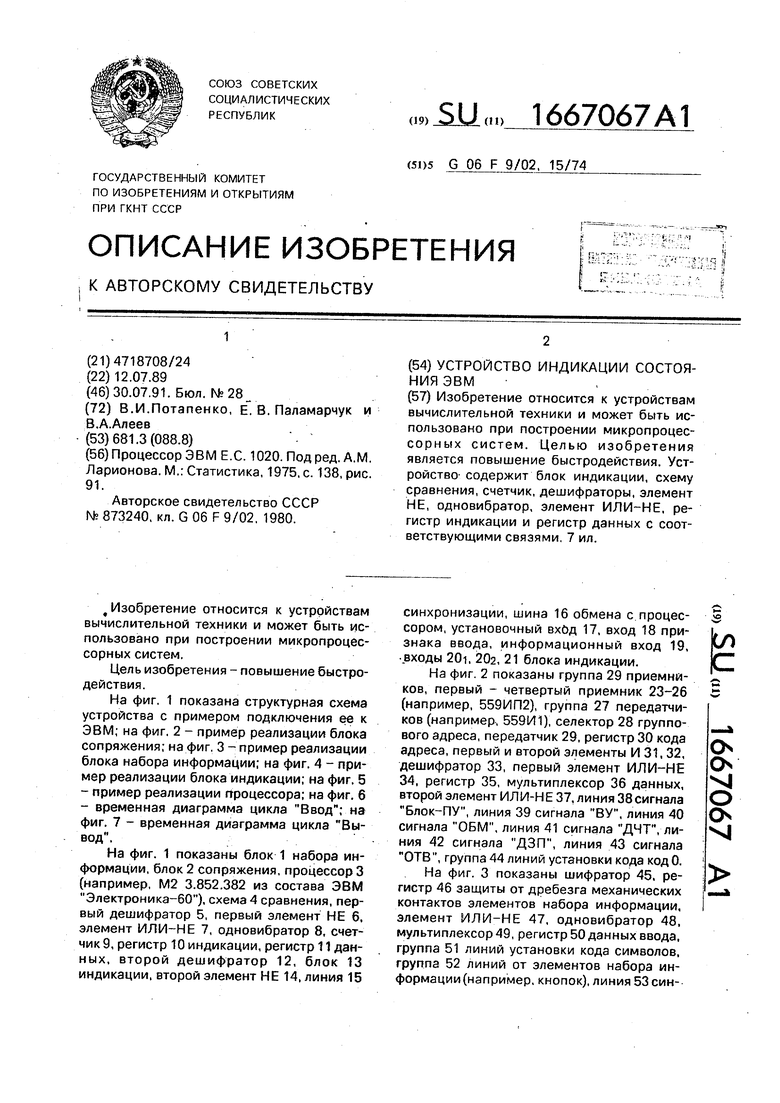

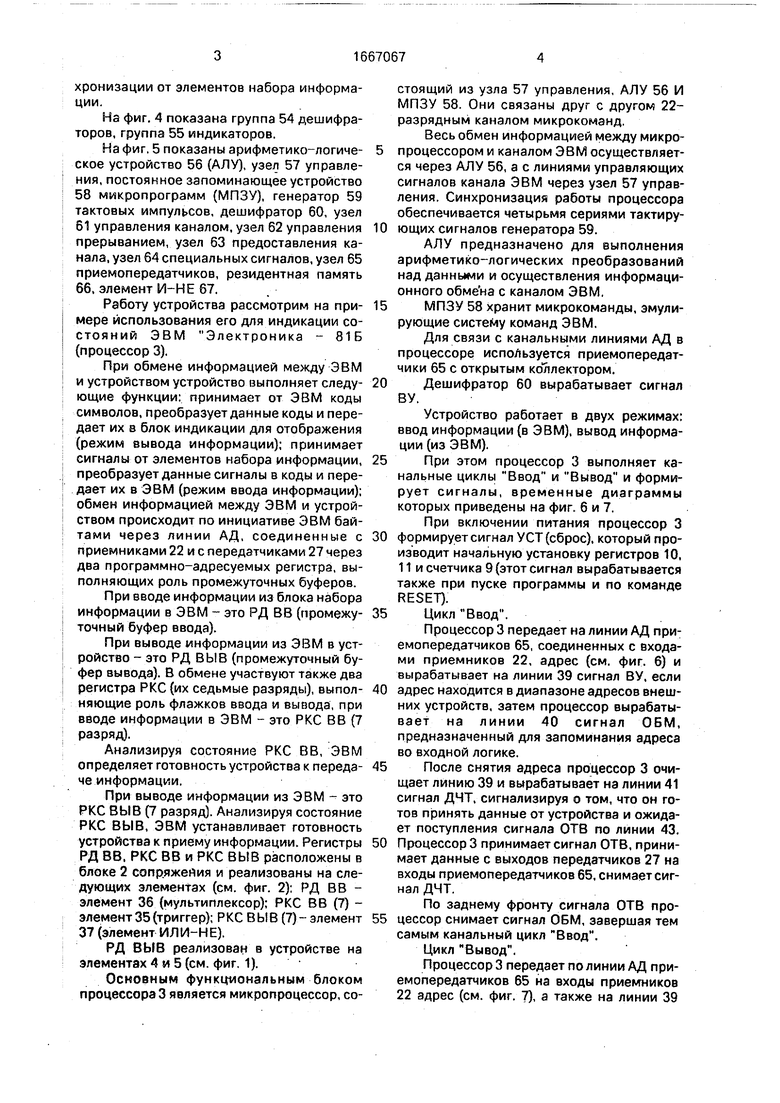

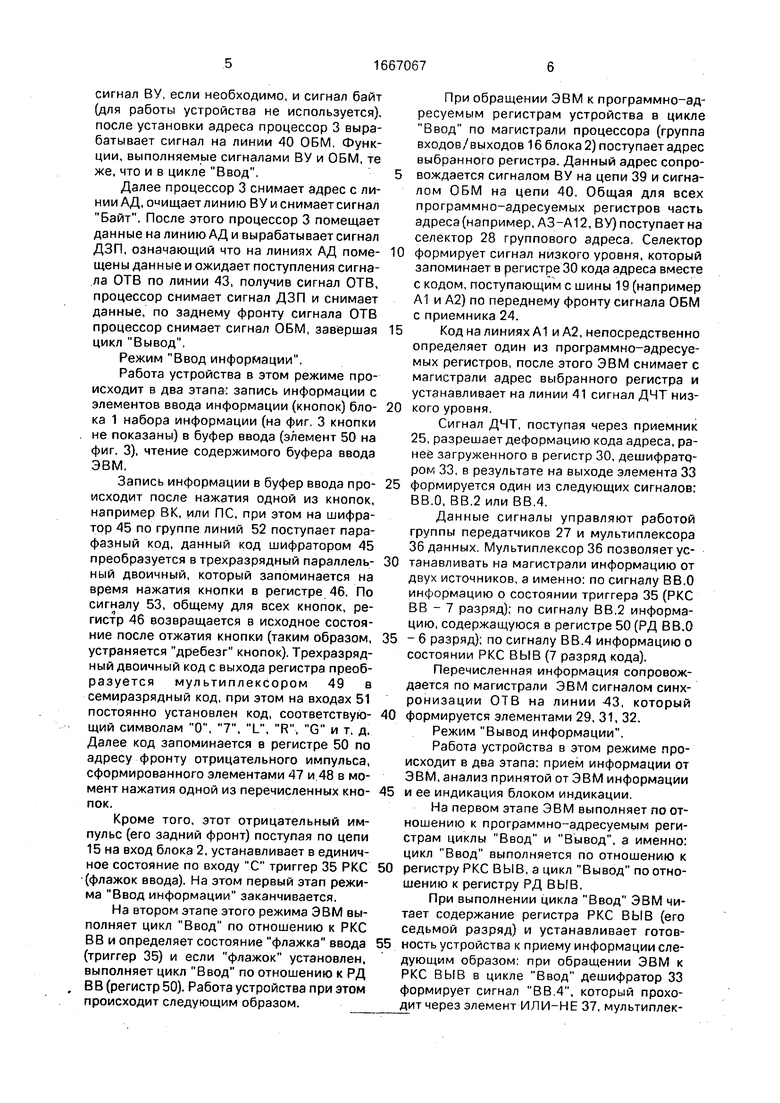

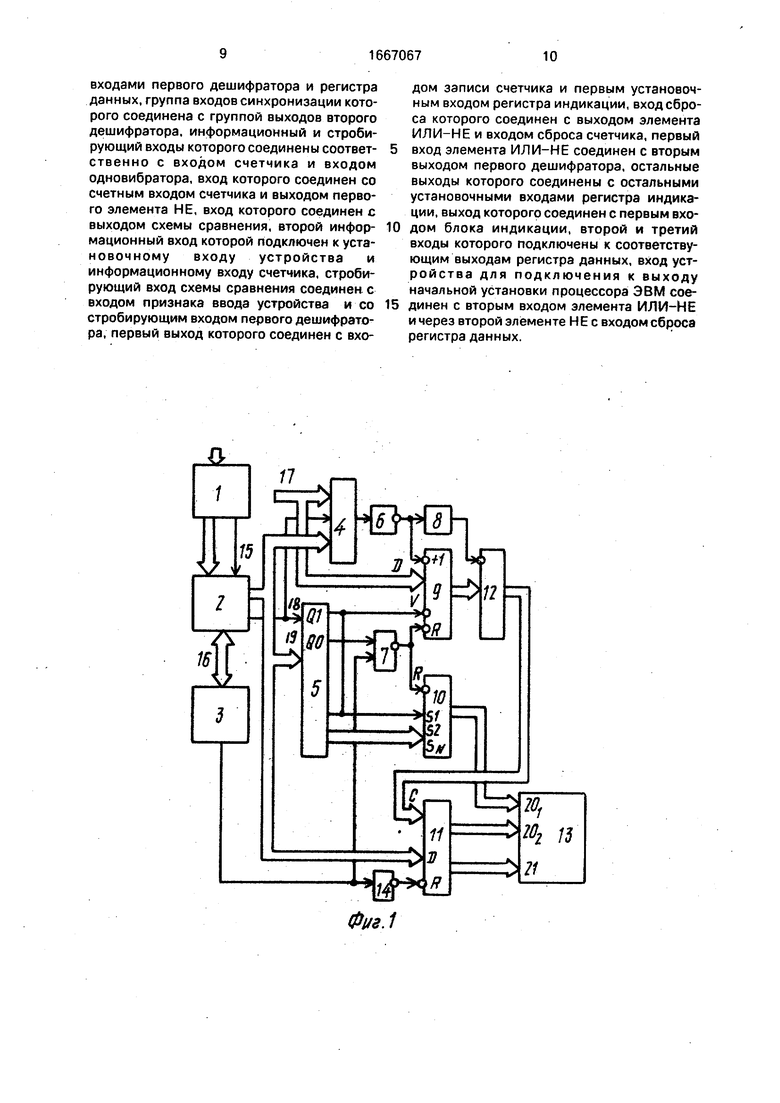

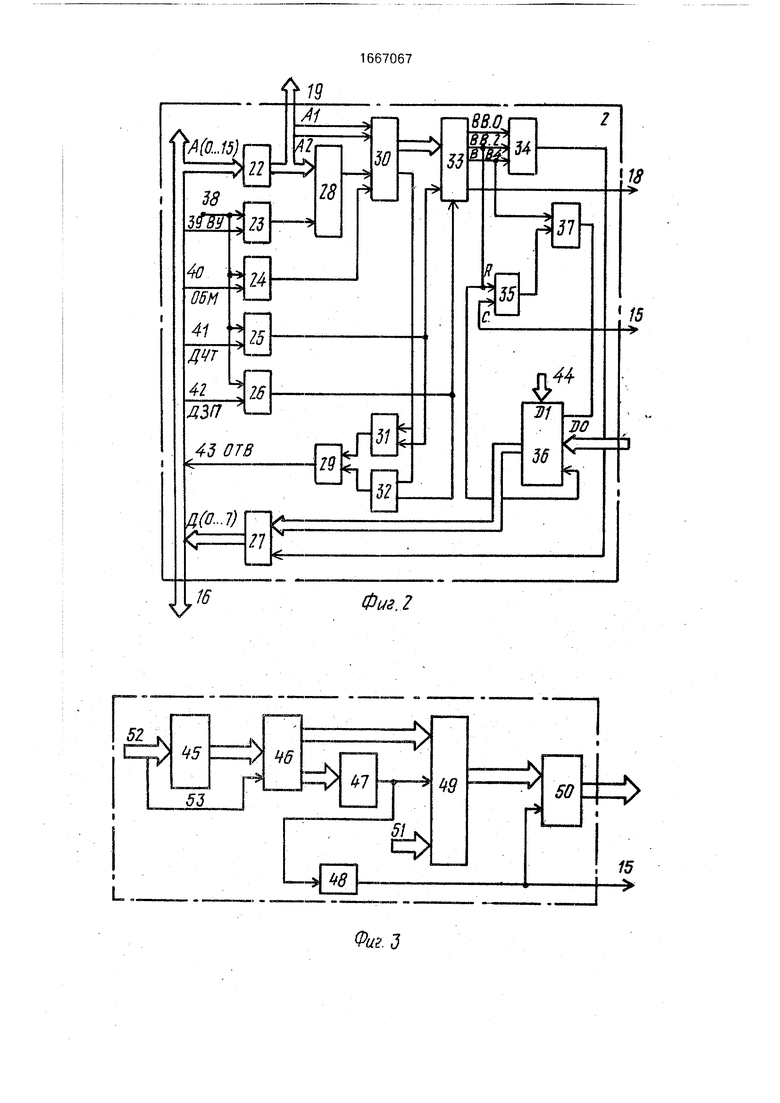

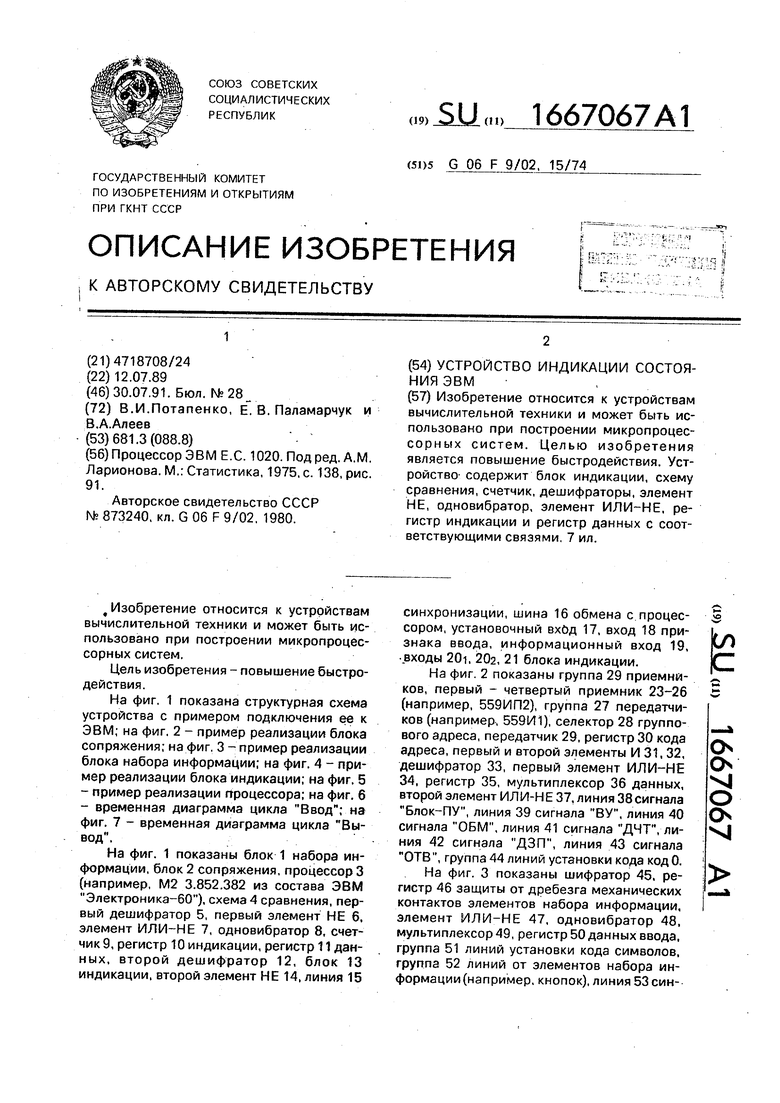

На фиг. 1 показана структурная схема устройства с примером подключения ее к ЭВМ; на фиг. 2 - пример реализации блока сопряжения; на фиг. 3 - пример реализации блока набора информации; на фиг, 4 - пример реализации блока индикации; на фиг. 5

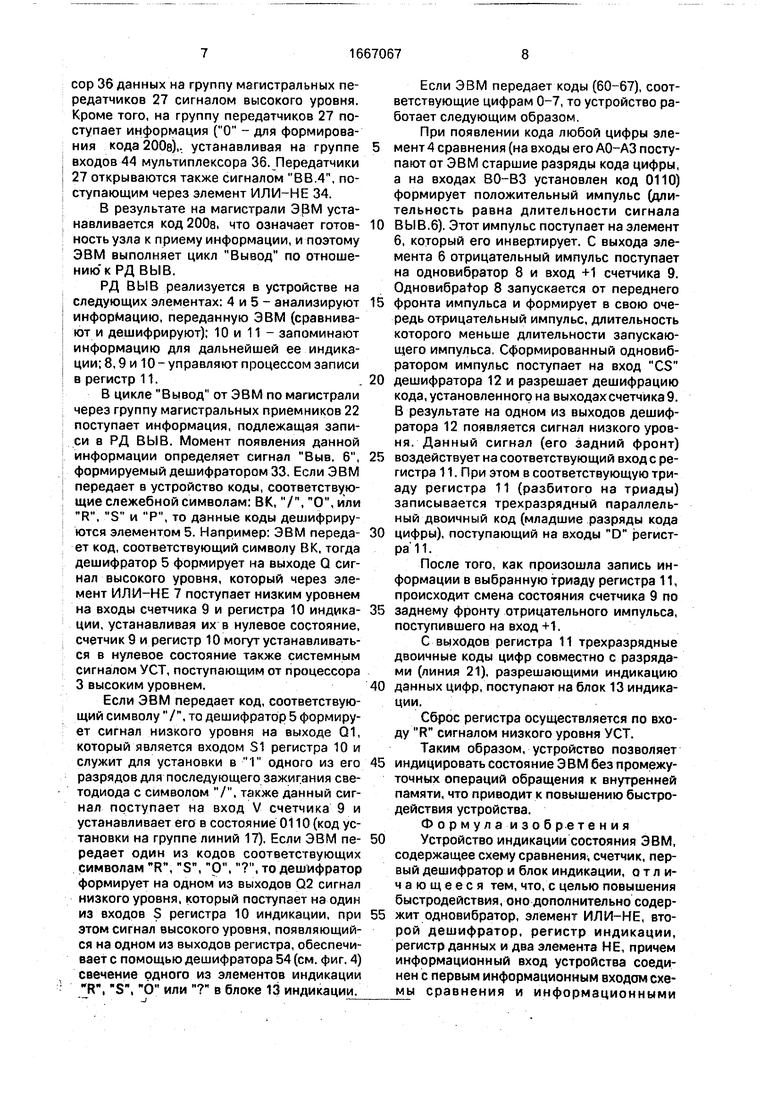

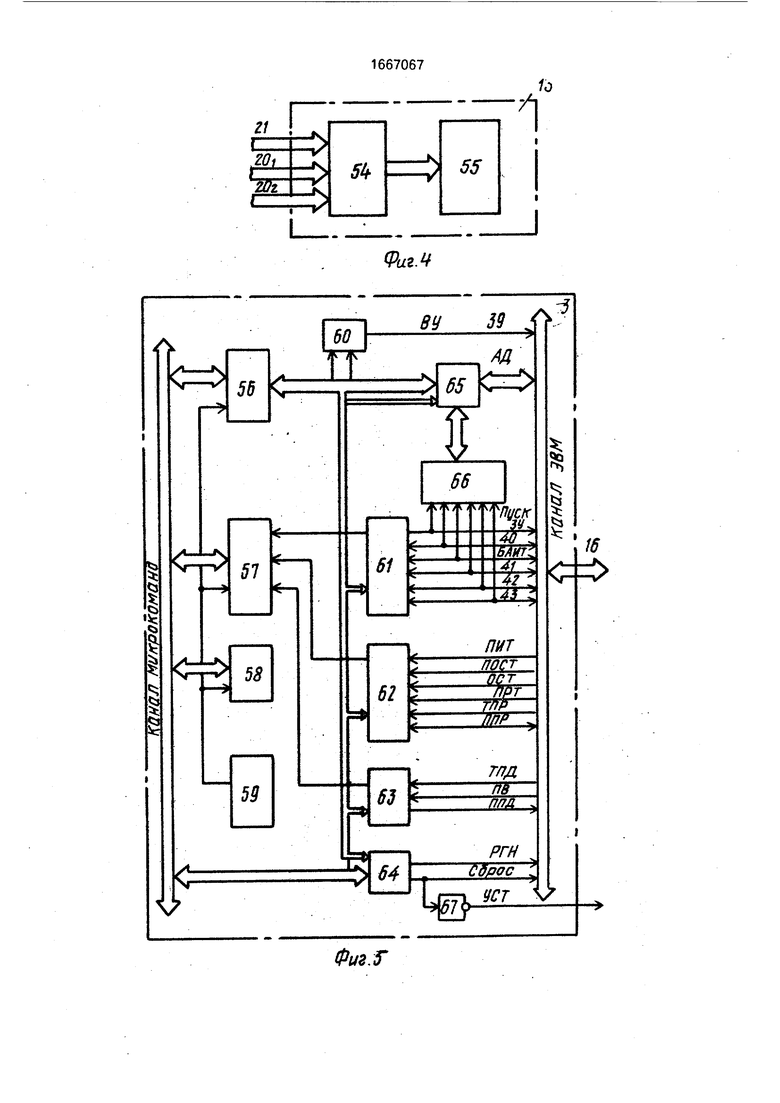

-пример реализации процессора; на фиг. 6

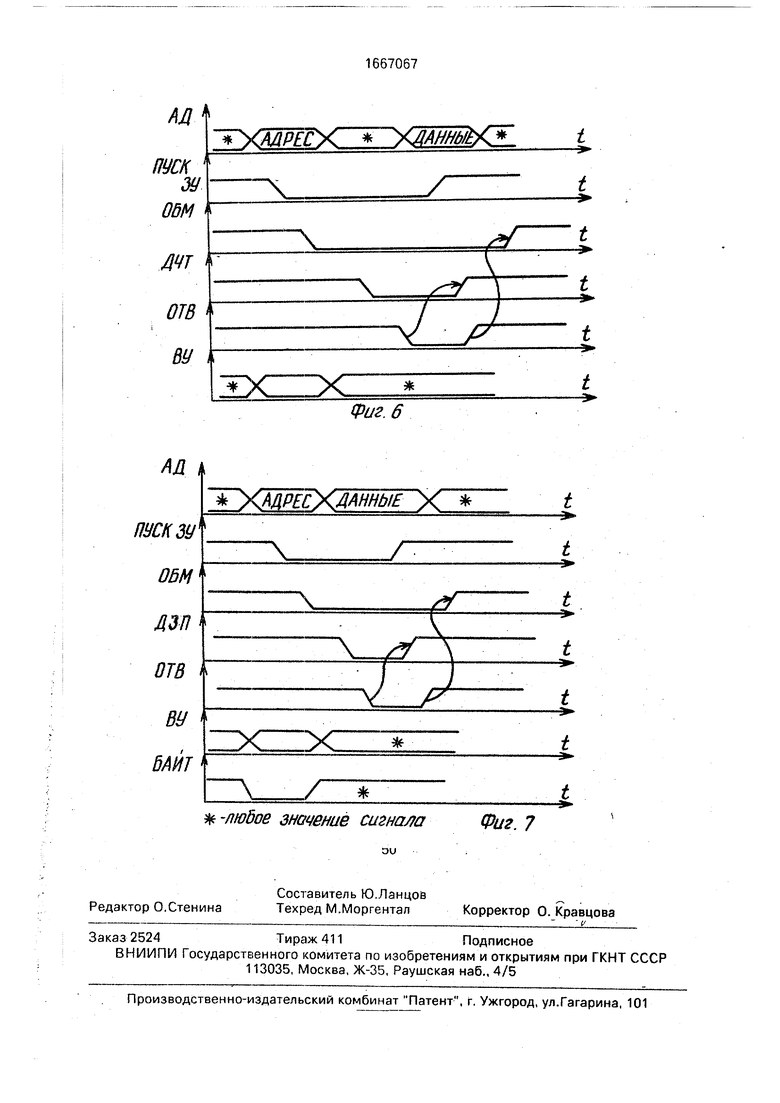

-временная диаграмма цикла на фиг. 7 - временная диаграмма цикла Вывод.

На фиг. 1 показаны блок 1 набора информации, блок 2 сопряжения, процессор 3 (например, М2 3.852.382 из состава ЭВМ Электроника-60), схема 4 сравнения, первый дешифратор 5, первый элемент НЕ б, элемент ИЛИ-НЕ 7, одновибратор 8, счетчик 9, регистр 10 индикации, регистр 11 дан- ных, второй дешифратор 12, блок 13 индикации, второй элемент НЕ 14, линия 15

синхронизации, шина 16 обмена с процессором, установочный вход 17, вход 18 признака ввода, информационный вход 19, входы 20i, 202, 21 блока индикации.

На фиг 2 показаны группа 29 приемников, первый - четвертый приемник 23-26 (например, 559ИП2), группа 27 передатчиков (например, 559И1), селектор 28 группового адреса, передатчик 29, регистр 30 кода адреса, первый и второй элементы И 31, 32, дешифратор 33, первый элемент ИЛИ-НЕ 34, регистр 35, мультиплексор 36 данных, второй элемент ИЛИ-НЕ 37, линия 38 сигнала Блок-ПУ, линия 39 сигнала ВУ, линия 40 сигнала ОБМ, линия 41 сигнала ДЧТ, линия 42 сигнала ДЗП, линия 43 сигнала ОТВ, группа 44 линий установки кода код 0.

На фиг. 3 показаны шифратор 45, регистр 46 защиты от дребезга механических контактов элементов набора информации, элемент ИЛИ-НЕ 47, одновибратор 48, мультиплексор 49, регистр 50 данных ввода, группа 51 линий установки кода символов, группа 52 линий от элементов набора ин- формации(например, кнопок), линия 53син&

Ј

О

ON XI О

О х|

хронизации от элементов набора информации.

На фиг. 4 показана группа 54 дешифраторов, группа 55 индикаторов.

На фиг. 5 показаны арифметико-логическое устройство 56 (АЛУ), узел 57 управления, постоянное запоминающее устройство 58 микропрограмм (МПЗУ), генератор 59 тактовых импульсов, дешифратор 60, узел 61 управления каналом, узел 62 управления прерыванием, узел 63 предоставления канала, узел 64 специальных сигналов, узел 65 приемопередатчиков, резидентная память 66, элемент И-НЕ 67.

Работу устройства рассмотрим на примере использования его для индикации состояний ЭВМ Электроника - 81Б (процессор 3).

При обмене информацией между ЭВМ и устройством устройство выполняет следующие функции: принимает от ЭВМ коды символов, преобразует данные коды и передает их в блок индикации для отображения (режим вывода информации); принимает сигналы от элементов набора информации, преобразует данные сигналы в коды и передает их в ЭВМ (режим ввода информации); обмен информацией между ЭВМ и устройством происходит по инициативе ЭВМ байтами через линии АД, соединенные с приемниками 22 и с передатчиками 27 через два программно-адресуемых регистра, выполняющих роль промежуточных буферов. При вводе информации из блока набора информации в ЭВМ - это РД ВВ (промежуточный буфер ввода).

При выводе информации из ЭВМ в устройство - это РД ВЫВ (промежуточный буфер вывода). В обмене участвуют также два регистра РКС (их седьмые разряды), выполняющие роль флажков ввода и вывода, при вводе информации в ЭВМ - это РКС ВВ (7 разряд).

Анализируя состояние РКС ВВ, ЭВМ определяет готовность устройства к передаче информации.

При выводе информации из ЭВМ - это РКС ВЫВ (7 разряд). Анализируя состояние РКС ВЫВ, ЭВМ устанавливает готовность устройства к приему информации. Регистры РД ВВ. РКС ВВ и РКС ВЫВ расположены в блоке 2 сопряжения и реализованы на следующих элементах (см. фиг. 2); РД ВВ - элемент 36 (мультиплексор); РКС В В (7) - элемент 35 (триггер); РКС ВЫВ (7)- элемент 37 (элемент ИЛИ-НЕ).

РД ВЫВ реализован в устройстве на элементах 4 и 5 (см. фиг. 1).

Основным функциональным блоком процессора 3 является микропроцессор, состоящий из узла 57 управления, АЛУ 56 И МПЗУ 58. Они связаны друг с другом 22- разрядным каналом микрокоманд.

Весь обмен информацией между микропроцессором и каналом ЭВМ осуществляется через АЛУ 56, а с линиями управляющих сигналов канала ЭВМ через узел 57 управления. Синхронизация работы процессора обеспечивается четырьмя сериями тактиру0 ющих сигналов генератора 59.

АЛУ предназначено для выполнения арифметико-логических преобразований над данными и осуществления информационного обмена с каналом ЭВМ.

5МПЗУ 58 хранит микрокоманды, эмулирующие систему команд ЭВМ.

Для связи с канальными линиями АД в процессоре используется приемопередатчики 65 с открытым коллектором.

0 Дешифратор 60 вырабатывает сигнал ВУ.

Устройство работает в двух режимах; ввод информации (в ЭВМ), вывод информации (из ЭВМ).

5При этом процессор 3 выполняет канальные циклы Ввод и Вывод и формирует сигналы, временные диаграммы которых приведены на фиг. 6 и 7.

При включении питания процессор 3

0 формирует сигнал УСТ (сброс), который производит начальную установку регистров 10, 11 и счетчика 9 (этот сигнал вырабатывается также при пуске программы и по команде RESET).

5Цикл Ввод.

Процессор 3 передает на линии АД приемопередатчиков 65, соединенных с входами приемников 22, адрес (см. фиг. 6) и вырабатывает на линии 39 сигнал ВУ, если

0 адрес находится в диапазоне адресов внешних устройств, затем процессор вырабатывает на линии 40 сигнал ОБМ, предназначенный для запоминания адреса во входной логике.

5 После снятия адреса процессор 3 очищает линию 39 и вырабатывает на линии 41 сигнал ДЧТ, сигнализируя о том. что он готов принять данные от устройства и ожидает поступления сигнала ОТВ по линии 43.

0 Процессор 3 принимает сигнал ОТВ, принимает данные с выходов передатчиков 27 на входы приемопередатчиков 65, снимает сигнал ДЧТ.

По заднему фронту сигнала ОТВ про5 цессор снимает сигнал ОБМ, завершая тем самым канальный цикл Ввод. Цикл Вывод.

Процессор 3 передает по линии АД приемопередатчиков 65 на входы приемников 22 адрес (см. фиг. 7), а также на линии 39

сигнал ВУ, если необходимо, и сигнал байт (для работы устройства не используется), после установки адреса процессор 3 вырабатывает сигнал на линии 40 ОБМ. Функции, выполняемые сигналами ВУ и ОБМ, те же, что и в цикле Ввод.

Далее процессор 3 снимает адрес с линии АД, очищает линию ВУ и снимает сигнал Байт. После этого процессор 3 помещает данные на линию АД и вырабатывает сигнал ДЗП, означающий что на линиях АД помещены данные и ожидает поступления сигнала ОТВ по линии 43, получив сигнал ОТВ, процессор снимает сигнал ДЗП и снимает данные, по заднему фронту сигнала ОТВ процессор снимает сигнал ОБМ, завершая цикл Вывод.

Режим Ввод информации.

Работа устройства в этом режиме происходит в два этапа: запись информации с элементов ввода информации (кнопок) блока 1 набора информации (на фиг. 3 кнопки не показаны) в буфер ввода (элемент 50 на фиг. 3), чтение содержимого буфера ввода ЭВМ.

Запись информации в буфер ввода происходит после нажатия одной из кнопок, например ВК, или ПС, при этом на шифратор 45 по группе линий 52 поступает пара- фазный код, данный код шифратором 45 преобразуется в трехразрядный параллельный двоичный, который запоминается на время нажатия кнопки в регистре 46. По сигналу 53, общему для всех кнопок, регистр 46 возвращается в исходное состояние после отжэтия кнопки (таким образом, устраняется дребезг кнопок). Трехразрядный двоичный код с выхода регистра преобразуется мультиплексором 49 в семиразрядный код, при этом на входах 51 постоянно установлен код, соответствующий символам О, 7, L, R, G и т, д. Далее код запоминается в регистре 50 по адресу фронту отрицательного импульса, сформированного элементами 47 и 48 в момент нажатия одной из перечисленных кнопок.

Кроме того, этот отрицательный импульс (его задний фронт) поступая по цепи 15 на вход блока 2, устанавливает в единичное состояние по входу С триггер 35 РКС (флажок ввода). На этом первый этап режима Ввод информации заканчивается.

На втором этапе этого режима ЭВМ выполняет цикл Ввод по отношению к РКС ВВ и определяет состояние флажка ввода (триггер 35) и если флажок установлен, выполняет цикл Ввод по отношению к РД В В (регистр 50). Работа устройства при этом происходит следующим образом.

При обращении ЭВМ к программно-адресуемым регистрам устройства в цикле Ввод по магистрали процессора (группа входов/выходов 16 блока 2) поступает адрес выбранного регистра. Данный адрес сопро- 5 вождается сигналом ВУ на цепи 39 и сигналом ОБМ на цепи 40. Общая для всех программно-адресуемых регистров часть адреса (например, A3-А 12, ВУ) поступает на селектор 28 группового адреса. Селектор 10 формирует сигнал низкого уровня, который запоминает в регистре 30 кода адреса вместе с кодом, поступающим с шины 19 (например А1 и А2) по переднему фронту сигнала ОБМ с приемника 24.

15Код на линиях А1 и А2, непосредственно

определяет один из программно-адресуемых регистров, после этого ЭВМ снимает с магистрали адрес выбранного регистра и устанавливает на линии 41 сигнал ДЧТ низ- 0 кого уровня.

Сигнал ДЧТ, поступая через приемник 25, разрешает деформацию кода адреса, ранее загруженного в регистр 30, дешифратором 33, в результате на выходе элемента 33 5 формируется один из следующих сигналов: ВВ.О, ВВ.2 или ВВ 4.

Данные сигналы управляют работой группы передатчиков 27 и мультиплексора 36 данных. Мультиплексор 36 позволяет ус- 0 танавливать на магистрали информацию от двух источников, а именно: по сигналу ВВ.О информацию о состоянии триггера 35 (РКС ВВ - 7 разряд); по сигналу ВВ.2 информацию, содержащуюся в регистре 50 (РД ВВ.О 5-6 разряд); по сигналу ВВ.4 информацию о состоянии РКС ВЫВ (7 разряд кода).

Перечисленная информация сопровождается по магистрали ЭВМ сигналом синхронизации ОТВ на линии 43, который 0 формируется элементами 29, 31, 32. Режим Вывод информации. Работа устройства в этом режиме происходит в два этапа: прием информации от ЭВМ, анализ принятой от ЭВМ информации 5 и ее индикация блоком индикации.

На первом этапе ЭВМ выполняет по отношению к программно-адресуемым регистрам циклы Ввод и Вывод, а именно: цикл Ввод выполняется по отношению к 0 регистру РКС ВЫВ, а цикл Вывод по отношению к регистру РД ВЫВ.

При выполнении цикла Ввод ЭВМ читает содержание регистра РКС ВЫВ (его седьмой разряд) и устанавливает готов- 5 ность устройства к приему информации следующим образом при обращении ЭВМ к РКС ВЫВ в цикле Ввод дешифратор 33 формирует сигнал ВВ 4, который проходит через элемент ИПИ-НЕ 37, мультиплексор 36 данных на группу магистральных передатчиков 27 сигналом высокого уровня. Кроме того, на группу передатчиков 27 поступает информация (О - для формирования кода 200в),. устанавливая на группе входов 44 мультиплексора 36. Передатчики 27 открываются также сигналом ВВ.4. поступающим через элемент ИЛИ-НЕ 34.

В результате на магистрали ЭВМ устанавливается код 200в, что означает готовность узла к приему информации, и поэтому ЭВМ выполняет цикл Вывод по отношению к РД ВЫВ.

РД ВЫВ реализуется в устройстве на следующих элементах: 4 и 5 - анализируют информацию, переданную ЭВМ (сравнивают и дешифрируют): 10 и 11 - запоминают информацию для дальнейшей ее индикации; 8,9 и 10 - управляют процессом записи в регистр 11,

В цикле Вывод от ЭВМ по магистрали через группу магистральных приемников 22 поступает информация, подлежащая записи в РД ВЫВ. Момент появления данной информации определяет сигнал Выв. 6, формируемый дешифратором 33. Если ЭВМ передает в устройство коды, соответствующие слежебной символам: ВК,/, О, или R, S и Р, то данные коды дешифрируются элементом 5. Например: ЭВМ передает код, соответствующий символу В К, тогда дешифратор 5 формирует на выходе Q сигнал высокого уровня, который через элемент ИЛИ-НЕ 7 поступает низким уровнем на входы счетчика 9 и регистра 10 индикации, устанавливая их в нулевое состояние, счетчик 9 и регистр 10 могут устанавливаться в нулевое состояние также системным сигналом УСТ, поступающим от процессора 3 высоким уровнем.

Если ЭВМ передает код, соответствующий символу /, то дешифратор 5 формирует сигнал низкого уровня на выходе Q1, который является входом S1 регистра 10 и служит для установки в 1 одного из его разрядов для последующего зажигания све- тодиода с символом /, также данный сигнал поступает на вход V счетчика 9 и устанавливает его в состояние 0110 (код установки на группе линий 17). Если ЭВМ передает один из кодов соответствующих символам R, S, О., то дешифратор формирует на одном из выходов Q2 сигнал низкого уровня, который поступает на один из входов S регистра 10 индикации, при этом сигнал высокого уровня, появляющийся на одном из выходов регистра, обеспечивает с помощью дешифратора 54 (см. фиг. 4) свечение одного из элементов индикации R, S, 6 или в блоке 13 индикации.

Если ЭВМ передает коды (60-67), соответствующие цифрам 0-7, то устройство работает следующим образом.

При появлении кода любой цифры элемент 4 сравнения (на входы его АО-АЗ поступают от ЭВМ старшие разряды кода цифры, а на входах ВО-ВЗ установлен код 0110) формирует положительный импульс (длительность равна длительности сигнала

0 ВЫ В.6). Этот импульс поступает на элемент 6, который его инвертирует. С выхода элемента 6 отрицательный импульс поступает на одновибратор 8 и вход +1 счетчика 9. Одновибратор 8 запускается от переднего

5 фронта импульса и формирует в свою очередь отрицательный импульс, длительность которого меньше длительности запускающего импульса. Сформированный одновиб- ратором импульс поступает на вход CS

0 дешифратора 12 и разрешает дешифрацию кода, установленного на выходах счетчика 9. В результате на одном из выходов дешифратора 12 появляется сигнал низкого уровня. Данный сигнал (его задний фронт)

5 воздействует на соответствующий вход с регистра 11. При этом в соответствующую триаду регистра 11 (разбитого на триады) записывается трехразрядный параллельный двоичный код (младшие разряды кода

0 цифры), поступающий на входы D регистра 11.

После того, как произошла запись информации в выбранную триаду регистра 11, происходит смена состояния счетчика 9 по

5 заднему фронту отрицательного импульса, поступившего на вход +1.

С выходов регистра 11 трехразрядные двоичные коды цифр совместно с разрядами (линия 21). разрешающими индикацию

0 данных цифр, поступают на блок 13 индикации.

Сброс регистра осуществляется по входу R сигналом низкого уровня УСТ.

Таким образом, устройство позволяет

5 индицировать состояние ЭВМ без промежуточных операций обращения к внутренней памяти, что приводит к повышению быстродействия устройства.

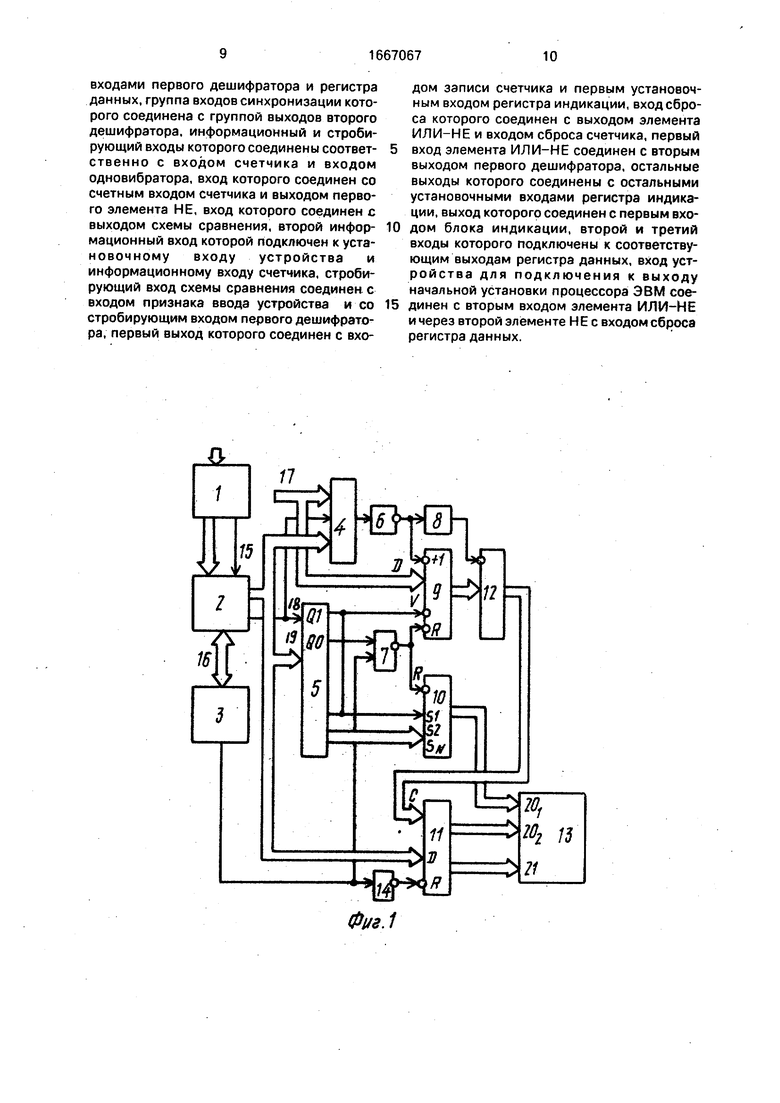

Формула изобретения

0 Устройство индикации состояния ЭВМ, содержащее схему сравнения, счетчик, первый дешифратор и блок индикации, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содер5 жит одновибратор, элемент ИЛИ-НЕ, второй дешифратор, регистр индикации, регистр данных и два элемента НЕ, причем информационный вход устройства соединен с первым информационным входом схемы сравнения и информационными

входами первого дешифратора и регистра данных, группа входов синхронизации которого соединена с группой выходов второго дешифратора, информационный и строби- рующий входы которого соединены соответ- ственно с входом счетчика и входом одновибратора, вход которого соединен со счетным входом счетчика и выходом первого элемента НЕ, вход которого соединен с выходом схемы сравнения, второй информационный вход которой подключен к установочному входу устройства и информационному входу счетчика, строби- рующий вход схемы сравнения соединен с входом признака ввода устройства и со стробирующим входом первого дешифратора, первый выход которого соединен с вхо0

дом записи счетчика и первым установочным входом регистра индикации, вход сброса которого соединен с выходом элемента ИЛИ-НЕ и входом сброса счетчика, первый вход элемента ИЛИ-НЕ соединен с вторым выходом первого дешифратора, остальные выходы которого соединены с остальными установочными входами регистра индикации, выход которого соединен с первым входом блока индикации, второй и третий входы которого подключены к соответствующим выходам регистра данных, вход устройства для подключения к выходу начальной установки процессора ЭВМ соединен с вторым входом элемента ИЛИ-НЕ и через второй элементе Н Е с входом сброса регистра данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1674142A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1988 |

|

SU1594555A2 |

| Устройство для сопряжения электронно-вычислительных машин | 1988 |

|

SU1580385A1 |

| Устройство для измерения параметров многополюсников | 1986 |

|

SU1478147A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для сопряжения двух ЭВМ | 1987 |

|

SU1499360A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1985 |

|

SU1291996A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

Изобретение относится к устройствам вычислительной техники и может быть использовано при построении микропроцессорных систем. Целью изобретения является повышение быстродействия. Устройство содержит блок индикации, схему сравнения, счетчик, дешифраторы, элемент НЕ, одновибратор, элемент ИЛИ - НЕ, регистр индикации и регистр данных с соответствующими связями. 7 ил.

Фиа.1

Фиг. 3

Фиг. 5

ФигМ

| ТЕЛЕФОННОЕ РЕЛЕ | 1923 |

|

SU1020A1 |

| Под ред | |||

| A.M | |||

| Ларионова | |||

| М.: Статистика, 1975, с | |||

| Прибор для определения всасывающей силы почвы | 1921 |

|

SU138A1 |

| Огнетушитель | 0 |

|

SU91A1 |

| Устройство для задания режимов работы цифровой вычислительной машины и индикации ее состояния | 1979 |

|

SU873240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1991-07-30—Публикация

1989-07-12—Подача