4

ю

4

ОО

Изобретение относится к технике цифровой связи и может быть использовано для выделения синхросигнала.

Целью изобретения является говы- шение помехозащищенности при выделении распределенного во времени синхросигнала.

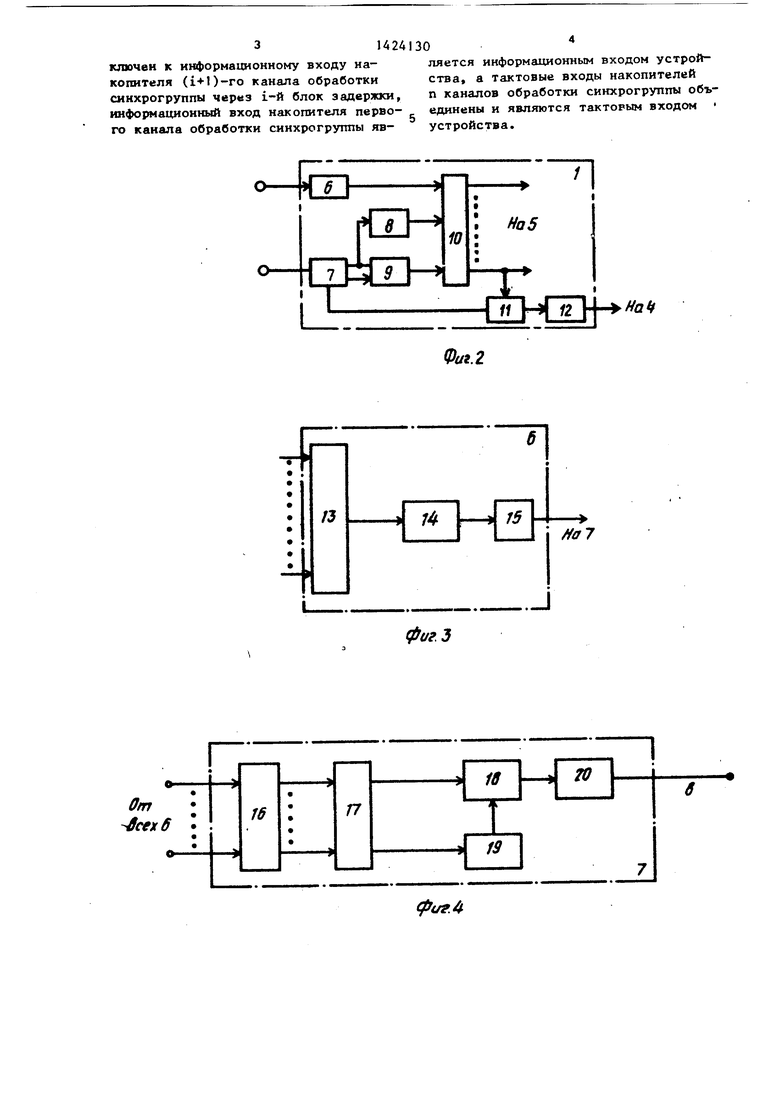

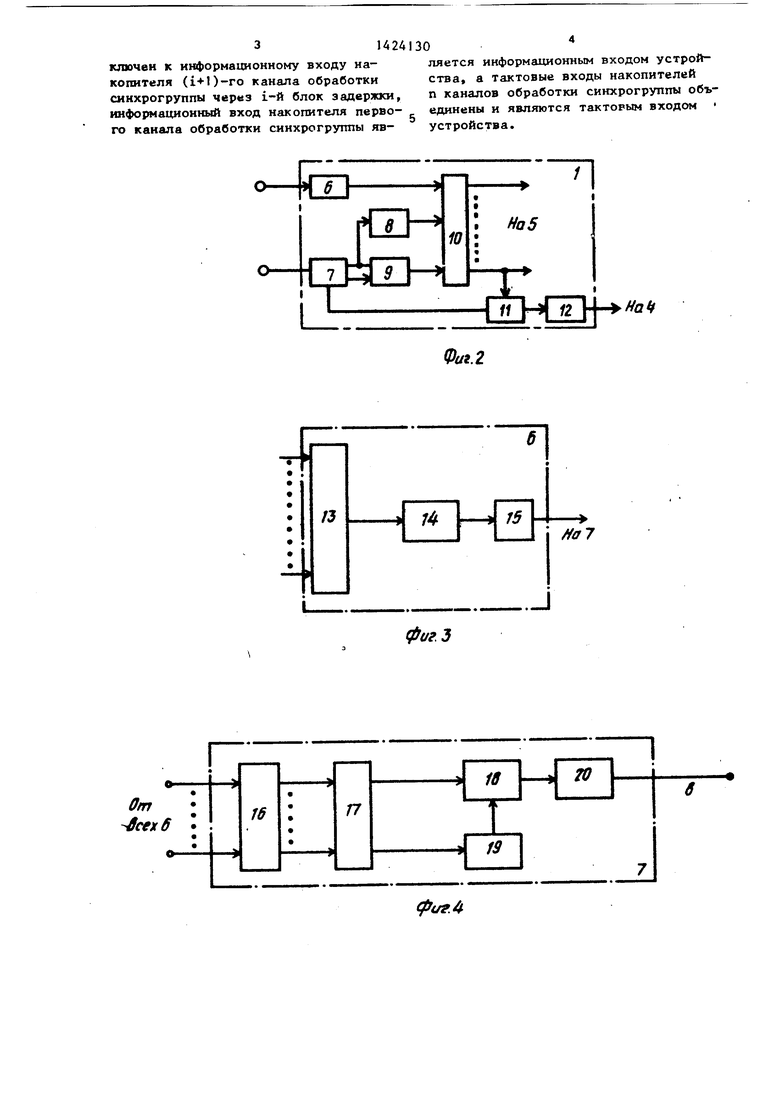

На фиг. 1 представлена структурна электрическая схема устройства выде- ления синхросигнала; на фиг. 2 - вариант реализации накопителя; на фиг. 3 - то же, опознавателя синхрогруппы; на фиг. А - то же, решающего узла соответственно.

Устройство выделения синхросигнала содержит п накопителей 1,1к,, (п-1) блоков 2 ,-2 , задержки, п преобразователей 3, - Зп кода , п опознав ател ей 4 h синхрогруппы и ре- шающий узел 5, причем в состав накопителя 1 входят согласующий усилител 6, делитель 7 частоты, формирователи 8 и 9 адресов записи и считьгаания, оперативный запоминающий блок 10,

D-триггер П и выходной усилитель 12 в состав каждого опознавателя А вход сумматор 13, пороговый блок 14 и формирователь 15 выходного сигнала, а в состав решающего узла 5 - блок 16 вы борки, дешифратор 17 выборки, коммутатор 18, пороговый блок 14 и формирователь 20 выходного сигнала.

Устройство выделения синхросигнала работает следующим образом.

Линейньй сигнал, содержащий синхро информацию, записьшается в накопитель 1у первого канала обработки синхрогруппы по сигналам, поступающим с тактового входа устройства. Емкость накопителя 1 должна быть не меньше количества символов в ожидаемой синхрогруппе. Снимаемый с выхода накопителя 1 сигнал через блок 2 задержки поступает на накопитель 1 следующего канала обработки синхрогруппы. Запись в накопители 1 последующих каналов .обработки синхрогруппы и продвижение информации через блоки 2 задержки осуществляют анапопгчно.

Бяоки 2 - 2 f,,, задержки обеспечивают необходимые временные интервалы между моментами поступления информации в накопители 1, - lt, соответст- вуто11Ц1е периодичности повторения ожи- даемых синхрогрупп.

Накопители 1 преобразуют записанную в них ииформацию в параллельную форму и подают ее одновременно на входы соответствующих преобразователей 3 кода, которые изменяют ее вид в зависимости от структуры (чередование импульсов и интервалов) ожидаемого синхросигнала.

Опознаватели 4 синхрогруппы анализируют поступающие с выходов преобразователей 3 сигналы и при наличии (или отсутствии) в них группы импульсов, аналогичных синхрогруппе, выра- батьшают соответствующие сигналы, к6- торые подаются на соответствующие входы решающего узла 5.

Появление подтверждающего сигнала на выходе одного из опознавателей А еще не свидетельствует о наличии истинной синхрогруппы, поскольку такой сигнал может быть вызван и приходом ложной синхрогруппы. Решающий узел 5 запрещает появление на выходе сигнала о выделении истинной синхрогруппы, если сигнал подтверждения ие появляется на заданном количестве опознавателей 4 синхрогруппы.

Приход истинной синхрогруппы, обладающей определенной периодичностью следования, вызьшает одновременное появление сигналов подтверждения на выходах заданного количества опознавателей 4 синхрогруппы. Только в этом случае решающий узел 5 формирует на выходе сигнал о наличии синхрогруппы

Формула изобретения

Устройство выделения синхросигнала, содержащее опознаватель синхрогруппы -и п каналов обработки синхрогруппы, в состав каждого из которых входит накопитель, причем выходы п каналов обработки синхрогруппы подключены к соответствующим входам решающего узла, отличающееся тем, что, с целью повьщ1ения помехозаииоценности при вьщелении распределенного во времени синхросигнала, введены (п-1) блоков задержки, (п-1) опознавателей синхрогруппы из п преобразователей кода, при этом в каждом из п каналов обработки синхрогруппы выходы накопителя через преобразователь кода подключены к соответствующим входам опознавателя сиHjcpoгруппы, выход которого является выходом канала обработки синхрогруппы, причем информационный выход накопителя i-ro канала обработки синхрогруппы (где i 1,2,...,п-1) подключей к информационному входу накопителя (i+O-ro канала обработки синхрогруппы через 1-й блок задержки, информационный вход накопителя первого канала обработки синхрогруппы является информационным входом устройства, а тактовые входы накопителей п каналов обработки синхрогруппы объединены и являются такторым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2298879C1 |

Изобретение относится к технике цифровой связи. Цель изобретения - повышение помехозащищенности при выделении распределенного во времени синхросигнала. Устр-во содержит накопители 1, блоки задержки (БЗ) 2, преобразователи 3 кода, опознаватели А синхрогруппы и решающий узел 5. Ли- нейньй сигнал, содержащий синхроин- формацию, записьшается в накопитель 1 первого канала обработки синхрогруппы. Затем осуществляется запись в накопители 1 последующих каналов и продвижение информации через БЗ 2. Накопители 1 преобразуют записанную в них информацию в параллельную форму и подают ее одновременно на преобразователи 3, которые изменяют ее. вид. Далее эти сигналы анализируются опознавателями 4. Приход истинной синхрогруппы, обладающей определенной периодичностью следования, вызывает одновременное появление сигналов подтверждения На выходах заданного ко- л}.чества опознавателей 4. Только в этом случае решающий узел 5 формирует на выходе сигнал о наличии синхрогруппы. 4 ил. (Л

/J

Half

Фаг. 2

74

Г5

/fa 7

,.J

фиг.Э

| Левин Л | |||

| С., Плоткин М | |||

| А | |||

| Цифровые системы передачи информации | |||

| М,: Радио и связь, 1982, с | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Колтунов М | |||

| Н | |||

| и др | |||

| Синхронизация по циклам в цифровых системах связи | |||

| М.; Связь, 1930, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1988-09-15—Публикация

1985-10-25—Подача