с входами вычитаемого и уменьшаемого вычитателя дополнительного диапазона, выход которого.соединен через четвертый дешифратор свходом второго шифратора рабочего диапазона,выход которого является выходом старшего разряда результата сумматора-умножителя, нечетные выходы первого и второго дешифраторов соединены соответственно с входами второго и третьего элементов ИЛИ, выходы которых сое- :

динены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛЯ, выход которого и выход четвертого элемента ИЛИ соединены соответственно с первым и вторым входами второго элемента ИСЮЮЧАЮЩЕЕ ИЛИ, выход которого является выходом переполнения сумматора-умножителя, нечетные выходы третьего дешифратора соединены соответственно с входами четвертого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Сумматор-вычитатель по модулю | 1982 |

|

SU1075259A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Устройство для суммирования | 1984 |

|

SU1233153A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

СУММАТОР-УМНОЖИТЕЛЬ, содержащий два коммутатора, сумматор рабочего диапазона, умножитель рабочего диапазона, причем первые информационньй и управляющий входы первого коммутатора соединены соответственно с входом второго операнда и входом сложения сумматора-умножителя, выход первого коммутатора соединен с первым входом сумматора рабочего диапазона, выходы умножителя рабочего диапазона и сумматора рабочего диапазона соединены соответственно с первым и вторым информационными входами второго коммутатора, первый управляющий вход и выход которого являются соответственно входом умножения и выходом младшего разряда результата сумматора-умножителя, о тличающийся тем, что, с целью расширения области применения за счет формирования сигнала переполнения при сложении и старшего разряда результата при умножении, он содержит четыре дешифратора, три шифратора дополнительного диапазона, умножитель дополнительного диапазона, вычитатель дополнительного диапазона, два шифратора рабочего диапазона, четыре элемента ИЛИ и два элемента ИСКЛКЬ ЧАЮЩЕЕ ИЛИ, причем вход первого операнда сумматора-умножителя соединен с вторым входом сумматора рабочего диапазона, первым входом умножителя рабочего диапазона и входом первого дешифратора, выходы которого соединены с соответствующими входами первого шифратора дополнительного диапазона, выход которого соединен с первым входом умножителя дополнительного диапазона, второй вход которого соединен с выхоi дом второго шифратора дополнительного диапазона, вход второго операн(Л да сумматора-умножителя соединен с вторым входом умножителя рабочего диапазона и входом второго дешифратора, выходы которого соединены с соответствующими входами второго шифратора дополнительного диапазона и первого шифратора рабочего диапа зона, выход которого соединен с со вторым информационным входом перво4 го коммутатора, второй управляющий О вход которого соединен с первым вхосо дом первого элемента ИЛИ и с входом вычитания сумматора-умножителя, вход сложения которого соединен с вторым входом первого элемента Ш1И, выход последнего соединен с вторым управляющим входом второго коммутатора, вькодом соединенного с входом третьего дешифратора, выходы которого соединены с соответствующими входами третьего шифратора дополнительного диапазона, выход которого и выход умножителя дополнительного диапазона соединены соответственно

1

Изобретение относится к вычислительной технике и может быть использовано в качестве одного из q-ичных разрядов многоразрядного арифметического устройства быстродействующих вычислительных машин.

Цель изобретения - расширение области применения за счет формирования сигнала переполнения при сложении и старшего разряда результата при умножении.

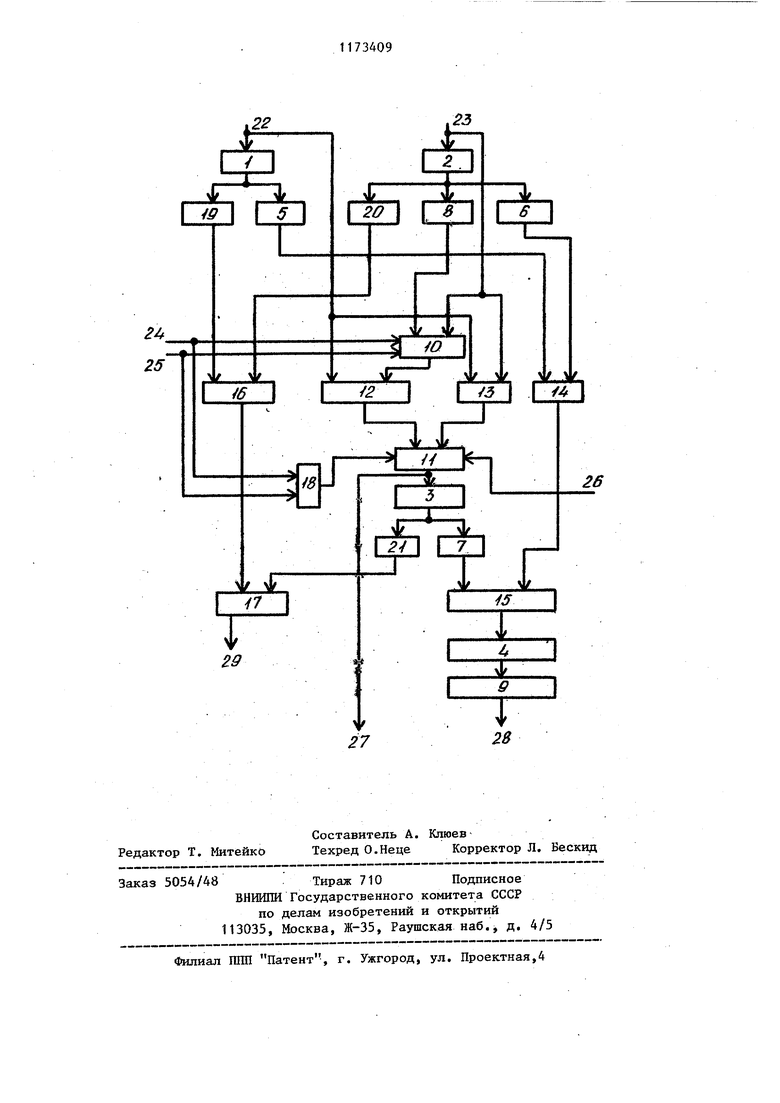

На чертеже представлена схема предлагаемого сумматора-умножителя.

Сумматор-умножитель содержит дешифраторы 1,2,3 и 4, шифраторы 5,6 и 7 дополнительного диапазона, шифраторы 8 и 9 рабочего диапазона, коммутаторы 10 и 11, сумматор 12 рабочего диапазона, умножитель 13 рабочего диапазона, умножитель 14 дополнительного диапазона, вычитатель 15 дополнительного диапазона, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и 17, элементы ИЛИ 18, 19, 20 и 21, 22 и 23,первого и второго операндов, входы 24, 25 и 26 слежения, вычитания и умножения,выходы 27, 28 и 29 младшего разряда, старшего разряда результата и переполнени соответственно.

В основу работы сумматора-умножителя положено следующее.

Пусть исходные числа Аи В представлены по основаниям рабочего диапазона СОК q П Р .Кроме того, пусть среди оснований рабочего диапазона нет четных оснований.

Произведение максимальных чисел из данного диапазона требует квадратичного диапазона для представлени Введем основания дополнительного диапазона СОК такие, что

.

1 n+1

Расширенный диапазон q-Q достаточен дпя представления произведения.

Запишем произведение чисел А и в виде

где oi и - старший и младший

разряды произведени соответственно.

Остатки произведения по основаниям рабочего диапазона представляют младшую q-ую цифру .

Старшая q-ая цифра произведения получается следуюшд1м образом:

((б)а-((АбЦ)а).

Сумма чисел из данного диапазон требует для своего представления двойного диапазона, ее можно записать в виде

,Uoi,

где oi(j- значение суммы по модулю q

V t ; 1 } - сигнал переноса в старший q-ый разряд,

V4(6)2-((A-B)ci)2)2Дешифраторы 1,2,3 и 4 преобразуют числа из кода СОК в унитарный код.

Шифраторы 5, 6 и 7 преобразуют унитарный код в код СОК по основаниям дополнительного диапазона.

3

Шифратор 8 преобразует унитарный код в код дополнения числа до 2 по основаниям рабочего диапазона.

Шифратор 9 преобразует унитарный код в код СОК по основаниям рабочег диапазона.

Сумматор 12 и вычитатель 15 представляют соответственно совокупность независимых сумматоров и вычитателей по основаниям СОК.

Умножители 13 и 14 представляют совокупность независимых умножителей по основаниям СОК.

Сумматор-умножитель работает следующим образом.

Сложение. Числа А и В по выходам 22 и 23 поступают на входы первого 1 и второго 2 дешифраторов. Одновременно по входу 24 поступает управляющий сигнал сложения, который открывает по первому управляющему входу коммутатор 10 и через элемент ИЛИ 18 по второму управляющему входу - коммутатор 11. Кроме того, числа А и В поступают на второй вход-сумматора 12 и на первый информационный вход коммутатора соответственно. Коды первого и второго слагаемых, преобразованные на элементах ИЛИ 19 и 20, по модулю два поступают на элемент ИСКШОЧА10.ЩЕЕ ИЛИ 16. С выхода коммутатора 10 второе слагаемое поступает на сумматор 12, где происходит сложение. С выхода сумматора 12 результат через открытый по второму входу коммутатор 11 поступает на выход 27 сумматора-умножителя. Код результата, преобразованный на элементе ИЛИ

734094

21, по модулю два поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17, на первый вход которого поступает значение с выхода элемента 5 ИСКЛЮЧАЮЩЕЕ ШШ 16. С выхода элемента ИСКЛЮЧАЮЩЕЕ ШШ 17 сигнал V поступает на выход 29 сумматора-умножителя.

Вычитание. Данная операция вы- . to полняется аналогично операции сложения. Отличие состоит в том, что через коммутатор 10 поступает с шифратора В дополнение кода второго числа.

15 Умножение. Числа А и Б с входов 22 и 23 поступают на дешифраторы 1 и 2. По входу 26 подается сигнал умножения. Первый и второй операнды поступают также на входы умножителя 13. Преобразованные по основаниям дополнительного диапазона на шифраторах 5 и 6 первый и второй операнд поступают на входы умножителя 14. С выхода умножителя 13

5 через коммутатор 11 младший разряд произведения od,, поступает на выход 27 сумматора-умножителя. Одновременно оС с помощью дешифратора 3 и шифратора 7 преобразуется в

0 код по основаниям дополнительного диапазона и вычитается на вычитателе 15 из результата умножителя 14. На выходе вычитателя 15 образуется старшая цифра о произведения по

основаниям дополнительного диапазона. Далее она преобразуется посредством дешифратора 4 и шифратора 9 в код по основаниям ра бочим диапазона и поступает на выход 28 сумматора-умножителя .

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU352275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СУММАТОР-УМНОЖИТЕЛЬ | 0 |

|

SU256368A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-15—Публикация

1983-06-29—Подача