Изобретение относится к вычислительной технике и может быть использовано при построении систем состоящих из отдельных функциональных блоков j подключенных к общей системной магистрали.

Цель изобретения - расширение функ1{иональньгх возможностей устройства за счет возможности подключения к нему активных блоков.

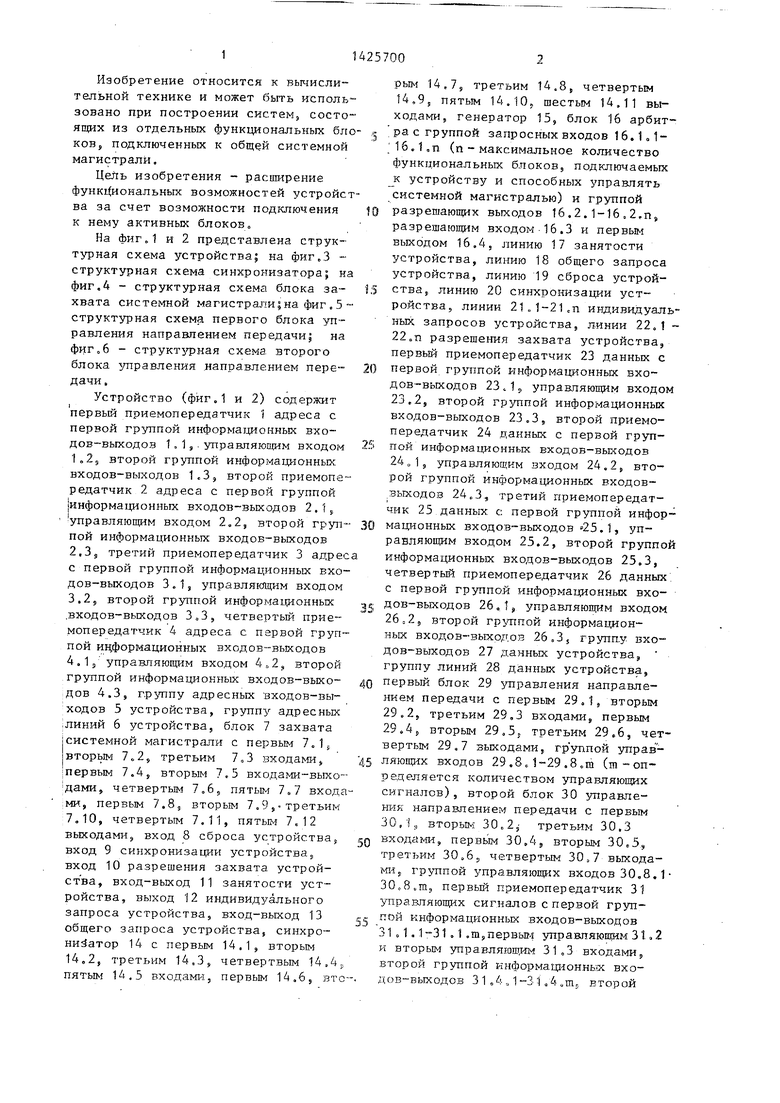

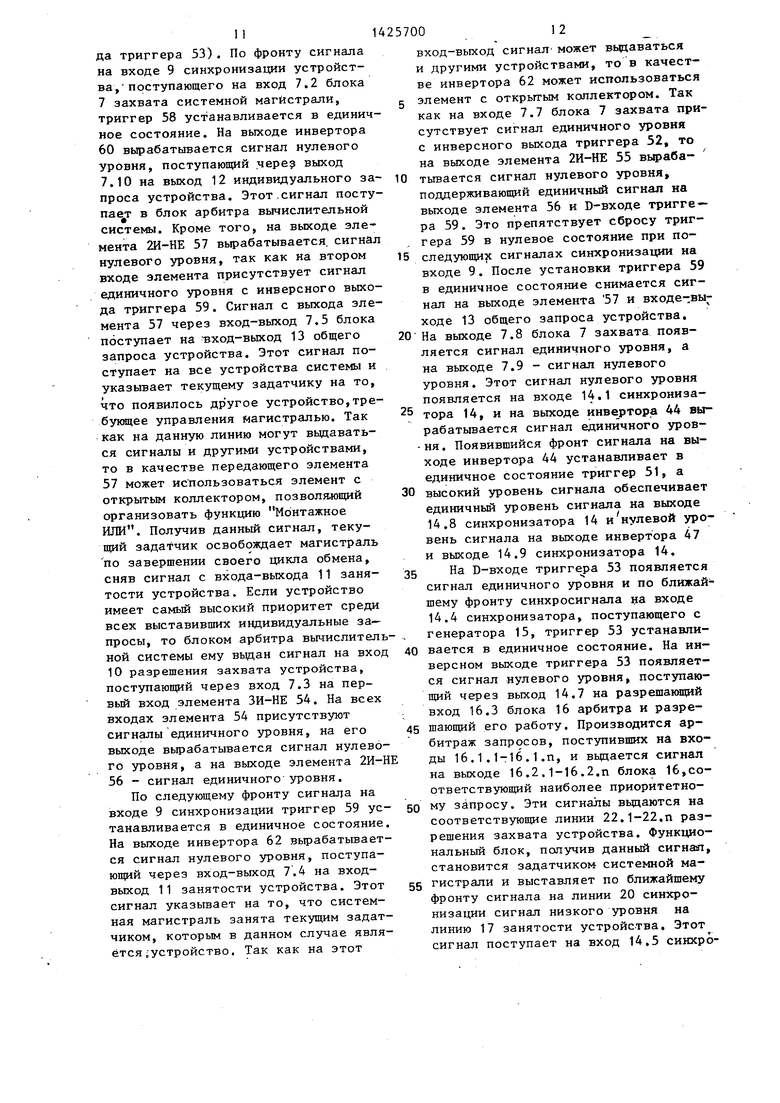

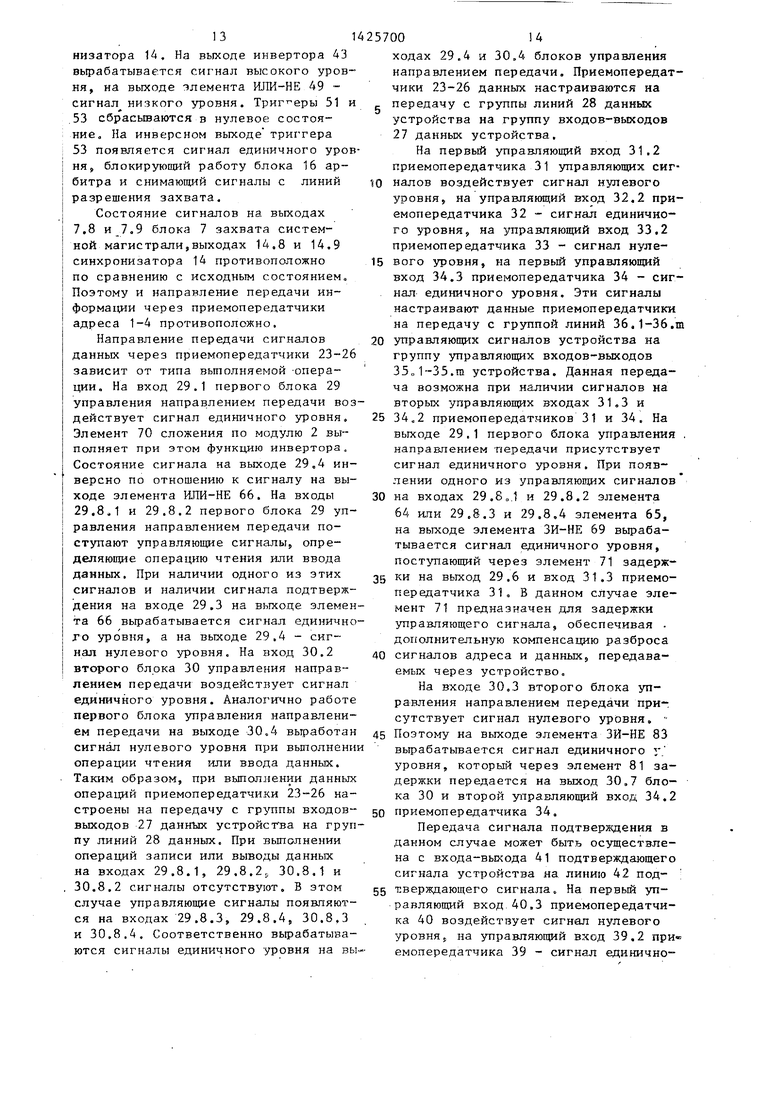

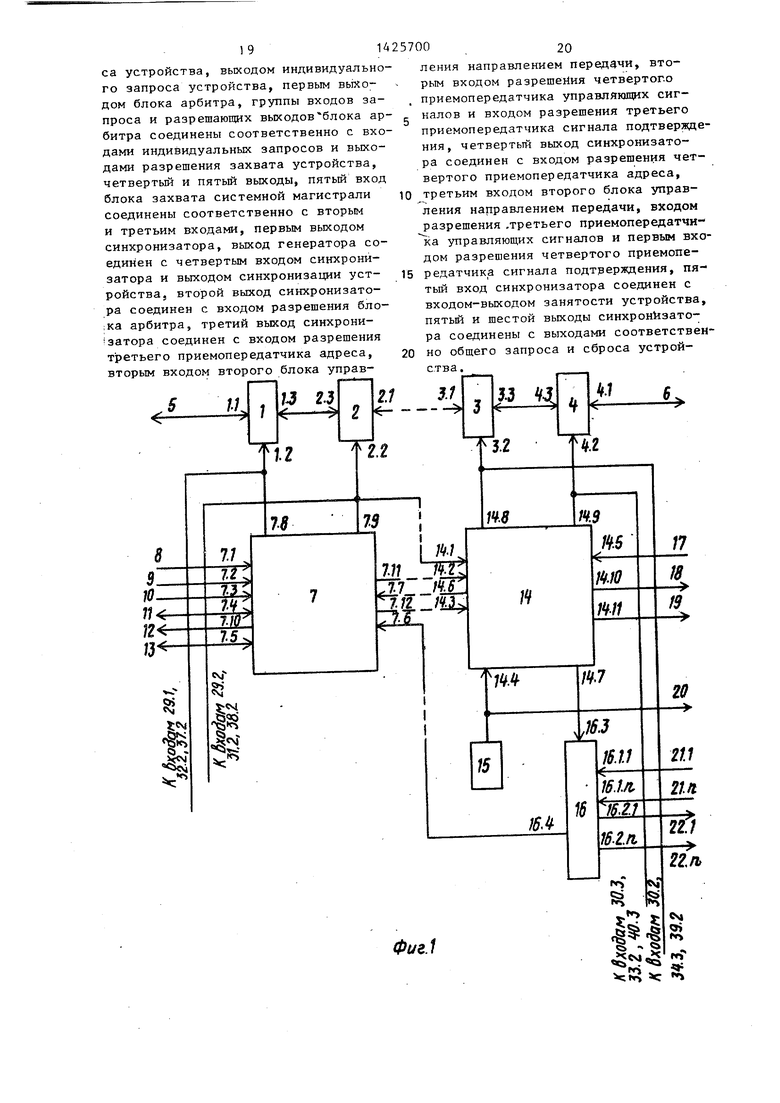

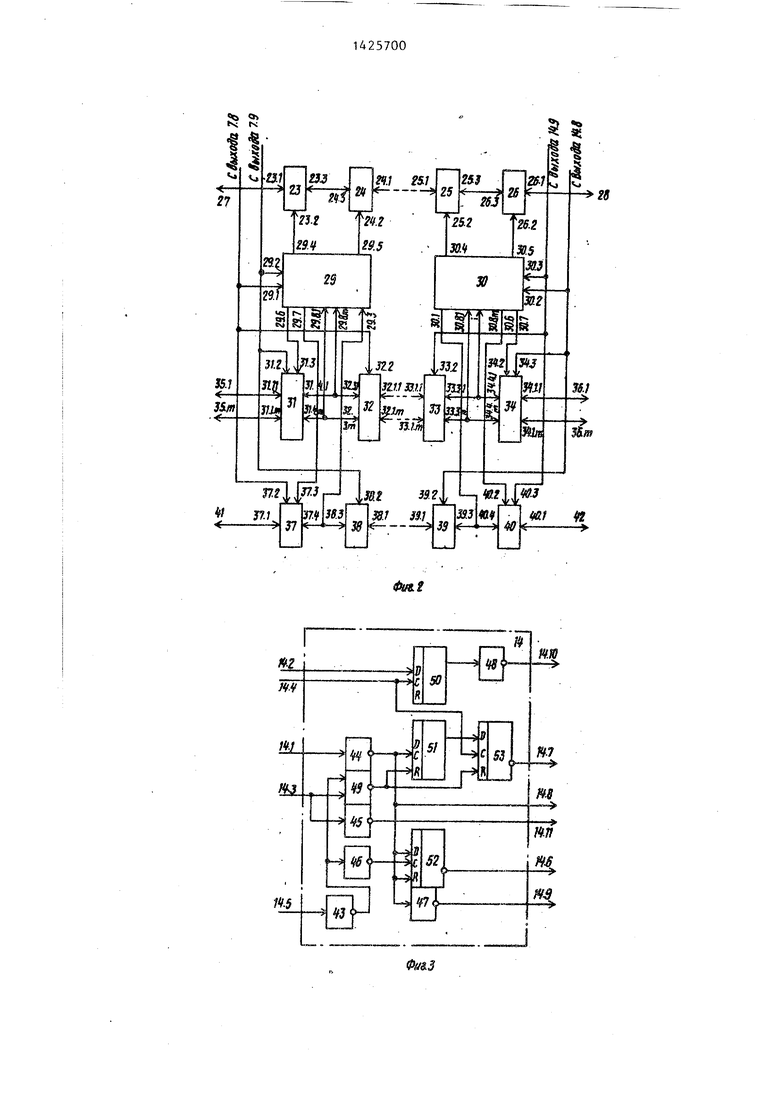

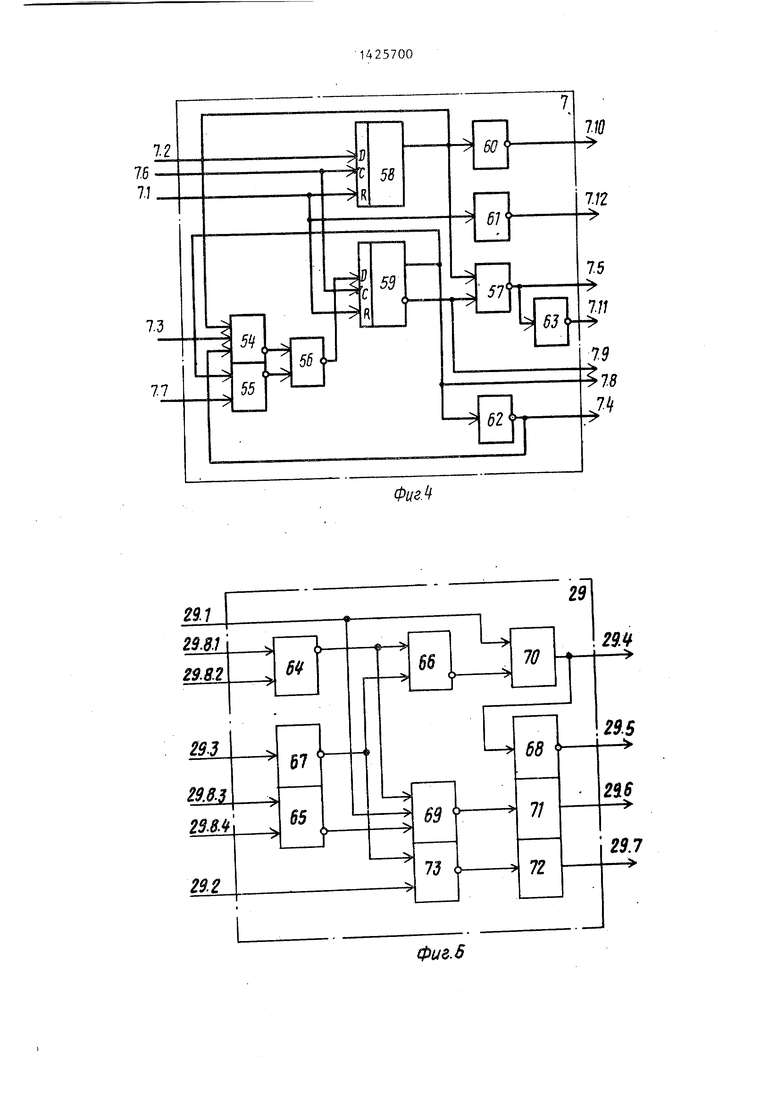

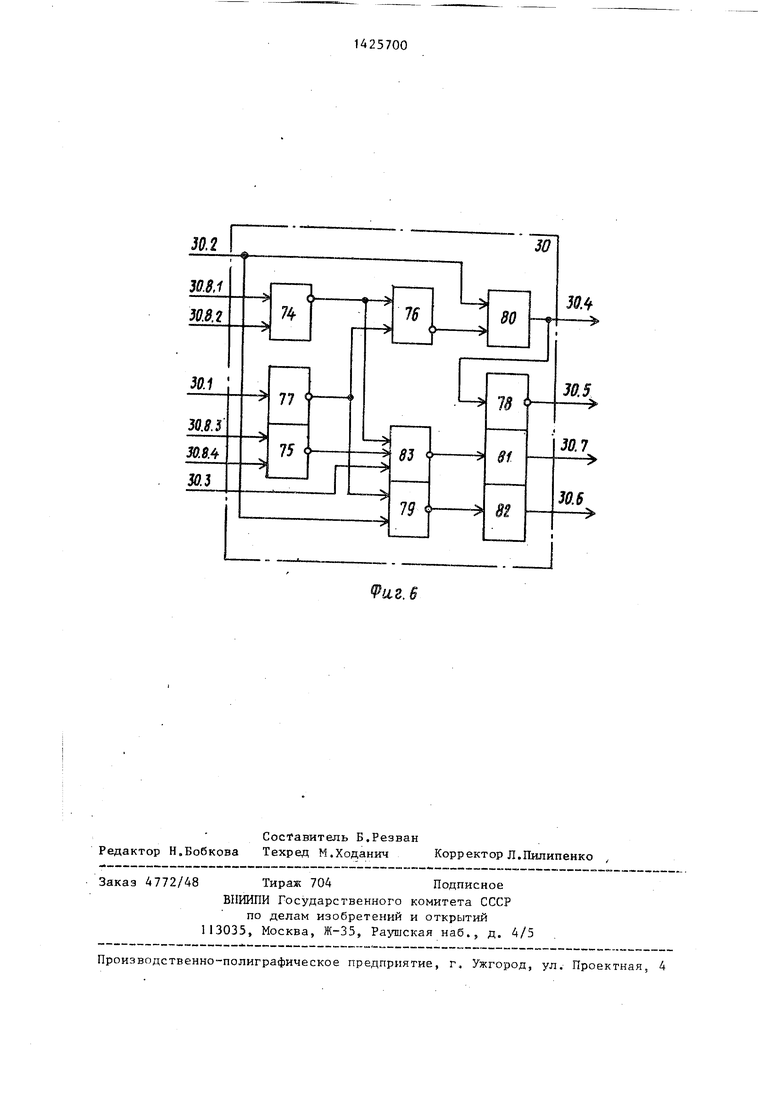

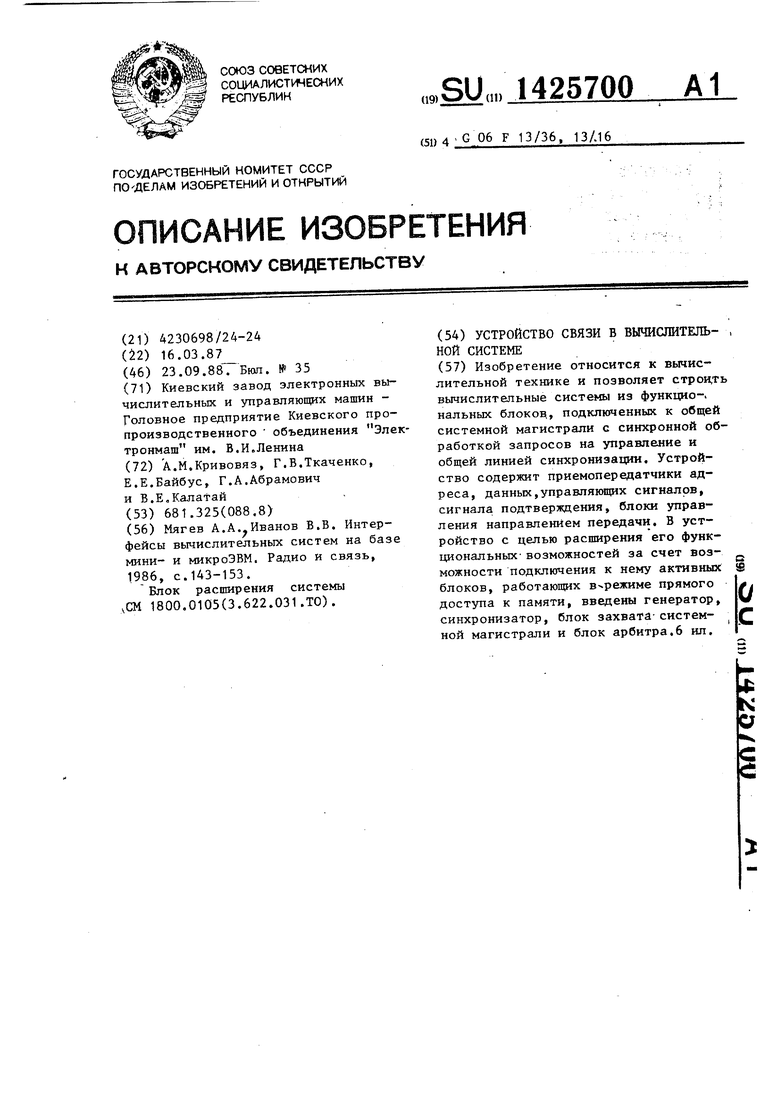

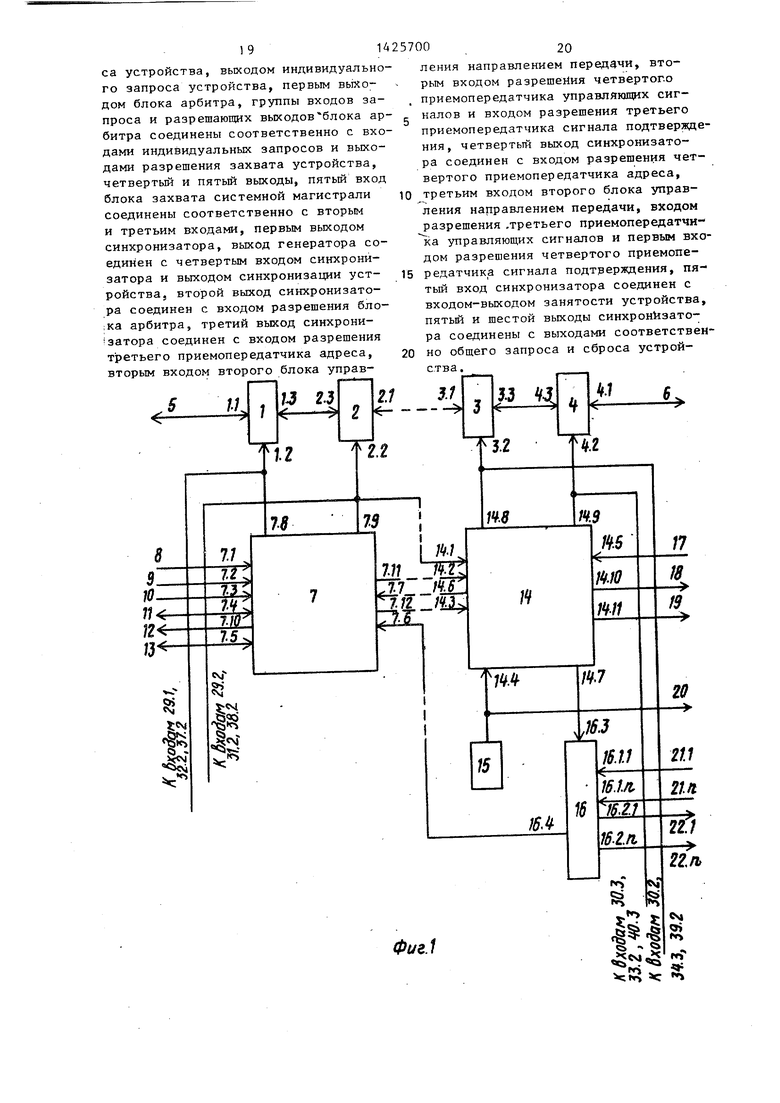

На фиг.1 и 2 представлена структурная схема устройства; на фиг.З - структурная схема синхронизатора; на фиг.4 - структурная схема блока захвата системной магистрали;на фиг. 5- структурная схема первого блока управления напраапением передачи| на фиг о 6 - структзфная схема второго блока управления .направлением передачи.

Устройство (фиг.1 и 2) содержит первый приемопередатчик 1 адреса с первой группой информатдионных входов-выходов 1.1,- управляюгцим входом 1„2э второй группой информационньк входов-выходов 1,3j второй приемопередатчик 2 адреса с первой группой информационных входов-выходов 2,t управляющим входом 2,2, второй группой информационных входов-выходов 2,3s третий приемопередатчик 3 адрес с первой группой информационных входов-выходов 3.1, управлякядим входом 3.25 второй группой информационных .входов-выходов 3.3, четвертьш приемопередатчик 4 адреса с первой группой информационных входов-выходов 4.15 управляющим входом 4,2. второй группой информационных входов-выходов 4.3, группу адресных входов-выходов 5 устройства, группу адресных линий 6 устройства, блок 7 захвата системной магистрали с первым 7.1 вторьм 7„25 третьим 7.3 входами,, первым 7.4, вторым 7.5 входами-выхо- дами четвертым 7.6, пятьм 7,7 входами, первым 7.8, вторым 7.9 ,, третьим 7.10, четвертым 7.11, ПЯТЬЕ 7,12 выходами, вход 8 сброса устройства, вход 9 синхронизации устройства, вход 10 разрешения захвата устройства, вход-выход 11 занятости устройства, выход 12 индивидуального запроса устройства, вход-выход 13 общего запроса устройства, синхро- нийатор 14 с первым 14.1, вторьм 14,2, третьим 14.3, четвертвым 14,4 пятым 14,5 входами, первым 14,6, втрьпч 14,7, третьим 14.8 четвертым 14,9, пятым 14.10, шестьм 14,11 выходами, генератор 15, блок 16 арбит. ра с группой запросных входов 16.1.1- Чб.1,п (п - максимальное количество функциональных блоков, подключаемых к устройству и способных управлять системной магистралью) и группой

разрешающих выходов 16.2.1-16.2,п, разрешающим входом-16,3 и первым выходом 16,4, линию 17 занятости устройства, линию 18 общего запроса устройства, линию 19 сброса устройства, линию 20 синхронизации устройства, линии 21„1-21сП индивидуальных запросов устройства, линии 22.1 22.п разрешения захвата устройства, nepBbrft приемопередатчик 23 данных с

первой группой информационных входов-выходов 23 с 15 управляющим входом 23,2, второй группой информационных входов-выходов 23.3, второй приемопередатчик 24 данных с первой группой информационных входов-выходов 24„1, управляющим входом 24.2, второй группой информационных входов- выходов 24,3,, третий приемопередатчик 25 данны х с первой группой информационных входов-выходов 25,1, управляющим входом 25.2, второй группой информационных входов-выходов 25.3, четвертьй приемопередатчик 26 данных, с первой группой информатдионных входов-выходов 26,1, управляющим входом 26 2, второй гр ттпой информационных входов-выходов 26,3; групп-у Бхо- дов-вьпсодов 27 данных устройства, группу линий 28 данных устройства, первый блок 29 управления направлением передачи с первым 29.1, вторым 29.2, третьим 29,3 входами, первым 29.4s вторым 29,55. третьим 29,6, четвертым 29,7 выходами, гр уппой управляющих входов 29 .8„ 1-29 .8.m (m-определяется количеством управляющих сигналов), второй блок 30 управления направлением передачи с первым 30,1д вторым 30,25 третьим 30,3

входами, первьм 30.4j вторым 30,5, третьим 30.6, четвертым 30,7 выходами, группой управляющих входов 30,8,1 30,8.т, первый приемопередатчик 31 управляющих сигналов с первой группой кнформационньк входов-выходов 31 „ 1.1-31 .1 .т5первы1-1 управляющим 31,2 и вторым управляющим 31.3 входаг да, второй группой кнформационньж входов-выходов 31„4,1-31.4.т, второй

приемопередатчик 32 управляющих налов с первой группой информационных входов-выходов 32,1.,1.ш, управляющим входом 32.2 и второй группой информационных входов-выходов 32.3.1-32.3.т, третий приемопередатчик 33 управляющих сигналов с первой группой информационных входов-выходов 33 .1.1-33.1.т, управляющим входом 33.2, второй группой информационных входов-выходов 33 .3 .1 - 33.3,т, четвертый приемопередатчик 34 управляющих сигналов с первой группой информационных входов-выходов 34.1.1-34.1.га, первым управляющим 34.3 и вторым управляющим 34,2 входами, второй группой информационных входов-выходов 34,4.1-34.4,т, группу управляющих входов-выходов 35о1-35.т устройства, группу линий

,36,1.-36,т управляющих сигналов устройства, первый приемопередат- с чик 37 сигнала подтверждения с первым входом - выходом 37.1, первым 37,2 и вторым 37.3 управляющими , входами, вторьгм входом-выходом 37,4, второй приемопередатчик 38 сигнала подтверждения с первым входом-выходом 38.1, управляющим входом 38,2, вторым входом-выходом 38,3, третий приемопередатчик 39 сигнала подтверждения с первым входом-выходом 39.1,

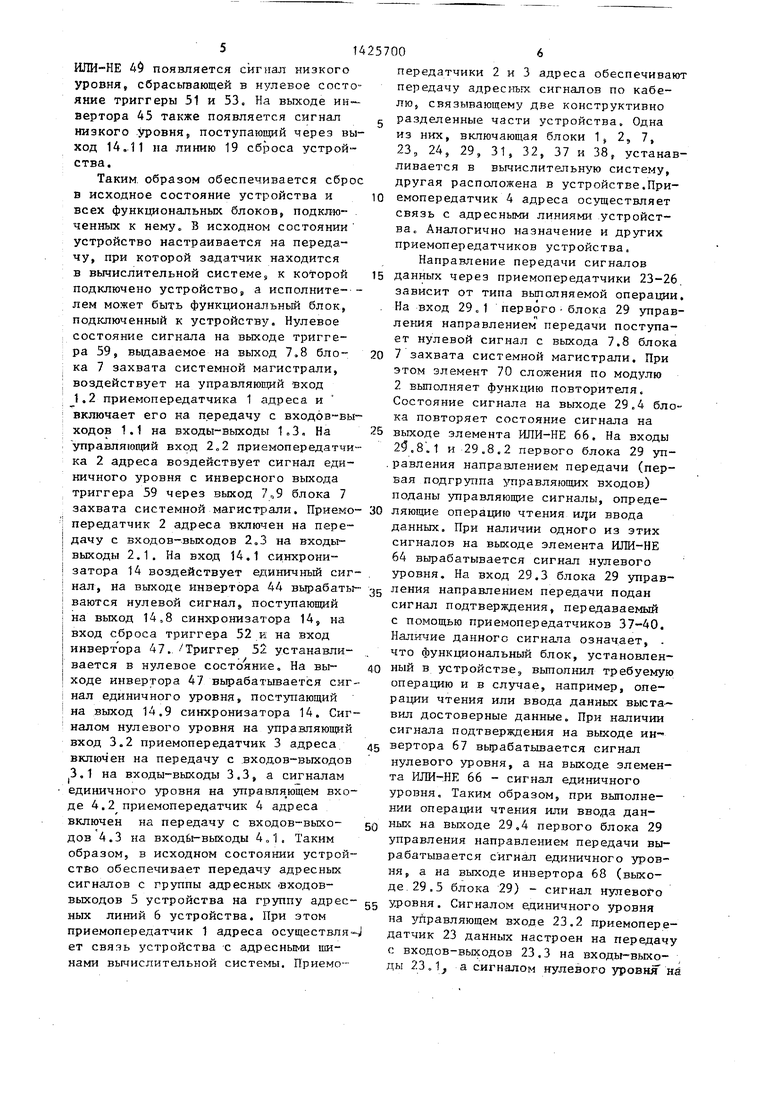

iуправляющим входом 39,2, вторым вхосиг-мент ЗИ-НЕ 69, элемент 70 сложения по модулю -2, первый 71 и второй 72 элементы задержки, элеме 5 2И-НЕ 73,.

Схема второго блока 30 управлен направлением передачи (фиг.6) соде жит первый 74, второй 75 и третий 76 элементы ИЛИ-НЕ, первый 77 и вт 10 рой 78 инверторы, элемент 2И-НЕ 79 элемент 80 сложения по модулю 2, п вый 81 и вт,орой 82 элементы задерж

ки, элемент ЗИ-НЕ 83.

Устройство работает следующим о 15 разом.

Вычислительная система, к котор подключается устройство, характери зуется наличием шин адреса, данных управляющих сигналов, сигналов под 20 тверждения, сброса, синхронизации, сигналов индивидуальньк запросов, сигналов разрешения захвата, сигнал занятости, сигнала общего запроса. В частном случае в качестве вычисл 25 тельной системы может использовать другое устройство связи,

В каждом цикле вычислительной с темы участвуют два функциональных блока - задатчик и исполнитель, За 30 датчик выставляет сигналы на адрес /ные шины, в случае записи выставляет сигналы на шины данньж, выста ляет управляющий сигнал, указывающ направление передачи и вид исполдом-выходом 39,3, четвертый приемопе-| ,, нителя (память или внешнее устройредатчик 40 сигнала подтверждения с , первым входом-выходом 40,1, первым 40.3 и BTopbiM 40,2 управляюшлм входами, вторым входом-выходом 40,4, вход-выход 41 подтверждающего сигнала устройства, линию 42 подтверждающего сигнала устройства.

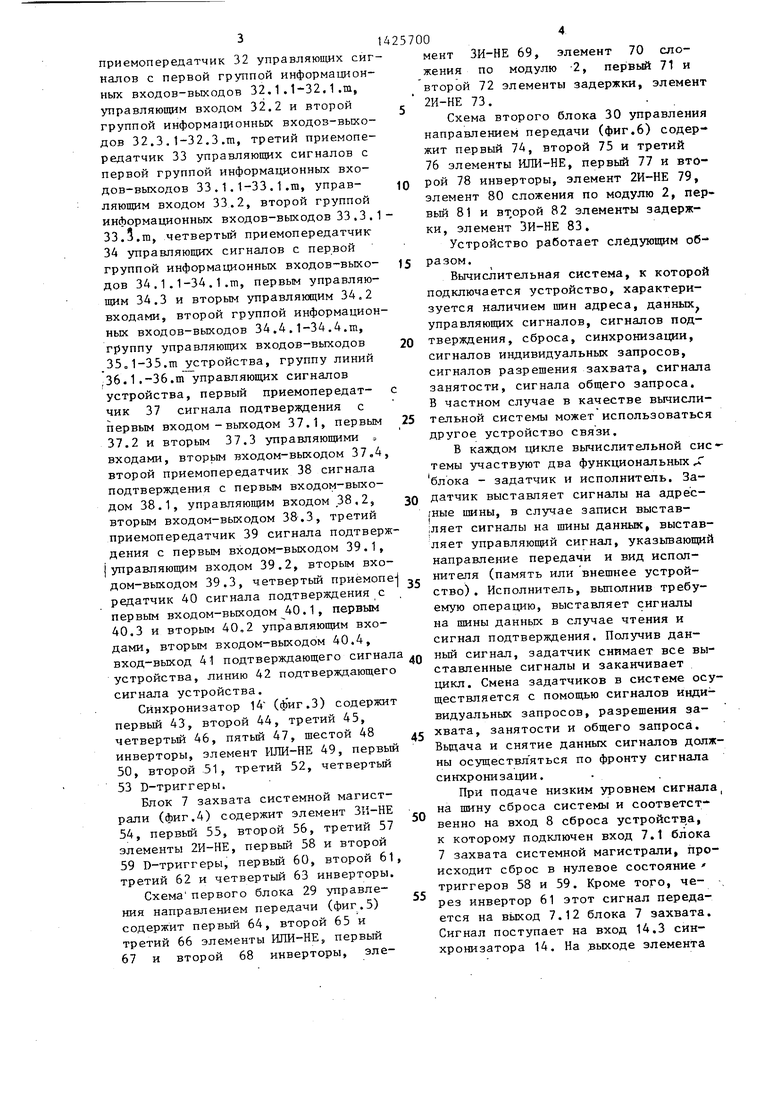

Синхронизатор 14 (ф иг.З) содержит первый 43, второй 44, третий 45, четвертый 46, пятый 47, щестой 48 инверторы, элемент ИЛИ-НЕ 49, первый 50, второй 51, третий 52, четвертый 53 D-триггеры.

Блок 7 захвата системной магистрали (фиг,4) содержит элемент ЗИ-НЕ 54, первый 55, второй 56, третий 57 элементы 2И-НЕ, первый 58 и второй 59 D-триггеры, первый 60, второй 61, третий 62 и четвертый 63 инверторы.

Схема первого блока 29 управления направлением передачи (фиг,5) содержит первьй 64, второй 65 и третий 66 элементы ИЛИ-НЕ, первый 67 и второй 68 инверторы, эле40

45

50

55

ство), Исполнитель, вьтолнив требуемую операцию, выставляет сигналы на шины данных в случае чтения и сигнал подтверждения. Получив данный сигнал, эадатчик снимает все вы ставленные сигналы и заканчивает цикл. Смена задатчиков в системе ос ществляется с помощью сигналов инди видуальных запросов, разрешения захвата, занятости и общего запроса. Вьщача и снятие данных сигналов дол ны осуществл яться по фронту сигнала синхронизации.

При подаче низким уровнем сигнал на шнну сброса системы и соответственно на вход 8 сброса устройств,а, к которому подключен вход 7.1 блока 7 захвата системной магистрали, про исходит сброс в нулевое состояние триггеров 58 и 59, Кроме того, через инвертор 61 этот сигнал передается на выход 7,12 блока 7 захвата. Сигнал поступает на вход 14,3 синхронизатора 14, На выходе элемента

-

1425700

-мент ЗИ-НЕ 69, элемент 70 сложения по модулю -2, первый 71 и второй 72 элементы задержки, элемент 5 2И-НЕ 73,.

Схема второго блока 30 управления направлением передачи (фиг.6) содержит первый 74, второй 75 и третий 76 элементы ИЛИ-НЕ, первый 77 и вто- 10 рой 78 инверторы, элемент 2И-НЕ 79, элемент 80 сложения по модулю 2, первый 81 и вт,орой 82 элементы задержки, элемент ЗИ-НЕ 83.

Устройство работает следующим об- разом.

Вычислительная система, к которой подключается устройство, характеризуется наличием шин адреса, данных управляющих сигналов, сигналов под- тверждения, сброса, синхронизации, сигналов индивидуальньк запросов, сигналов разрешения захвата, сигнала занятости, сигнала общего запроса. В частном случае в качестве вычисли- тельной системы может использоваться другое устройство связи,

В каждом цикле вычислительной сис«- темы участвуют два функциональных блока - задатчик и исполнитель, За- датчик выставляет сигналы на адрес- /ные шины, в случае записи выставляет сигналы на шины данньж, выставляет управляющий сигнал, указывающий направление передачи и вид исполнителя (память или внешнее устрой

ство), Исполнитель, вьтолнив требуемую операцию, выставляет сигналы на шины данных в случае чтения и сигнал подтверждения. Получив данный сигнал, эадатчик снимает все выставленные сигналы и заканчивает цикл. Смена задатчиков в системе осуществляется с помощью сигналов индивидуальных запросов, разрешения захвата, занятости и общего запроса. Вьщача и снятие данных сигналов должны осуществл яться по фронту сигнала синхронизации.

При подаче низким уровнем сигнала, на шнну сброса системы и соответственно на вход 8 сброса устройств,а, к которому подключен вход 7.1 блока 7 захвата системной магистрали, происходит сброс в нулевое состояние триггеров 58 и 59, Кроме того, через инвертор 61 этот сигнал передается на выход 7,12 блока 7 захвата. Сигнал поступает на вход 14,3 синхронизатора 14, На выходе элемента

514257006

ИЛИ-НЕ 4$ появляется ckruaji низкогопередатчики 2 и 3 адреса обеспечивают

уровня, сбрасьгаающей в нулевое состо-передачу адресных; сигналов по кабеяние триггеры 51 и 53. На выходе ин- лю, вертора 45 также появляется сигнал низкого .уровняS поступающий через выход 14,.11 па линию 19 сброса устройства.

Таким, образом обеспечивается сброс в исходное состояние устройства и всех функциональных блоков, подключенных к нему. В исходном состоянии устройство настраивается на передачу, при которой задатчик находится в вычислительной системе, к которой подключено устройство а исполните- - лем может быть функциональный блок, подключенный к устройству. Нулевое состояние сигнала на выходе триггера 59, выдаваемое на выход 7,8 блока 7 захвата системной магистрали, воздействует на управляющий вход 1.2 приемопередатчика 1 адреса и включает его на передачу с вход6в--вы ходов 1.1 на входы-выходы , На управляюп(Ий вход 2„2 приемопередатчика 2 адреса воздействует сигнал единичного уровня с инверсного выхода триггера 59 через выход 7,9 блока 7

ii связывающему две конструктивно

g разделенные части устройства. Одна из них, включающая блоки 1 j, 2, 7, 23,, 24, 29, 31, 32, 37 и 38 устанавливается в вычислительную систему, другая расположена в устройстве.При10 емопередатчик 4 адреса осуществляет связь с адресными линиями устройства. Аналогично назначение и других приемопередатчиков устройства. Направление передачи сигналов

15 данных через приемопередатчики 23-26. зависит от типа вьтсшняемой операции. . На вход 29 „1 первого блока 29 управления направлением передачи поступает нулевой сигнал с выхода 7.8 блока

20 7 захвата системной магистрали. При этом элемент 70 сложения по модулю 2 выполняет функцию повторителя. Состояние сигнала на выходе 29.4 блока повторяет состояние сигнала на

25 выходе элемента ИЛИ-НЕ 66, На входы

2.8.1 и 29.8.2 первого блока 29 уп- .равления направлением передачи (первая подгруппа отправляющих входов)

поданы управляющие сигналы, опреде- захвата системной магистрали. Приемо- 30 ляющие операцию чтения ввода передатчик 2 адреса включен на пере-данных. При наличии одного из этих

дачу с входов-выходов 2оЗ на входы-сигналов на выходе элемента ИЛИ-НЕ

выходы 2.1. На вход 14,1 синхрони-64 вырабатывается сигнал нулевого

затора 14 воздействует единичный сиг- . уровня. На вход 29.3 блока 29 управ- нал, на выходе инвертора 44 вырабаты- -jg ления направлением передачи подан ваются нулевой сигнал поступающийсигнал подтверждения, передаваемый

с помощью приемопередатчиков 37-40. Наличие данного сигнала означает, . что функциональный блок, установлен- 40 ный в устройстве, вьшапнил требуемую операцию и в случае, например, операции чтения или ввода данных выставил достоверные данные. При наличии

на выход 14,8 синхронизатора 14, на вход сброса триггера 52 к на вход инверт ора 47.. Триггер 52 устанавливается в нулевое состояние. На выходе инвертора 47 вырабатывается сигнал единичного уровня, поступающий на выход 14.9 синхронизатора 14, Сиглю,

ii связывающему две конструктивно

разделенные части устройства. Одна из них, включающая блоки 1 j, 2, 7, 23,, 24, 29, 31, 32, 37 и 38 устанавливается в вычислительную систему, другая расположена в устройстве.Приемопередатчик 4 адреса осуществляет связь с адресными линиями устройства. Аналогично назначение и других приемопередатчиков устройства. Направление передачи сигналов

данных через приемопередатчики 23-26. зависит от типа вьтсшняемой операции. На вход 29 „1 первого блока 29 управления направлением передачи поступает нулевой сигнал с выхода 7.8 блока

7 захвата системной магистрали. При этом элемент 70 сложения по модулю 2 выполняет функцию повторителя. Состояние сигнала на выходе 29.4 блока повторяет состояние сигнала на

выходе элемента ИЛИ-НЕ 66, На входы

2.8.1 и 29.8.2 первого блока 29 уп- равления направлением передачи (первая подгруппа отправляющих входов)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения процессора с общей магистралью | 1988 |

|

SU1606976A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Устройство для сопряжения двух магистралей | 1987 |

|

SU1462329A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1552195A1 |

| УСТРОЙСТВО ЛЕКАРСТВЕННОГО УЧЕТА | 1994 |

|

RU2111534C1 |

Изобретение относится к вычислительной технике и позволяет строи,ть вычислительные системы из функцио-, нальных блокоц, подключенных к общей системной магистрали с синхронной обработкой запросов на управление и общей линией синхронизации. Устройство содержит приемопередатчики адреса, данных,управляющих сигналов, сигнала подтверждения, блоки управления направлением передачи, В устройство с целью расщирения его функциональных- возможностей за счет возможности подключения к нему активных блоков, работающих в режиме прямого доступа к памяти, введены генератор, синхронизатор, блок захвата-системной магистрали и блок арбитра.6 ил. С

налом нулевого уровня на управляющийсигнала подтверждения на выходе ий-

вход 3.2 приемопередатчик 3 адреса 45 вертора 67 вырабатывается сигнал

включен на передачу с входов-выходов 3.1 на входы-выходы 3.3, а си гналам единичного уровня на упра1эля ющем входе 4.2 приемопередатчик 4 адреса включен на передачу с входов-выходов 4.3 на входб -выходы 4„1. Таким образом, в исходном состоянии устройство обеспечивает передачу адресных сигналов с группы адресных шходоввыходов 5 устройства на группу адрес- gg уровня. Сигналом единичного уровня ньгх линий 6 устройства. При этомна управляющем входе 23.2 приемопереприемопередатчик 1 адреса осуществля-J датчик 23 данных настроен на передачу ет связь устройства -с адресными ш-с входов-выходов 23.3 на входы-вьгхонами вычислительной системы. Приемо-ды 23 „1j а сигналом нулевого уровня на

нулевого уровня, а на выходе элемента ИЛИ-НЕ 66 - сигнал единичного уровня. Таким образом, при выполнении операции чтения или ввода дан- 50 ных на выходе 29,4 первого блока 29 управления направлением передачи вырабатывается сигнал единичного уровня, а на выходе инвертора 68 (выходе 29.5 блока 29) - сигнал нулевого

нулевого уровня, а на выходе элемента ИЛИ-НЕ 66 - сигнал единичного уровня. Таким образом, при выполнении операции чтения или ввода дан- ных на выходе 29,4 первого блока 29 управления направлением передачи вырабатывается сигнал единичного уровня, а на выходе инвертора 68 (выходе 29.5 блока 29) - сигнал нулевого

управляющем входе 24.2 приемопередатчик 24 данных настроен на передачу с входов-выходов 24.1 на выходы-входы 24.3. На вход 30.2 второго блока 30 управления направлением передачи поступает сигнал нулевого уровня и работа схемы на элементе ШТИ-НЕ 74, инверторе 77, элементе ИЛИ-НЕ 76, элементе 80 сложения по модулю 2 полностью аналогична рассмотренной схеме на элементах , 66 и 70. При этом на входы 30.8.1 и 30.8.2 блока 30 поданы те же управляющие сигналы, определяющие операцию чтения или ввода данных, а на вход 30,1 блока 30 подан сигнал подтверждения. Поэтому при выполнении операции чтения или ввода данных на выходе 30.4 второго блока 30 управления направлением передачи также вырабатывается сигнал единичного уровня, а на выходе инвертора 78 (выходе 30.5 блока 30) - сигнал нулевого уровня. Сигналом единичного уровня на управляющем входе 25.2 приемопередатчик 25 данных настроен на передачу с входов- выходов 25.3 на входы-выходы 25.1, а сигналом нулевого уровня на управляющем входе 26.2 приемопередатчик 26 данных настроен на передачу с входов- выходов 26.1 на входы-выходы 26.3. Таким образом, при выполнении операции чтения или ввода данных обеспечивается передача даннык с группы линий 28 данных устройства на шину данных вычислительной системы, к которой подключена группа входов-выходов 27 данных устройства.

При выполнении операции записи или вывода данных отсутствуют сигналы на входах элементов ИЛИ-НЕ 64 и 74, на выходах элементов вьфабаты- ваются сигналы единичного уровня. Тогда сигналы на выходах 29.4 и 30.4 приобретают низкий уровень, а на вь ходах 29.5 и 30.5 - высокий. Направление передачи данных через приемопередатчики 23-26 становится противоположным, т.е. с группы входов- выходов 27 данных устройства на группу линий 28 данных устройства.

На первый управляющий вход 31.2, приемопередатчика 31 управляющих сигналов поступает сигнал единичного уровня с выхода 7.9 блока 7 захвата системной магистрали. Этот сигнал разрешает приемопередатчику осуществлять передачу информации с входоввыходов 31.1.1-31.1.т соответственно на входы-выходы 31.4.1-31.4.т. Данная передача возможна только при на- личии сигнала на втором управляющем входе 31.3. Сигнал вырабатывается на выходе 29.6 первого блока управления направлением передачи. При нулевом состоянии сигнала на входе 29.1 бло

ка 29 на выходе элемента ЗИ-НЕ 69 вырабатывается сигнал единичного уровня, поступающ 1й через элемент 71 задержки на выход 29.6. Таким образом, в исходном состоянии приемопередатчик 31 осуществляет всегда передачу с входов-выходов 31.1.1-31.1.т на входы-выходы 31.4.1-31.4,т. На управляющий вход 32.2 приемопередатчика 32 управляющих сигналов поступает сигнал нулевого уровня с выхода 7.8

блока 7 захвата системной магистрали. При этом обеспечивается передача информации с входов-выходов 32.3.1 - 32.3.т на входы-выходы 32.1.1-32.1.т.

На управляющий вход 33.2 приемопередатчика 33 поступает сигнал еди- .ничного уровня с выхода 14.9 синхронизатора 14 и обеспечивает передачу с входов-выходов 33.1.1-33.1.то на

входы-выходы 33.3.1-33.3.т. На первый управляющий вход 34.3 приемопередатчика 34 поступает сигнал нулевого уровня с выхода 14.8 синхронизатора 14. Этот сигнал разрешает приемопередатчику 34 осуществлять передачу информации с входов-выходов 34.4.1-34.4.т на входы-выкоды 34.1.1-34.1.т соответственно. Данная передача возможна при наличии

сигнала на втором управляющем входе 34.2. Сигнал вырабатывается на выходе 30.7 второго блока 30 управления направлением передачи. На входе 30.3 блока 30 присутствует сигнал единичного уровня, поступающий на первый вход элемента ЗИ-НЕ 83. Тогда п ри поступлении одного из управляющих сигналов на входы элементов ИЛИ-НЕ 74 и 75 на выходе соответствукмдего

элемента вьфабатывается сигнал нулевого уровня. На выходе элемента ЗИ-НЕ 83 вырабатывается сигнал единичного уровня, поступающий через элемент 81 задержки на выход 30.7

блока 30. Элемент 81 предназначен . для задержки управляющего сигнала, обеспечивая дополнительную компенсацию разброса сигналов адреса и данных, передаваемьк через устройство. Управляющие сигналы помимо задания вида вьшолняемой операции осуществляют функцию указания достоверности сигналов на шинах адреса и данных. Таким образом, в исходном состоянии обеспечивается передача управляющих сигналов с группы управляющих входов-выходов 35.1-35.m устройства на группу линий 36.1-36,т управляющих сигналов устройства.

Передача сигнала подтверждения может быть осуществлена с линии 42 подтверждающего сигнала устройства на вход-выход 41 подтвер)вдающего сигнала устройства. Направление передачи через приемопередатчик 40 сигнала подтверждения определяется сигналами на его управляющих входах 40. и 40.3. На.первый управляющий вход 40.3 поступает сигнал единичного уровня с выхода 14.9 синхронизатора 14, Этот сигнал настраивает приемопередатчик 40 на передачу с входов- выходов 40.1 на входы-выходы 40.4. Данная передача возможна при наличии разрешающего сигнала на втором управляющем входе 40.2, поступающего с выхода 30.6 второго блока 30 управления направлением передачи. Так как на входе 30.2 блока 30 присутствует сигнал нулевого уровня с выхода 14.8 синхронизатора 14,. то на вы- хо де элемента 2И-НЕ 79 постоянно вырабатывается сигнал единичного уровня, поступающий через элемент 82 за- держки на выход 30,6. Приемопередатчик 40 постоянно настроен на передачу с входов-выходов 40,1 на входы-вы35 жен выставить сигнал на соответству ющей блоку линии 21.1-21,п индиви- дуальньгх запросов. Выдача данных сигналов должна осуществляться по . фронту сигнала на линии 20 синхроходы 40.4. На управляющем входе 39.2 40 низации устройства. Данные синхро- приемопередатчика 39 постоянно при-сигналы вьфабатьюаются генератором

сутствует сигнал нулевого уровня, обеспечивая передачу с входов-выходов 39.3 на входы-выходы 39.1. На уп- равяяюсцлй вход 38.2, приемопередатчика 38 поступает постоянно сигнал единичного уровня-с выхода 7.9 .блока 7 захвата системной магистрали, обеспечивая передачу с входов-выходов

управляющий вход 37.2 приемопередатчика 37 постоянно поступает сигнал нулевого уровня с выхода 7„В блока 7 захвата системной магистрали. Этот сигнал настраивает приемопередатчик 37 на передачу с входов-выходов 37,4 на входы-выходы 37.1, Данная передача возможна при наличии разрешающего сигнала на втором управляющем входе

входов 16.1.1-16.1.п блока 16 арбитра на выходе 16.4 вьфабатываетс сигнал, пocтyпaюш iй на вход 7.6 бл 7 захвата системной магистрали. Вы 55 дача разрешающих сигналов на выход 16.2.1-16,2.п блокируется единичнь уровнем сигнала на разрешающем вхо де 16.3, поступающим с выхода 14.7 синхронизатора 14 (инверсного вьгхо

Таким образом, в исходном состоянии все узлы устройства настроены на передачу данных между задатчи- ком, находящимся в вычислительной системе, и исполнителем,который может находиться в устройстве.

Если функ1 иональному блоку, установленному в устройстве, потребуется стать задатчиком системы, он должен выставить сигнал на соответствующей блоку линии 21.1-21,п индиви- дуальньгх запросов. Выдача данных сигналов должна осуществляться по . фронту сигнала на линии 20 синхро

низации устройства. Данные синхро- сигналы вьфабатьюаются генератором

При появлении сигнала на любом из

входов 16.1.1-16.1.п блока 16 арбитра на выходе 16.4 вьфабатывается сигнал, пocтyпaюш iй на вход 7.6 блока 7 захвата системной магистрали. Вы- 55 дача разрешающих сигналов на выходах 16.2.1-16,2.п блокируется единичньм уровнем сигнала на разрешающем входе 16.3, поступающим с выхода 14.7 синхронизатора 14 (инверсного вьгхода триггера 53), По фронту сигнала на входе 9 синхронизации устройства, поступающего на вход 7.2 блока 7 захвата системной магистрали, триггер 58 устанавливается в единичное состояние. На выходе инвертора 60 вырабатывается сигнал нулевого уровня, поступающий :чере9 выход 7.10 на выход 12 индивидуального запроса устройства. Этот,сигнал посту в блок арбитра вычислительной системы. Кроме того, на выходе элемента 2И-НЕ 57 вырабатывается, сигнал нулевого уровня, так как на втором входе элемента присутствует сигнал единичного уровня с инверсного выхода триггера 59. Сигнал с выхода элемента 57 через вход-выход 7.5 блока поступает на ход-выход 13 общего запроса устройства. Этот сигнал поступает на все устройства системы и указывает текущему задатчику на то, что появилось другое устройство,требующее управления магистралью. Так как на данную линию могут вьщавать- ся сигналы и другими устройствами, то в качестве передающего элемента 57 может использоваться элемент с открытым коллектором, позволяющий организовать функцию Монтажное ИЛИ. Получив данный сигнал, текущий задатчик освобождает магистраль по завершении своего цикла обмена, сняв сигнал с входа-выхода 11 занятости устройства. Если устройство имеет самый высокий приоритет среди всех выставивших индивидуальные запросы, то блоком арбитра вычислительной системы ему вьщан сигнал на вход 10 разрешения захвата устройства, поступающий через вход 7.3 на первый вход элемента ЗИ-НЕ 54. На всех входах элемента 54 присутствуют сигналы единичного уровня, на его выходе вьфабатывается сигнал нулевого уровня, а на выходе элемента 2И-Н 56 - сигнал единичного уровня.

По следующему фронту сигнала на входе 9 синхронизации триггер 59 устанавливается в единичное состояние. На выходе инвертора 62 вырабатьшает- ся сигнал нулевого уровня, поступающий через вход-выход 7.4 на вход- выход 11 занятости устройства. Этот сигнал указывает на то, что системная магистраль занята текущим задат- чиком, которым в данном случае является ;устройство. Так как на этот

вход-выход сигнал- может вцдаваться и другими устройствами, то в качестве инвертора 62 может использоваться 5 элемент с открытым коллектором. Так как на входе 7.7 блока 7 захвата присутствует сигнал единичного уровня с инверсного выхода триггера 52, то на выходе элемента 2И-НЕ 55 вьфаба0 тьшается сигнал нулевого уровня, поддерживающий единичный сигнал на выходе элемента 56 и D-входе триггера 59. Это препятствует сбросу триггера 59 в нулевое состояние при по5 следующие сигналах синхронизации на входе 9. После установки триггера 59 в единичное состояние снимается сигнал на выходе элемента 57 и входе-:вы- ходе 13 общего запроса устройства,

0 На выходе 7.8 блока 7 захвата появляется сигнал единичного уровня, а на выходе 7.9 - сигнал нулевого уровня. Этот сигнал нулевого уровня появляется на входе 14.1 синхрониза5 тора 14, и на выходе инвертора 44 вырабатывается сигнал единичного уров- -ня. Появившийся фронт сигнала на выходе инвертора 44 устанавливает в единичное состояние триггер 51, а

0 высокий уровень сигнала обеспечивает единичный уровень сигнала на выходе 14.8 синхронизатора 14 и нулевой уровень сигнала на выходе инвертора 47 и выходе 14.9 синхронизатора 14.

5 На D-входе тригге а 53 появляется сигнал единичного уровня и по ближайшему фронту синхросигнала на входе 14.4 синхронизатора, поступающего с генератора 15, триггер 53 устанавли0 вается в единичное состояние. На инверсном выходе триггера 53 появляется сигнал нулевого уровня, поступающий через выход 14.7 на разрешающий вход 16.3 блока 16 арбитра и разре5 шающий его работу. Производится арбитраж запросов, поступивших на входы 16.1.1-16.1.П, и вьщается сигнал на выходе 16.2.1-16.2.п блока 16,соответствующий наиболее приоритетно-

0 му запросу. Эти сигналы вьщаются на соответствующие линии 22.1-22.п разрешения захвата устройства. Функциональный блок, получив данный сигнал, становится эадатчиком системной ма5 гистрали и выставляет по ближайшему фронту сигнала на линии 20 синхронизации сигнал низкого уровня на линию 17 занятости устройства. Этот сигнал поступает на вход 14.5 синхронизатора 14, На выходе инвертора 43 вьфабатывается сигнал высокого уровня, на выходе элемента ИЛИ-НЕ 49 - сигнал низкого уровня. Триггеры 51 и 53 сбрасьшаются в нулевое состояние,, На инверсном выходе тригтера

53 появляется сигнал единичного уровня,, блокирующий работу блока 16 арбитра и снимаюп1ий сигналы с линий разрешения захвата.

Состояние сигналов на выходах 7.8 и 7,9 блока 7 захвата системной магистрали, выходах 14,8 и 14,9 синхронизатора 14 противоположно по сравнению с исходным состоянием. Поэтому и направление передачи ин- форма1щи через приемопередатчики адреса 1-4 противоположно.

Направление передачи сигналов данньк через приемопередатчики 23-26 зависит от типа вьтолняемой -операции. На вход 29.1 первого блока 29 управления направлением передачи воздействует сигнал единичного уровня. Элемент 70 сложения по модулю 2 выполняет при этом функцию инвертора,

Состояние сигнала на выходе 29.4 инверсно по отношению к сигналу на выходе элемента ИЛИ-НЕ 66, На входы 29.8,1 и 29,8,2 первого блока 29 управления направлением передачи поступают управляющие сигналы, определяющие операцию чтения или ввода данных. При наличии одного из этих сигналов и наличии сигнала подтверждения на входе 29.3 на выходе элемента 66 вырабатывается сигнал единичного уро вня, а на выходе 29,4 - сигнал нулевого уровня. На вход 30.2 второго блока 30 управления направлением передачи воздействует сигнал единичного уровня. Аналогично работе первого блока управления направлением передачи на выходе 30,4 выработан сигнал нулевого уровня при выполнении операции чтения или ввода данных. Таким образом, при выполнении данных операций приемопередатчики 23-26 настроены на передачу с грз. ппы входов- выходов 27 данных устройства на группу линий 28 данных. При выполнении операций записи или выводы данных на входах 29,8.1, 29.8.2, 30,8.1 и

30,8,2 сигналы отсутствуют. В этом случае управляющие сигналы появляются на входах 29,8.3, 29.8.4, 30,8,3 и 30,8.4, Соответственно вырабатываются сигналы единичного уровня на выходах 29,4 и 30.4 блоков управления направлением передачи. Приемопередатчики 23-26 данных настраиваются на

передачу с группы линий 28 данных устройства на группу входов-выходов 27 данных устройства.

На первый управляющий вход 31,2 приемопередатчика 31 управляющих сигналов воздействует сигнал нулевого уровня, на управлянщий вход 32.2 приемопередатчика 32 - сигнал единичного уровня, на управляющий вход 33.2 приемопередатчика 33 - сигнал нулевого уровня, на первый управляющий вход 34.3 приемопередатчика 34 - сигнал единичного уровня. Эти сигналы настраивают данные приемопередатчики на передачу с группой линий 36.1-36.m

управляющих сигналов устройства на группу управляющих входов-выходов 35„1-35.т устройства. Данная передача возможна при наличии сигналов на вторых управляющих входах 31,3 и

34„2 приемопередатчиков 31 и 34. На выходе 29.1 первого блока управления . направлением т ередачи присутствует сигнал единичного уровня. При появлении одного из управляющих сигналов

на входах 29.8„.1 и 29.8.2 элемента 64 или 29.8.3 и 29,8.4 элемента 65, на выходе элемента ЗИ-НЕ 69 вырабатывается сигнал единичного уровня, поступающий через элемент 71 задержки на выход 29.6 и вход 31.3 приемопередатчика 31, В данном случае элемент 71 предназначен для задержки Заправляющего сигнала, обеспечивая . дополнительную компенсацию разброса

сигналов адреса и данных, передаваемых через устройство.

На входе 30.3 второго блока управления направлением передачи присутствует сигнал нулевого уровня. Поэтому на выходе элемента ЗЙ-НЕ 83 вырабатывается сигнал единичного з уровня, который через элемент 81 задержки передается на выход 30,7 блока 30 и второй управляющий вход 34.2

приемопередатчика 34.

Передача сигнала подтверждения в данном случае может быть осуществлена с входа-выхода 41 подтверждающего сигнала устройства на линию 42 под-

тверждающего сигнала. На первый управляющий вход.40.3 приемопередатчика 40 воздействует сигнап нулевого уровняS на управляющий вход 39.2 при« емопередатчика 39 - сигнал единичного уровня, на управляющий вход 38.2 приемопередатчика 38 - сигнал нулевого уровня, на первый управляющий вход 37.2 приемопередатчика 38 - сигнал нулевого уровня, на первый управляющий вход 37,2 приемопередатчика 37 - сигнал единичного уровня. Все эти сигналы настраивают приемопередатчики на передачу с входа-выхода 41 на линию 42 подтверждающего сигнала. Данная передача возможна при наличии разрешающих сигналов на вторых управляющих входах.37.3 и приемопередатчиков 3-7 и 40 соответственно. На вход 29.2 первого блока управления направлением передачи воздействует сигнал нулевого уровня, поэтому на выходе элемента 2Й-НЕ 73 вырабатывается сигнал единичного уровня, поступающий через элемент 72 задержки на выход 29.7 и второй управляющий вход 37.3 приемопередатчика 37. На вход 30.2 второго блока 30 управления направлением передачи воздействует сигнал единичного уровня. Тогда при появлении на входе 30.1 блока 30 сигнала подтверждения на выходе и.нвертора 77 вьфабатывается сигнал нулевого уровня, на выходе элемента 2И-НЕ 79 сигнал единичного уровня, поступающий через элемент 82 задержки на выход 30.6 блока 30 и второй управляющий вход приемопередатчика 40. Эле- мент 82 в данном случае обеспечи- ,вает дополнительную задержку сигнала подтверждения для компенсации разброса сигналов данных, передаваемых через устройство в случае операции чтения или ввода данных.

Таким образом, после захвата системной магистрали функциональным блоком, установленным в устройстве, все узлы настроены на передачу данных между этим блоком и исполнителем, который может находиться в вычислительной системе.

Освобождение системной магистра- ли задатчиком происходит после завершения очередного цикла передачи данных, если от какого-либо другого устройства поступает сигнал на линии общего запроса. Если устройство, на- ходя щееся в вычислительной системе, требует захвата магистрали, то по очередному фронту сигнала синхронизации оно выставляет низким уровнем сигнал на вход-выход 13 общего запроса устройства. Этот сигнал поступает на вход-выход 7.5 блока 7 захвата системной магистрали. На выходе инвер- тора 63 и выходе 7.11 блока появляется сигнал единичного уровня, поступающий на вход 14,2 синхронизатора 14. По очередному фронту сигнала с генератора 15 на входе 14.4 синхронизатора 14 устанавливается в единичное состояние триггер 50. На выходе инвертора 48, в качестве которого должен использоваться элемент с открытым коллектором для организации

функции , Монтажное ИЛИ, вырабатывается сигнал нулевого уровня, поступающий через выход 14.10 на линию 18 общего запроса устройства. Этот сигнал и заставляет функциональный блок

освободить системную магистраль, выставив высоким уровнем сигнал на линию 17 занятости устройства. Этот сигнал поступает на вход 14,5 синхронизатора 14, на выходе инвертора 43

вырабатывается сигнал нулевого уров- ня, на выходе инвертора 46 - сигнал единичного уровня. По этому перепаду сигнала устанавливается в единичное состояние триггер 52, на его

инверсном выходе появляется сигнал нулевого уровня. Через выход 14,6 этот сигнал поступает на вХод -7.7 блока 7 захвата системной магистрали. На выходе элемента 2И-НЕ 55 вырабатывается сигнал единичного уровня, на выходе элемента 2И-НЕ 56 - сигнал нулевого уровня, поступающий на D- вход триггера 59. По ближайшему фронту сигнала на входе 9 синхронизации

триггер 59 устанавливается в нулевое состояние. На его инверсном выходе появляется сигнал единичного уровня, поступающий через выход 7,9 блока 7 захвата на вход 14.1 синхронизатора

Формула изобретен и я

Устройство связи в вычислительной

системе, содержащее по четыре приемо- передатчика адреса, данных, управляю-; щих сигналов, сигнала подтверждения,. два блока управления направлением

17

передачи, причем группы адресных входов-выходов, входов-выходов данных,

управляющих входов-выходов ВХОД ВЕз1ход подтверждающего сигнала устройства соединены с первыми группами информационных входов вьЬ одов первых приемопередатчиков соответственно адреса, данных,, управляющих сигналов и первым входом-выходом первого приемопередатчика сигнала под- , тверждения вторые групггы информационных входов-выходов первых приемопередатчиков адреса), данных, управляющих сигналов и второй вход™ выход первого датчиков гфиемопередат чика сигнала- подтверждения соединены соответственно с вторыми группами информационных входов-выходов вторых одноименных приемопередатчиков и вторым входом-выходом второго при емопередатчика сигнала подтверждения первые группы информационз1ых: входов™ вькодов вторых приемопередатчиков адреса, данных, управляющих сигналов и первый вход-вькод второго при емопередатчика сигнала подтверждения соединены соответственно с первыми группами информационных входов-выходов третьих одноименных приемопередатчиков и первым входом-вьпсо- дом третьего приемопередатчика сигнала подтверждения5 вторые группы информационных входов-выхрдов третьи приемопередатчиков адресаj данных,, управляющих сигналов и второй вход- выход третьего приемопередатчика сигнала .подтверждения соединены соот- ветств енно с второй rpyrsnoft информационных входов-выходов четвертьк одноименных приемопередатчиков и вторым входом-выходом четвертого приемопередатчика сигнала подтверждения, первая группа информационньк входов-выходов четвертых; приемопередатчиков адреса; данных, управляющих сигнатюв и первый вход-выход четвертого приемопередатчика сигнала подтверждения соединены с оответ- ственно с группами входов-выходов адреса, данных, - управляюзцих сигналов и подтверждающего сигнала устройства, входы разрешения первого и второго приемопередатчиков данных соединены соответственно с первым и вторым выходами первого блока управления направлением передачи, входы разрешения третьего и четвертого приемопередатчиков данных соединены с

14

, 2570018

первым и вторым выходами второго блока управления направлением передачи, группа yпpaвляющ x входов которых

(- соединена с вторыми группами информационных входов-выходов соответственно первого и третьего приемопередатчиков управляющих сигналовд первые входы разрешения первого и чет10 вертого приемопередатчиков управляю- ЩИ.К сигналов соединены соответственно с третьим и четвертым выходами, соответственно первого и второго блоков управления направлением передачи,

1Й третий и первьм входы которых соединены соответственно с вторыми входа- ми-выхода ш первого и третьего приемопередатчиков сигнала подтверждения, первые управляющие входы разрешения

20 первого и четвертого приемопередатчиков сигнала подтверждения соединены соответственно с четвертым первого блока и третьим выходом второго блока управления направлением

25 передачи, отживающееся

тем,, что, с целью расширения функциональных возмолсностей за счет возможности подключения активных блоков, в него введены генератор,, син30 хронизатор, блок захвата системной магистрали и блок арбитра, причем, вход разрешения первого приемопередатчика адреса соединен с первым выходом блока захвата системной маги g страли, первым входом первого блока управления направлением передачи, первым входом разрешения первого приемопередатчика сигнала подтверждения и входом разрешения второго приемо40 передатчика управляющих сигналов, вход разрешения второго приемопередатчика адреса соединен с вторым выходом блока захвата системной магистрали, вторым входом первого блока.

45 управления направлением передачи, вторым входом разрешения первого приемопередатчика управляющих сигналов, входом разрешения второго приемопередатчика сигнала подтверлздения

gg и первым ВХОДОМ синхронизатора, первый, второй, третий входы блока захвата системной магистрали соединены соответственно с входами сброса, синхронизации и разрешения захвата уст55 ррйства, первьм. второй входы-выходы, третий выход, четвертый вход блока захвата системной магистрали соединен ны соответственно с входами-выходами занятости устройства;, общего запро-

19

са устройства, выходом индивидуальнго запроса устройства, первым выходом блока арбитра, группы входов запроса и разрешающих выходов блока абитра соединены соответственно с вхдами индивидуальных запросов и выходами разрешения захвата устройства, четвертый и пятьй вьжоды, пятый вхо блока захвата системной магистрали соединены соответственно с вторым и третьим входами, первым выходом синхронизатора, выход генератора соединен с четвертым входом синхронизатора и выходом синхронизации уст- ройства, второй выход синхронизатора соединен с входом разрешения бло ;ка арбитра, третий выход синхрони- затора соединен с входом разрешения третьего приемопередатчика адреса, вторым входом второго блока управ

20

ления направлением передачи, вторым входом разрешения четвертого приемопередатчика управляющих сигналов и входом разрешения третьего приемопередатчика сигнала подтверждения, четвертый выход синхронизатора соединен с входом разрешения четвертого приемопередатчика адреса, третьим входом второго блока управления направлением передачи, входом разрешения .третьего приемопередатчика управляющих сигналов и первым входом разрешения четвертого приемопередатчика сигнала подтверждения, пятый вход синхронизатора соединен с входом-выходом занятости устройства, пятый и шестой выходы синхронизатора соединены с выходами соответственно общего запроса и сброса устройства ,

т

фиг. 6

иг.б

| Мягев А.А.Иванов В.В | |||

| Интерфейсы вычислительньпс систем на базе мини- и микроэвм | |||

| Радио и связь, 1986, с.143-153 | |||

| Всасывающе-нагнетательное устройство для передвижения судов | 1925 |

|

SU1800A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-16—Подача