Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах на основе мультипроцессорных вычислительных систем.

Целью изобретения является увеличение пропускной способности системы за счет повышения степени распараллеливания процесса обработки потока взаимозависимых заявок.

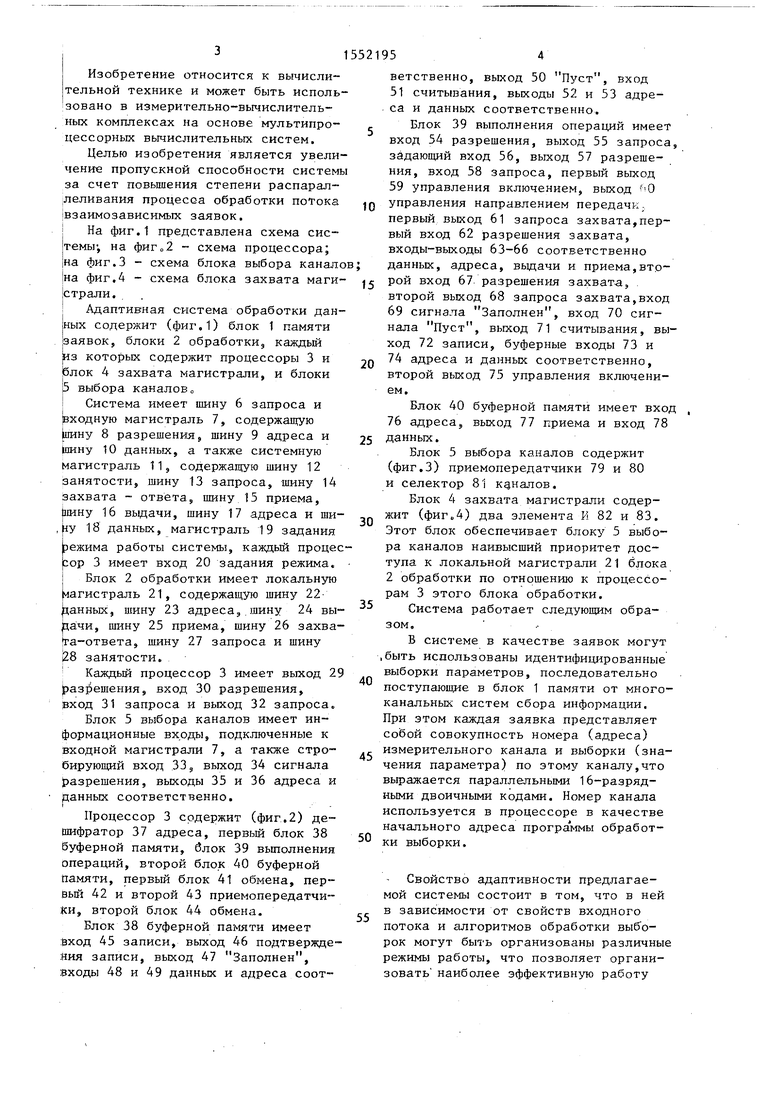

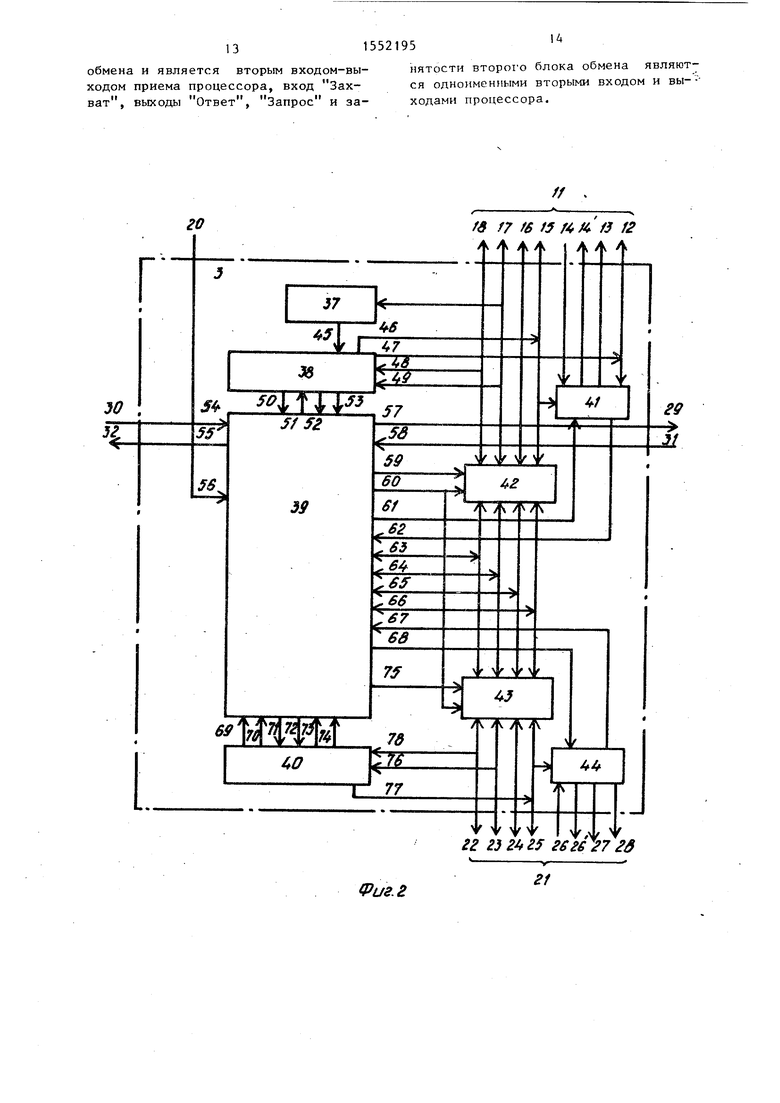

На фиг.1 представлена схема системы-, на фиг о2 - схема процессора; на фиг.З - схема блока выбора канало на фиг.4 - схема блока захвата маги- 1страли.

Адаптивная система обработки дан- ых содержит (фиг.1) блок 1 памяти

заявок, блоки 2 обработки,, каждый |из которых содержит процессоры 3 и блок 4 захвата магистрали, и блоки 5 выбора каналов о

Система имеет шину 6 запроса и ходную магистраль 7, содержащую |шну 8 разрешения, шину 9 адреса и шину 10 данных, а также системную магистраль 11, содержащую шину 12 занятости, шину 13 запроса, шину 14 захвата - ответа, шину 15 приема, шину 16 выдачи, шину 17 адреса и шину 18 данных, магистраль 19 задания режима работы системы, каждый проце рор 3 имеет вход 20 задания режима.

Блок 2 обработки имеет локальную магистраль 21, содержащую шину 22 Данных, шину 23 адреса, шину 24 выдачи, шину 25 приема, шину 26 захвата-ответа, шину 27 запроса и шину 28 занятости.

Каждый процессор 3 имеет выход 2 разрешения, вход 30 разрешения, вход 31 запроса и выход 32 запроса.

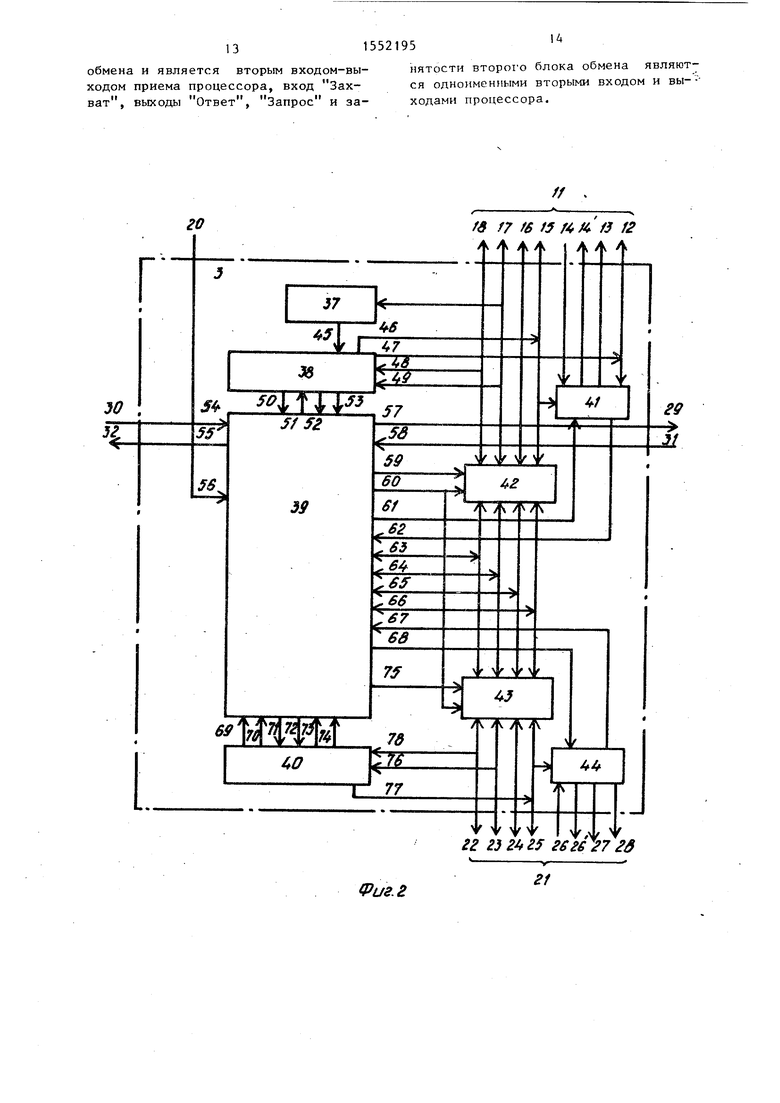

Блок 5 выбора каналов имеет информационные входы, подключенные к входной магистрали 7, а также стро- бирующий вход 33, выход 34 сигнала разрешения, выходы 35 и 36 адреса и данных соответственно.

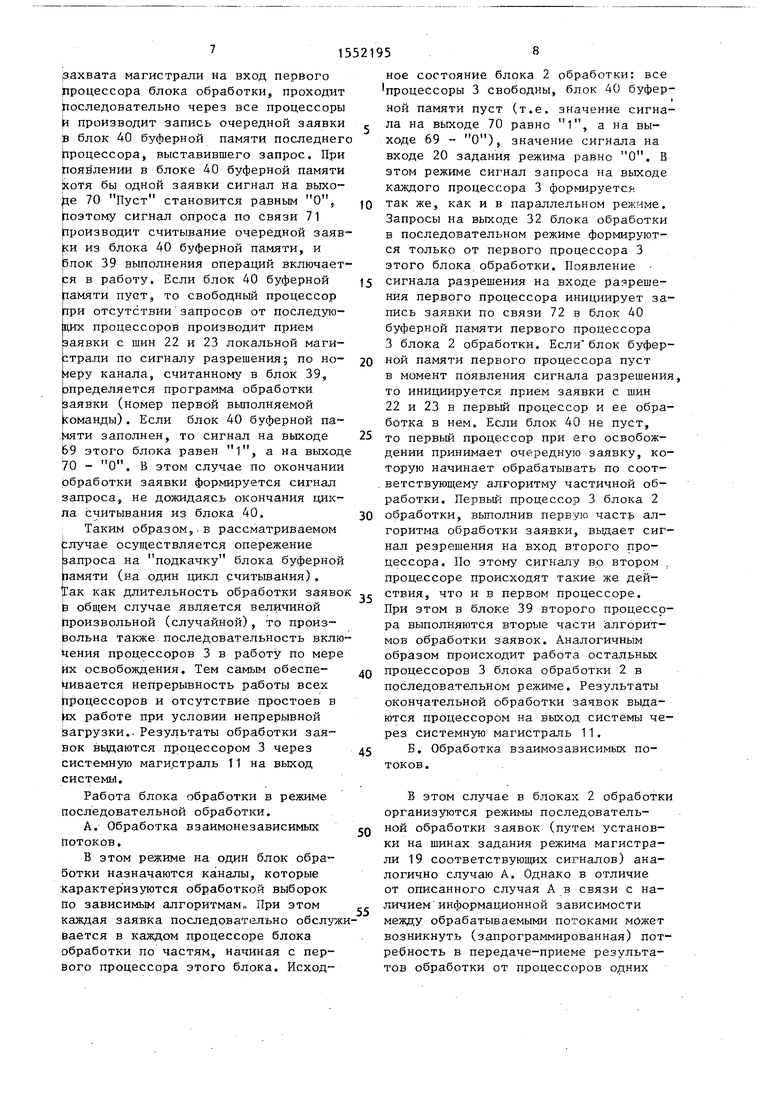

Процессор 3 содержит (фиг.2) дешифратор 37 адреса, первый блок 38 буферной памяти, блок 39 выполнения операций, второй блок 40 буферной Памяти, первый блок 41 обмена, первый 42 и второй 43 приемопередатчики, второй блок 44 обмена.

Блок 38 буферной памяти имеет Вход 45 записи, выход 46 подтвержде йия записи, выход 47 Заполнен, входы 48 и 49 данных и адреса соот

10

5

0

5

0

5

0

45

0

5

ветственно, выход 50 Пуст, вход 51 считывания, выходы 52 и 53 адреса и данных соответственно.

Блок 39 выполнения операций имеет вход 54 разрешения, выход 55 запроса, задающий вход 56, выход 57 разрешения, вход 58 запроса, первый выход 59 управления включением, выход О управления направлением передачи первый выход 61 запроса захвата,первый вход 62 разрешения захвата, входы-выходы 63-66 соответственно данных, адреса, выдачи и приема,второй вход 67 разрешения захвата, второй выход 68 запроса захвата,вход 69 сигнала Заполнен, вход 70 сигнала Пуст, выход 71 считывания, выход 72 записи, буферные входы 73 и 74 адреса и данных соответственно, второй выход 75 управления включением.

Блок 40 буферной памяти имеет вход 76 адреса, выход 77 приема и вход 78 данных.

Блок 5 выбора кэналов содержит (фиг.З) приемопередатчики 79 и 80 и селектор 81 каналов.

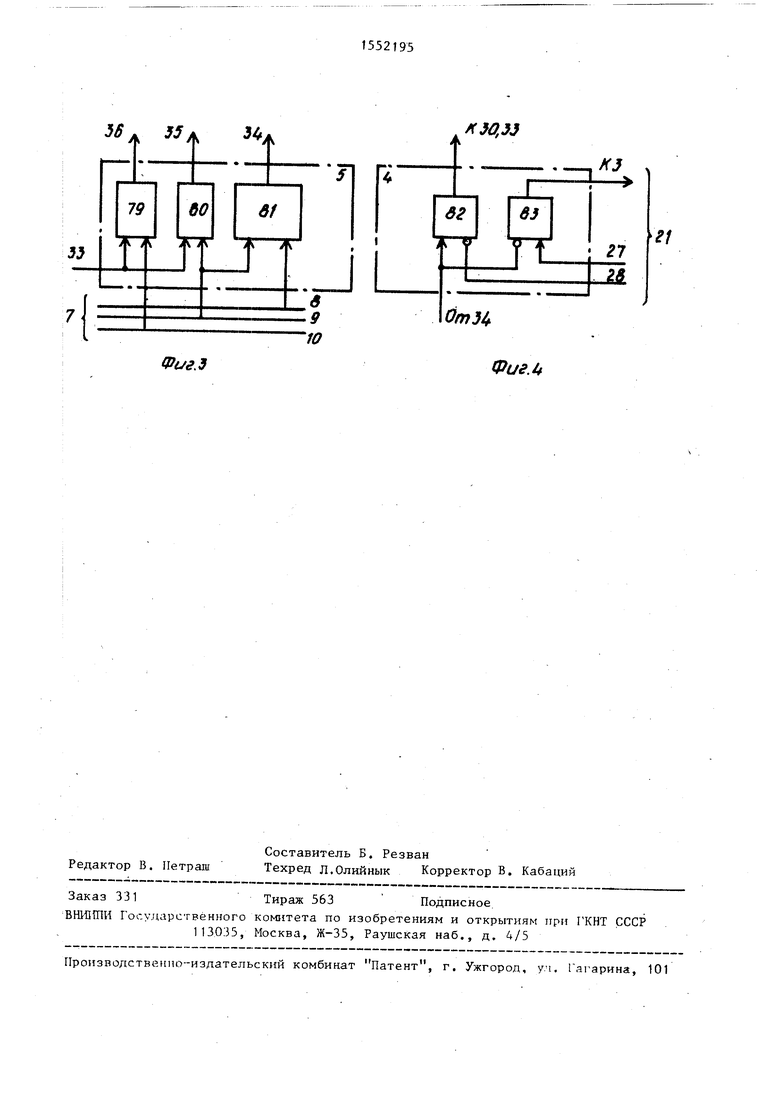

Блок 4 захвата магистрали содержит (фиг.4) два элемента 1И 82 и 83. Этот блок обеспечивает блоку 5 выбора каналов наивысший приоритет доступа к локальной магистрали 21 блока 2 обработки по отношению к процессорам 3 этого блока обработки.

Система работает следующим образом,

Б системе в качестве заявок могут ,быть использованы идентифицированные выборки параметров, последовательно поступающие в блок 1 памяти от многоканальных систем сбора информации. При этом каждая заявка представляет собой совокупность номера (адреса) измерительного канала и выборки (значения параметра) по этому каналу,что выражается параллельными 16-разрядными двоичными кодами. Номер канала используется в процессоре в качестве начального адреса программы обработки выборки.

Свойство адаптивности предлагаемой системы состоит в том, что в ней в зависимости от свойств входного потока и алгоритмов обработки выборок могут быть организованы различные режимы работы, что позволяет организовать наиболее эффективную работу

системы в каждом конкретном применении.

В зависимости от значения сигнало на шинах задания режима работы магистрали 11 всякий блок обработки може работать в одном из двух режимов: в режиме параллельной обработки (применяется для обработки взаимонезависимых потоков заявок по независимым алгоритмам) или в режиме последовательной обработки (применяется для обработки потоков заявок по зависимым алгоритмам), причем в этом режиме работы целесообразно выделить два случая: обработка взаимонезависимых потоков заявок и обработка взаимозависимых потоков заявок.

При описании работы системы пред- полагается, что все каналы разбиты предварительно на группы по числу блков обработки, причем номера каналов одной группы используются как адреса по которым в соответствующих селекторах 81 каналов записаны 1, а по остальным адресам селекторов каналов записаны О.

При описании работы системы удобно выделить процесс приема заявок из блока 1 памяти заявок в блоки 2 обработки, который происходит асин-. хронно с процессом собственно обработки заявок.

Прием заявок на обработку.

Для приема заявок на обработку каждый блок обработки, который не загружен полностью, выставляет на выходе 32 запроса сигнал запроса,, Запросы от блоков обработки по шине 6 запроса поступают на вход запроса блока 1 памяти. При наличии заявок и сигнала запроса на соответствующем входе блока 1 памяти последний выставляет на шинах адреса 9 и данных 10 коды номера канала и выборки очередной заявки и выдает по шине 8 сигнал разрешения. Под действием сигнала разрешения, поступающего с выход а блока 1 памяти на синхровходы блоков 5 выбора каналов, на выходе 34 одного из блоков 5 будет установлен единичный сигнал разрешения, который поступает на вход блока 4 захвата магистрали блока 2 обработки. При этом цепь действия сигналов запроса от процессоров прерывается, так как на выходе элемента И 83 нулевой сигнал. Таким образом, на время действия сигнала разрешения по связи

5

0

5

0

5

0

5

0

5

34 ни один из процессоров не может .. осуществлять захват локальной маги- страли.

Если на шине 28 отсутствует сигнал занятости, то сигнал разрешения проходит через элемент И 82. Если сигнал разрешения по связи 34 поступает в момент, когда локальная магистраль уже занята (на шине 28 - единичный сигнал), то поскольку длительность сигнала разрешения превышает длительность цикла локальной магист-4 рали,в момент снятия сигнала занятости в конце этого цикла сигнал разрешения/ проходит на выход элемента И 82. С выхода элемента И 82 сигнал поступает на вход разрешения первого процессора рассматриваемого блока обработки и одновременно по связи 33 поступает на стробирующие входы приемопередатчиков 79 и 80 соответствующего блока выбора каналов. В результате этого информация с шин 9 и 10 через приемопередатчики 80 и 79 по связям 35 и 36 подается соответственно на шины 23 и 22 локальной магистрали блока 2 обработки.

Цепь распространения сигнала разрешения, поступающего на вход разрешения первого процессора 3 блока 2 обработки, устроена таким образом, что этот сигнал проходит на вход 72 записи блока 40 буферной памяти и разрешает запись данных в соответствующий блок с шин 22 и 23 локальной -магистрали. По окончании действия сигнала разрешения локальная магистраль освобождается. Таким образом, процесс приема заявок на обработку совмещен в общем случае с процессом обработки заявок (независимо от режима работы блоков обработки) .

Работа блока обработки в режиме параллельной обработки заявок.

В этом режиме на один блок обработки назначаются каналы, характеризующиеся обработкой выборок по независимым алгоритмам. Исходное состояние блока 2 обработки: все процессоры 3 свободны, блок 40 буферной памяти пуст (т„е. значение сигнала на выходе 70 равно,1, а на выходе 69 - О), значение сигнала на входе „ 20 задания режима работы равно 1. В этом случае каждый процессор выдает сигнал запроса с выхода 32. Сигнал разрешения, поступающий из блока 4

захвата магистрали на вход первого Процессора блока обработки, проходит Последовательно через все процессоры И производит запись очередной заявки В блок 40 буферной памяти последнего Процессора, выставившего запрос. При появлении в блоке 40 буферной памяти котя бы одной заявки сигнал на выхо- )це 70 Пуст становится равным Поэтому сигнал опроса по связи 71 ПРОИЗВОДИТ считывание очередной заяв- и из блока 40 буферной памяти, и блок 39 выполнения операций включает- ря в работу. Если блок 40 буферной памяти пуст, то свободный процессор при отсутствии запросов от последую- цих процессоров производит прием заявки с шин 22 и 23 локальной магистрали по сигналу разрешения; по но- черу канала, считанному в блок 39, эпределяется программа обработки заявки (номер первой выполняемой команды). Если блок 40 буферной па- Йяти заполнен, то сигнал на выходе Ь9 этого блока равен |, а на выходе 70 - О. В этом случае по окончании обработки заявки формируется сигнал запроса, не дожидаясь окончания цикла считывания из блока 40.

Таким образом, в рассматриваемом случае осуществляется опережение запроса на подкачку блока буферной ламяти (на один цикл считывания). (Так как длительность обработки заявок В общем случае является величиной Произвольной (случайной), то произвольна также последовательность включения процессоров 3 в работу по мере Их освобождения. Тем самым обеспечивается непрерывность работы всех Процессоров и отсутствие простоев в fix работе при условии непрерывной (загрузки.- Результаты обработки заявок выдаются процессором 3 через системную магистраль 11 на выход системы.

Работа блока обработки в режиме Последовательной обработки.

А. Обработка взаимонезависимых потоков.

В этом режиме на один блок обработки назначаются каналы, которые Карактеризуются обработкой выборок по зависимым алгоритмам При этом Каждая заявка последовательно обслуживается в каждом процессоре блока обработки по частям, начиная с первого процессора этого блока. Исход15521958

ное состояние блока 2 обработки: все процессоры 3 свободны, блок 40 буферной памяти пуст (т.е. значение сигна- с ла на выходе 70 равно 1, а на выходе 69 - 0)} значение сигнала на входе 20 задания режима равно О. В этом режиме сигнал запроса на выходе каждого процессора 3 формируется

10 так же, как и в параллельном режиме. Запросы на выходе 32 блока обработки в последовательном режиме формируются только от первого процессора 3 этого блока обработки. Появление

15 сигнала разрешения на входе ра реше- ния первого процессора инициирует запись заявки по связи 72 в блок 40 буферной памяти первого процессора 3 блока 2 обработки. Если блок буфер20 ной памяти первого процессора пуст

в момент появления сигнала разрешения, то инициируется прием заявки с шин 22 и 23 в первый процессор и ее обработка в нем. Если блок 40 не пуст,

25 то первый процессор при его освобождении принимает очередную заявку, которую начинает обрабатывать по соответствующему алгоритму частичной обработки. Первый процессеD 3 блока 2

30 обработки, выполнив первую часть алгоритма обработки заявки, выдает сигнал резрешения на вход второго процессора. По этому сигналу во втором процессоре происходят такие же действия, что и в первом процессоре. При этом в блоке 39 второго процессора выполняются вторые части алгоритмов обработки заявок. Аналогичным образом происходит работа остальных процессоров 3 блока обработки 2 в последовательном режиме. Результаты окончательной обработки заявок выдаются процессором на выход системы через системную магистраль 11.

45 Б. Обработка взаимозависимых потоков.

35

40

50

55

В этом случае в блоках 2 обработки организуются режимы последовательной обработки заявок (путем установки на шинах задания режима магистрали 19 соответствующих сигналов) аналогично случаю А. Однако в отличие от описанного случая А в связи с наличием информационной зависимости между обрабатываемыми потоками может возникнуть (запрограммированная) потребность в передаче-приеме результатов обработки от процессоров одних

В этом случае в блоках 2 обработки организуются режимы последовательной обработки заявок (путем установки на шинах задания режима магистрали 19 соответствующих сигналов) аналогично случаю А. Однако в отличие от описанного случая А в связи с наличием информационной зависимости между обрабатываемыми потоками может возникнуть (запрограммированная) потребность в передаче-приеме результатов обработки от процессоров одних

блоков обработки к процессорам других блоков обработки. Для передачи результатов обработки от процессора 3 одного блока 2 обработки процессору 3, находящемуся в другом блоке обработки, предусмотрена команда, по которой формируется требование на подключение системной магистрали 11. Эта магистраль подключается в том случае, если нет сигнала занятости на шине 12. О захвате магистрали 11 блок 41 сообщает блоку 39 выполнения операций передающего процессора 3 сигналом по связи 62. При этом блок 41 передающего процессора сразу выставляет сигнал занятости на шине 12 системной магистрали 11, препятствуя доступу к этой магистрали остальным процессорам системы.

После того, как системная магистраль 11 захвачена, активизируется сигнал 59 на подключение системной магистрали 11 к информационным выходам 63-66 блока 39 через приемопередатчик 42. После этого передающий процессор 3 выставляет адрес процессора-абонента и передаваемые данные соответственно на шинах 17 и 18. Независимо от состояния процессора- абонента передаваемый адрес дешифрируется в дешифраторе 37, и последний выдает сигнал записи в блок 38 буферной памяти по связи 45, В резултате адрес и данные с шин 17 и 18 записываются в блок 38, который сигналом подтверждения записи по связи 46 через шину 15 освобождает доступ к системной магистрали другим процессорам. На этом процесс передачи данных по системной магистрали заканчивается.

Прием данных в блок 38 буферной памяти может осуществляться до тех пор, пока не произойдет заполнение блока 38. В такой ситуации сигнал Заполнен по связи 47 поступает на шину 12 занятости системной магистрали, запрещая передачу данных по этой магистрали. Получение данных по результатам обработки зависимых потоков происходит в процессорах из блоков 38 буферной памяти. Считывание данных из блока 38 в блок 39 выполнения операций происходит при выполнении соответствующей команды, активизирующей сигнал считывания по связи 51. Результаты окончательной обработки заявок выдаются процессора0

5

0

5

0

5

0

5

0

5

ми так же, как и в других режимах, на выход системы через системную магистраль 1 1«

Режимы работы блоков обработки устанавливаются от тшешних устройств путем установки соответствующих сигналов на шинах 20 магистрали 19 задания режима работы системы. Таким образом, в системе может быть организовано несколько различных режимов обработки, что позволяет системе эффективно адаптироваться к входным потокам разной структуры.

Формула изобретения

1. Адаптивная система обработки данных, содержащая блок памяти заявок, N блоков выбора каналов и N блоков обработки, каждый из которых содержит первый и второй процессоры и блок захвата магистрали, причем выходы разрешения, адреса и данных блока памяти через одноименные шины входной магистрали подключены к входам разрешения, адреса и данных всех блоков выбора каналов, выход разрешения i-го (...N) блока выбора каналов подключен к одноименному входу блока захвата магистрали 1-го блока обработки, выход строба блока зах,- вата магистрали 1-го блока обработки подключен к одноименному входу первого процессора 1-го блока обработки и к входу строба 1-го блока выбора канала, выходы адреса и данных которого через одноименные шины локальной магистрали подключены к входам адреса и данных первого и второго процессоров 1-го блока обработки, в каждом блоке обработки выход Разрешение первого процессора подключен к одноименному входу второго процессора, выход Запрос второго процессора подключен к входу Запрос первого процессора, выход Запрос первого процессора через входную шину подключен к входу Запрос блока памяти заявок, входы-выходы данных, адреса, сигналов выдачи, сигналов приема первого процессора через одноименные шины локальной магистрали подключены к одноименным входам-выходам второго процессора, выход Захват блока захвата магистрали подключен к - одноименному входу первого процессора, выход Ответ которого подключен к входу Захват второго процессора, выход Запрос и вход-выход занятости первого и второго процесг соров через одноименные шины локальной магистрали подключены к входам Запрос и Занято соответственно блока захвата магистрали входы задан режима первого и второго процессоров являются одноименными входами системы, отличающаяся тем, что, с целью увеличения пропускной способности системы за счет повышени степени распараллеливания процесса обработки потока взаимозависимых заявок, входы-выходы занятости, при- ема, выдачи, адреса и данных каждого из процессоров всех блоков обработки через одноименные шины системной магистрали соединены между собой, выход Запрос каждого из процессоров всех блоков обработки через одноимен ную шину системной магистрали подключен к входу Захват первого процессора первого блока обработки, в каждом блоке обработки выход ответ Первого процессора подключен к входу сигнала Захват второго процессора, выход Ответ второго процессора 1-г блока обработки подключен к входу Запрос первого процессора 1-го блока обработки.

2. Система поп.1,отличаю- ц а я с я тем, что процессор со- ержит первый и второй блоки буферной памяти, первый и второй при- Ёмопередатчики, первый и второй бло- Ки обмена,, дешифратор адреса и блок выполнения операций, входы Разре- йение, Запрос, Задание режима И выходы Разрешение и Запрос Которого являются соответственно Одноименными входами и выходами процессора, выходы Пуст, Адрес, Данные первого блока буферной памяти подключены соответственно к фдноименным первым входам блока выполнения операции, первый выход Считывание которого подключен к Одноименному входу первого блока буферной памяти, выход Подтверждение лаписи которого подключен к одноименным входам первого блока обмена И первого приемопередатчика и является первым выходом приема процессора, выход Заполнен первого-блока буферной памяти подключен к одноименному входу первого блока обмена и Является первым выходом занятости Процессора, первые информационные

входы-выходы первого приемопередатчика соединены с одноименными входами первого блока буферной памяти и являются первыми входами-выходами адреса и данных процессора, первый вход-выход выдачи процессора является одноименным входом-выходом первого приемопередатчика, вход Захват, выход Ответ и выход Запрос первого блока обмена являются одноименными первыми входами и выходами процессора, выход Разрешение захвата первого блока обмена подключен к одноименному первому входу блока выполнения операций, первый выход запроса захвата которого подключен к одноименному входу первого блока обмена, первый выход Управление включением блока выполнения операций подключен к одноименному входу первого приемопередатчика, информационные входы-выходы, входы-выходы выдачи и приема которого подключены соответственно к одноименным входам-выходам второго приемопередатчика и входам-выходам блока выполнения операций, выход управления направлением передачи которого подключен к одноименным входам первого и второго приемопередатчиков, вход Управление включением которого подключен к одноименному второму выходу блока выполнения операций,

второй выход запроса захвата которо- i го подключен к одноименному входу

второго блока обмена, выход Разрешение захвата которого подключен к одноименному второму входу блока выполнения операций, вторые выходы считывания и записи которого подключены к одноименным входам второго блока буферной памяти, выход Заполнен, Пуст Адрес и Данные которого подключены к одноименным вторым входам блока выполнения опе- |раций соответственно, входы-выходы адреса и данных второго приемопередатчика подключены к одноименным входам второго блока буферной памяти

и являются одноименными вторыми вхоi

..дами-выходами процессора, вход-выход выдачи второго приемопередатчика является одноименным вторым входом выходом процессора, вход-выход прием второго приемопередатчика соединен с одноименными выходом второго блока буферной памяти, входом второго блок

13

обмена и является вторым входом-выходом приема процессора, вход Захват, выходы Ответ, Запрос и за1552195U

нятости второго блока обмена являются одноименными вторыми входом и выходами процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах на основе мультипроцессорных вычислительных систем. Цель изобретения - увеличение пропускной способности системы за счет повышения степени распараллеливания процесса обработки потока взаимозависимых заявок. Для этого в систему, содержащую блок памяти заявок 1, N блоков 2 обработки, каждый из которых содержит процессоры 3 и блок 4 захвата магистрали и N блоков выбора канала, дополнительно введена магистраль адреса /данных/ управления, обеспечивающая связь между всеми процессорами системы. 1 з.п. ф-лы, 4 ил.

го

/6 /7 Г6 15 Г4 & 0 12

Фиг. В

2f

36 А 35

г1

34

7Р

60

3/

W

yv Л

t Л м

,J

в

.9

Ю

ФигЗ

XJQJJ

КЗ ,

-

дг

вз

п

3

ОтЫ

Фиг.

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

Авторы

Даты

1990-03-23—Публикация

1988-05-05—Подача